## Description

The µPD8257 is a programmable four-channel direct memory access (DMA) controller. It is designed to simplify high-speed transfers between peripheral devices and memories. Upon a peripheral request, the μPD8257 generates a sequential memory address, thus allowing the peripheral to read or write data directly to or from memory. Peripheral requests are prioritized within the µPD8257 so that the system bus may be acquired by the generation of a single HOLD command to the 8080A. DMA cycle counts are maintained for each of the four channels, and a control signal notifies the peripheral when the preprogrammed member of DMA cycles has occurred. Output control signals are also provided which allow simplified sectored data transfers and expansion to other µPD8257 devices for systems requiring more than four DMA channels.

### **Features**

- ☐ Four-channel DMA controller

- ☐ Priority DMA request logic

- ☐ Channel inhibit logic

- ☐ Terminal count and modulo 128 outputs

- ☐ Automatic load mode☐ Single TTL clock

- □ Single  $+5 \text{ V} \pm 10\%$  power supply

- ☐ Expandable

- ☐ Available in extended temperature range

### **Ordering Information**

| Part<br>Number | Package Type       | Max Frequency<br>of Operation |  |  |

|----------------|--------------------|-------------------------------|--|--|

| μPD8257C-2     | 40-pin plastic DIP | 5 MHz                         |  |  |

| μPD8257C-5     | 40-pin plastic DIP | 3 MHz                         |  |  |

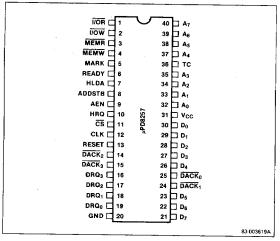

### Pin Configuration

### Pin Identification

| No.               | Symbol                                                                           | Function                            |

|-------------------|----------------------------------------------------------------------------------|-------------------------------------|

| 1                 | I/OR                                                                             | I/O read, control signal            |

| 2 .               | Ī/OW                                                                             | I/O write, control signal           |

| 3                 | MEMR                                                                             | Memory read output                  |

| 4                 | MEMW                                                                             | Memory write output                 |

| 5                 | MARK                                                                             | Modulo 128 mark                     |

| 6                 | READY                                                                            | Ready input                         |

| 7                 | HLDA                                                                             | Hold acknowledge input (from 8080A) |

| 8                 | ADDSTB                                                                           | Address strobe output               |

| 9                 | AEN                                                                              | Address enable output               |

| 10                | HRQ                                                                              | Hold request (to 8080A)             |

| 11                | <del>C</del> S                                                                   | Chip select input                   |

| 12                | CLK                                                                              | Clock input                         |

| 13                | RESET                                                                            | Reset input                         |

| 14, 15,<br>24, 25 | DACK <sub>2</sub> , DACK <sub>3</sub> ,<br>DACK <sub>1</sub> , DACK <sub>0</sub> | DMA acknowledge output              |

| 16-19             | DRQ3-DRQ0                                                                        | DMA request input                   |

| 20                | GND                                                                              | Ground                              |

| 21-23, 26-30      | D <sub>7</sub> -D <sub>5</sub> ,<br>D <sub>4</sub> -D <sub>0</sub>               | I/O data bus                        |

| 31                | V <sub>CC</sub>                                                                  | +5 V power supply                   |

| 32-35             | A <sub>0</sub> -A <sub>3</sub>                                                   | I/O address bus                     |

| 36                | TC                                                                               | Terminal count output               |

| 37-40             | A <sub>4</sub> -A <sub>7</sub>                                                   | Output address bus                  |

#### Pin Functions

## D<sub>0</sub>-D<sub>7</sub> (I/O Data Bus)

During an I/O read, the CPU enables these lines as inputs, allowing it to read an address register, a word count register, or the status or temporary register. During an I/O write, these lines are enabled as outputs, allowing the CPU to program the µPD8257-2/-5 control registers. During DMA cycles, the eight MSBs of the address are output to the data bus to be strobed to an external latch via ADDSTB.

# A<sub>4</sub>-A<sub>7</sub> (Output Address Bus)

These lines, active only during DMA service, are outputs that provide the four MSBs of the address.

### A<sub>0</sub>-A<sub>3</sub> (I/O Address Bus)

During DMA active states, these lines are outputs that provide the 4 LSBs of the output address bus. During DMA idle states, these lines are inputs, allowing the CPU to load or examine control registers.

# DRQ<sub>0</sub>-DRQ<sub>3</sub> (DMA Request Input)

These are asynchronous channel request inputs used by peripherals to request DMA service. In a fixed priority scheme,  $DRQ_0$  has the highest priority and  $DRQ_3$  has the lowest. The polarity of these lines is programmable; however, reset initializes them to active high.

# **HLDA (Hold Acknowledge)**

Indicates that the CPU has relinquished control of the system busses.

### HRQ (Hold Request)

Requests control of the system bus. The  $\mu$ PD8257-2/-5 issues this signal in response to software requests or DRQ inputs from peripherals.

# DACK<sub>0</sub>-DACK<sub>3</sub> (DMA Acknowledge Output)

These lines indicate an active channel. They are sometimes used to select a peripheral. Only one DACK may be active at any time. All DACK lines are inactive unless DMA has control of the bus. The polarity of these lines is programmable; however, reset initializes them to active low.

### TC (Terminal Count)

When the terminal count occurs, TC goes high, informing the CPU that the data transfer is complete.

### RESET

Clears the command, status, request, and temporary registers, the first/last flip flop, and sets the mask register. The  $\mu$ PD8257-2i-5 is in idle state after a reset.

### CS (Chip Select)

The CPU uses  $\overline{CS}$  to select the  $\mu$ PD8257-2/-5 as an I/O device during an I/O read or write by the CPU. This provides CPU communication on the data bus.  $\overline{CS}$  may be held low during multiple transfers to or from the  $\mu$ PD8257-2/-5 as long as  $\overline{I/OR}$  or  $\overline{I/OW}$  is toggled following each transfer.

#### READY

This signal can extend memory read and write pulses for slow memories or I/O peripherals.

### CLK (Clock)

Controls internal operations and data transfer rate.

### AEN (Address Enable)

This signal allows the external latch to output the upper address byte by disabling the system bus during DMA cycles. Use HLDA and AEN to deselect I/O peripherals that may be erroneously accessed during DMA transfers. The µPD8257-2/-5 deselects itself during DMA transfers.

### ADDSTB (Address Strobe)

This signal strobes the upper address byte form  $D_0$ - $D_7$  into an external latch.

### **MEMR** (Memory Read)

This signal accesses data from a specified memory location during memory-to-peripheral or memory-to-memory transfers.

### **MEMW** (Memory Write)

This signal writes data to a specified memory location during peripheral-to-memory or memory-to-memory transfers.

### I/OR (I/O Read)

In the idle state, this signal is an input control line used by the CPU to read control registers. In the active state, the  $\mu$ PD8257-2/-5 uses I/OR as an output control signal to access data from a peripheral during a DMA write.

# I/OW (I/O Write)

In the idle state, the CPU uses I/OW as an input control signal to load information to the  $\mu$ PD8257-2/-5. In the active state, the  $\mu$ PD8257-2/-5 uses I/OW as an output control signal to load data to a peripheral during a DMA read.

The rising edge of  $\overline{\text{WR}}$  must follow each data byte transfer in order for the CPU to write to the  $\mu\text{PD8257-2/-5}$ . Holding I/OW low while toggling CS does not produce the same effect.

# MARK (Modulo 128 Mark)

This output notifies the selected peripheral that the current DMA cycle is the 128th cycle since the previous MARK output. MARK always occurs at 128 (and all multiples of 128) cycles from the end of the data block.

# $V_{CC}$

Power supply.

### **GND**

Ground.

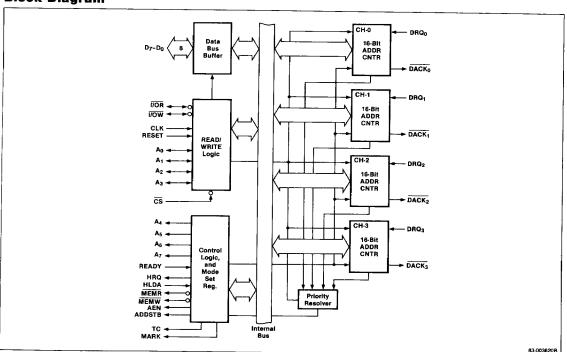

### **Block Diagram**

### **Absolute Maximum Ratings**

$T_A = 25^{\circ}C$

| Operating temperature, T <sub>OPT</sub> | 0°C to 70°C        |

|-----------------------------------------|--------------------|

| Storage temperature, T <sub>STG</sub>   | -65°C to +150°C    |

| Power supply voltage, V <sub>CC</sub>   | -0.5 V to +7 V (1) |

| Power dissipation                       | 1 Watt             |

Comment: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Note:

(1) With respect to Ground

### **DC Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = +5 \text{ V } \pm 10\% \text{ GND} = 0 \text{ V}$

|                                |                 | Lin  | nits                     |      | Test                                                                                 |  |  |

|--------------------------------|-----------------|------|--------------------------|------|--------------------------------------------------------------------------------------|--|--|

| Parameter                      | Symbol          | Min  | Max                      | Unit | Conditions                                                                           |  |  |

| Input low voltage              | VIL             | -0.5 | 0.8                      | ٧    |                                                                                      |  |  |

| Input high voltage             | V <sub>IH</sub> | 2.0  | V <sub>CC</sub><br>+ 0.5 | ٧    |                                                                                      |  |  |

| Output low voltage             | VOL             |      | 0.45                     | ٧    | $l_{0L} = 1.6 \text{ mA}$                                                            |  |  |

| Output high<br>voltage         | V <sub>OH</sub> | 2.4  | V <sub>CC</sub>          | ٧    | $I_{OH} = -150 \mu A$<br>for AB,<br>DB and AEN<br>$I_{OH} = -80 \mu A$ for<br>others |  |  |

| HRQ output high voltage        | V <sub>HH</sub> | 3.3  | v <sub>cc</sub>          | ٧    | $I_{0H} = -80  \mu A$                                                                |  |  |

| Power supply                   | Icc             |      | 100                      | mA   | 8257-2                                                                               |  |  |

| current                        |                 | _    | 120                      | mA   | 8257-5                                                                               |  |  |

| Input leakage                  | IIL             | -10  | 10                       | μΑ   | $0 \le V_{IN} \le V_{CC}$                                                            |  |  |

| Output leakage<br>during float | OFL             | -10  | 10                       | μΑ   | 0.45 ≤ V <sub>OUT</sub><br>≤V <sub>CC</sub>                                          |  |  |

### Capacitance

$T_A = 25^{\circ}C; V_{CC} = GND = 0 V$

|                   |                  |     | Limits |     |      | Test                               |  |  |

|-------------------|------------------|-----|--------|-----|------|------------------------------------|--|--|

| Parameter         | Symbol           | Min | Тур    | Max | Unit | Conditions                         |  |  |

| Input capacitance | Cı               |     |        | 10  | pF   | f <sub>c</sub> = 1 MHz             |  |  |

| I/O capacitance   | C <sub>1/0</sub> |     |        | 20  | pF   | Unmeasured pins<br>returned to GND |  |  |

### **AC Characteristics**

$T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5 \text{ V } \pm 10\%; \text{ GND } = 0 \text{ V}$

| Parameter                           |                                 |                   | Lh  | mits               |     |                 |                         |

|-------------------------------------|---------------------------------|-------------------|-----|--------------------|-----|-----------------|-------------------------|

|                                     |                                 | μ <b>PD8257-2</b> |     | μ <b>PD8257-</b> 5 |     |                 |                         |

|                                     | Symbol                          | Min               | Max | Min                | Max | Unit            | Test<br>Conditions      |

| Read                                |                                 |                   |     |                    |     |                 |                         |

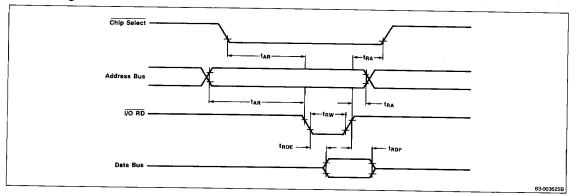

| ADR or CS↓ Setup to RD↓             | t <sub>AR</sub>                 | 0                 |     |                    |     | ns              |                         |

| ADR or CS → hold from RDt           | † <sub>RA</sub>                 | 0                 |     |                    |     | ns              |                         |

| Data Access from RD↓                | t <sub>RDE</sub>                | 0                 | 140 | 0                  | 170 | ns              | $C_L = 100 \text{ pF}$  |

| DB → float delay from RDt           | t <sub>RDF</sub>                | 10                | 85  | 20                 | 100 | ns              | C <sub>L</sub> = 100 pF |

| RD width                            | t <sub>RW</sub>                 | 200               |     | 250                |     | ns              | о 100 рі                |

| Write                               |                                 |                   |     |                    |     |                 |                         |

| ADR setup to WR↓                    | t <sub>AW</sub>                 | 20                |     | <del></del> -      |     | ns              |                         |

| ADR hold from WRt                   | t <sub>WA</sub>                 | 0                 |     |                    |     | ns              |                         |

| Data setup to WR↓                   | t <sub>DW</sub>                 | 100               |     | 200                |     | ns              |                         |

| Data hold from WRt                  | t <sub>WD</sub>                 | 0                 |     |                    |     | ns              |                         |

| WR width                            | twws                            | 100               |     | 200                |     | ns              |                         |

| Other timing                        | -                               |                   |     |                    |     |                 |                         |

| Reset pulse width                   | trstw                           | 300               |     | 300                |     | ns              |                         |

| Power supply f(VCC) setup to reset+ | trstd                           | 500               |     | 500                |     | μS              |                         |

| Signal rise & fall times            | t <sub>r</sub> , t <sub>f</sub> |                   | 20  |                    | 20  | F               |                         |

| Reset to first IOWR                 | trsts                           | 2                 |     | 2                  |     | t <sub>CY</sub> |                         |

#### Note:

(1) All timing measurements are made at the following reference voltages unless specified otherwise: input "1" at 2.0 V, "0" at 0.8 V, output "1" at 2.0 V, "0" at 0.8 V.

### **AC Characteristics**

$T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = +5 \text{ V } \pm 10\%; \text{ GND } = 0 \text{ V}$

|                                                                 |                   |                       | Lim | its                   |                   |      |                    |

|-----------------------------------------------------------------|-------------------|-----------------------|-----|-----------------------|-------------------|------|--------------------|

|                                                                 |                   | μPD8257               | 7-2 | μPD825                | 7-5               |      |                    |

| Parameter                                                       | Symbol            | Min                   | Max | Min                   | Max               | Unit | Test<br>Conditions |

| Cycle time (period)                                             | t <sub>CY</sub>   | 0.200                 | 4   | 0.320                 | 4                 | μS   |                    |

| Clock active (high)                                             | tθ                | 80                    | _   | 80                    | .8t <sub>CY</sub> | ns   |                    |

| DRQ↑ setup to 04 (SI, S4)                                       | tos               | 50                    |     | 120                   |                   |      |                    |

| DRQ↓ hold from HLDA↑                                            | t <sub>QH</sub>   | 0                     |     | 0                     |                   |      | (4)                |

| HRQ↑ or ↓ delay from <i>θ</i> ↑ (SI, S4)<br>(measured at 2.0 V) | t <sub>DQ</sub>   |                       | 160 |                       | 160               | ns   |                    |

| HRQ↑ or ↓delay from 0↑ (SI, S4)                                 | t <sub>HS</sub>   | 1                     | 200 | 100                   | 250               | ns   | (3)                |

| HLDA† or √setup to θ√ (SI, S4)                                  | t <sub>HS</sub>   | 50                    |     | 100                   |                   | ns   | (5)                |

| AEN↑ delay from θ↓ (S1)                                         | t <sub>AEL</sub>  |                       | 150 |                       | 300               | ns   |                    |

| AEN↓ delay from 0↑ (SI)                                         | t <sub>AET</sub>  |                       | 150 |                       | 200               | ns   |                    |

| ADR (AB) (active) delay from AEN1 (S1)                          | t <sub>AEA</sub>  | 20                    | *** | 20                    |                   | ns   | (4)                |

| ADR (AB) (active) delay from 61 (S1)                            | t <sub>FAAB</sub> |                       | 200 |                       | 250               | ns   | (2)                |

| ADR (AB) (float) delay from $\theta$ 1 (SI)                     | t <sub>AFAB</sub> |                       | 150 |                       | 150               | ns   | (2)                |

| ADR (AB) (stable) delay from 61 (S1)                            | tasm              |                       | 200 |                       | 250               | пѕ   | (2)                |

| ADR (AB) (stable) hold from $\theta\uparrow$ (S1)               | t <sub>AH</sub>   | t <sub>ASM</sub> - 50 |     | t <sub>ASM</sub> - 50 |                   |      | (2)                |

| ADR (AB) (valid) hold from RDt (S2, SI)                         | t <sub>AHR</sub>  | 60                    |     | 60                    |                   | ns   | (4)                |

# **AC Characteristics (cont)**

|                                                                                                                          |                   |                                       | Limit | 18                                       |     |      | Test       |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|-------|------------------------------------------|-----|------|------------|

| Parameter                                                                                                                |                   | μ <b>PD8257</b>                       | -2    | μ <b>PD8257</b>                          | -5  |      |            |

|                                                                                                                          | Symbol            | Min                                   | Max   | Min                                      | Max | Unit | Conditions |

| ADR (AB) (valid) hold from WRt (S1, SI)                                                                                  | t <sub>AHW</sub>  | 100                                   |       | 300                                      |     | ns   | (4)        |

| ADR (DB) (active) delay from 6t (S1)                                                                                     | †FADB             |                                       | 150   |                                          | 300 | ns   | (2)        |

| ADR (DB) (float) delay from 01 (S2)                                                                                      | t <sub>AFDB</sub> | tstt                                  | 140   | t <sub>STT</sub> + 20                    | 170 | ns   | (2)        |

| ADR (DB) setup to ADR STB↓ (S1-S2)                                                                                       | t <sub>ASS</sub>  | 100                                   |       | 100                                      |     | ns   | (4)        |

| ADR (DB) (valid) hold from ADR STB4<br>(S2)                                                                              | t <sub>AHS</sub>  | 20                                    |       | 50                                       |     | ns   | (4)        |

| ADR STB† delay from 0† (S1)                                                                                              | t <sub>STL</sub>  |                                       | 150   |                                          | 200 | ns   |            |

| ADR STB+ delay from 0t (S2)                                                                                              | ts⊓               |                                       | 140   |                                          | 140 | ns   |            |

| ADR STB width (S1-S2)                                                                                                    | T <sub>SW</sub>   | t <sub>CY</sub> -100                  |       | t <sub>CY</sub> -100                     |     | ns   | (4)        |

| RD  → or WR (ext)  → delay from ADR  STB  → (S2)                                                                         | tasc              | 20                                    |       | 70                                       |     | ns   | (4)        |

| RDI or WR (ext) delay from ADR (DB) (float) (S2)                                                                         | t <sub>DBC</sub>  | 0                                     |       | 20                                       |     | ns   | (4)        |

| DACK† or +delay from $\theta$ + (S2, S1) and TC/Mark† delay from $\theta$ † (S3) and TC/Mark† delay from $\theta$ † (S4) | t <sub>AK</sub>   |                                       | 200   |                                          | 250 | ns   | (5)        |

| RD↓ or WR (ext) ↓ delay from 0↑ (S2) and WR↓ delay from 0↑ (S3)                                                          | t <sub>DCL</sub>  |                                       | 150   |                                          | 200 | ns   | (2) (6)    |

| RD↑ delay from 0↓ (S1, SI) and WR↑ delay from 0↑ (S4)                                                                    | t <sub>DCT</sub>  |                                       | 150   |                                          | 200 | ns   | (2) (7)    |

| RD or WR (active) from 61 (S1)                                                                                           | tFAC              |                                       | 200   |                                          | 300 | ns   | (2)        |

| RD or WR (float) from 01 (SI)                                                                                            | tAFC              |                                       | 150   |                                          | 150 | ns   | (2)        |

| RD width (S2-S1 or SI)                                                                                                   | T <sub>RWM</sub>  | 2t <sub>CY</sub> + t <sub>0</sub> -50 |       | 2t <sub>CY</sub> +<br>t <sub>θ</sub> –50 |     | ns   | (4)        |

| WR width (S3-S4)                                                                                                         | t <sub>wwm</sub>  | t <sub>CY</sub> -50                   |       | t <sub>CY</sub> - 50                     |     | กร   | (4)        |

| WR (ext) width (S2-S4)                                                                                                   | twwmE             | 2t <sub>CY</sub> - 50                 |       | 2t <sub>CY</sub> - 50                    |     | пѕ   | (4)        |

| READY set up time to 01 (S3, Sw)                                                                                         | t <sub>RS</sub>   | 30                                    |       | 30                                       |     | ns   |            |

| READY hold time from 6t (S3, Sw)                                                                                         | t <sub>RH</sub>   | 30                                    |       | 30                                       |     | ns   |            |

### Note:

- (1) Load = 1 TTL (2) Load = 50 pF (3) Load =  $V_{OH}$  = 3.3 V (4) Tracking specification (5)  $\triangle t_{TAK} \le 50$  ns (6)  $\triangle t_{DCL} \le 50$  ns (7)  $\triangle t_{DCT} \le 50$  ns

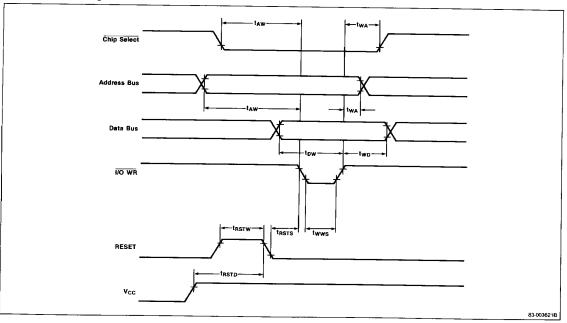

# **Timing Waveforms**

# Read Timing

# Write/Reset Timing

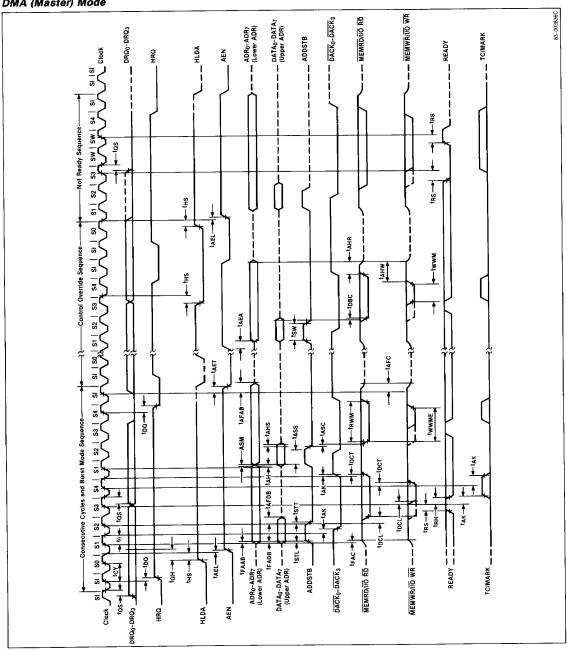

# Timing Waveforms (cont)

DMA (Master) Mode

8-86

## **Functional Description**

The  $\mu$ PD8257 is a programmable, direct memory Access (DMA) device. When used with an 8212 I/O port device, it provides a complete four-channel DMA controller for use in 8080A/8085A based systems. Once initialized by an 8080A/8085A CPU, the  $\mu$ PD8257 will block transfer up to 16,364 bytes of data between memory and a peripheral device without any attention from the CPU. It will do this on all 4-DMA channels. After receiving a DMA transfer request from a peripheral, the following sequence of events occurs within the  $\mu$ PD8257.

- It acquires control of the system bus (placing 8080A/8085A in hold mode).

- Resolves priority conflicts if multiple DMA requests are made.

- (3) A 16-bit memory address word is generated with the aid of an 8212 in the following manner:

- (a) The μPD8257 outputs the least significant eight bits (A<sub>0</sub>-A<sub>7</sub>) which go directly onto the address bus.

- (b) The μPD8257 outputs the most significant eight bits (A<sub>8</sub>-A<sub>15</sub>) onto the data bus where they are latched into an 8212 and then sent to the high order bits on the address bus.

- (4) The appropriate memory and I/O read/write control signals are generated allowing the peripheral to receive or deposit a data byte directly from or to the appropriate memory location.

Block transfer of data (e.g., a sector of data on a floppy disk) either to or from a peripheral may be accomplished as long as the peripheral maintains its DMA request (DRQ $_{\rm n}$ ). The  $_{\mu}$ PD8257 retains control of the system bus as long as DRQ $_{\rm n}$  remains high or until the terminal count (TC) is reached. When the terminal count occurs, TC goes high, informing the CPU that the operation is complete.

There are three different modes of operation:

- DMA read, which causes data to be transferred from memory to a peripheral;

- (2) DMA write, which causes data to be transferred from a peripheral to memory; and

- (3) DMA verify, which does not actually involve the transfer of data.

The DMA read and write modes are the normal operating conditions for the  $\mu\text{PD8257}.$  The DMA verify mode responds in the same manner as read/write except no memory or I/O read/write control signals are generated, thus preventing the transfer of data. The peripheral gains control of the system bus and obtains DMA acknowledgements for its requests, thus allowing it to access each byte of a data block for check purposes or accumulation of a CRC (cycle redundancy code) checkword. In some applications it is necessary for a block of DMA read or write cycles to be followed by a block of DMA verify cycles to allow the peripheral to verify its newly acquired data.

### **DMA Operation**

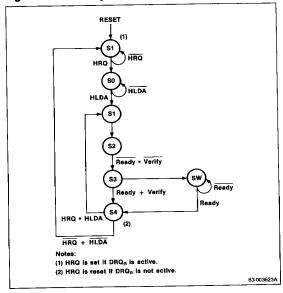

As shown in figure 1, internally the  $\mu$ PD8257 contains six different states (S0, S1, S2, S3, S4 and SW). The duration of each state is determined by the input clock. In the idle state, (S1), no DMA operation is being executed. A DMA cycle is started upon receipt of one or more DMA requests (DRQ<sub>n</sub>). Then the  $\mu$ PD8257 enters the S0 state, during which a hold request (HRQ) is sent to the 8080A/8085A and the  $\mu$ PD8257 waits in S0 until the 8080A/8085A issues a hold acknowledge (HLDA) back. During S0, DMA requests are sampled and DMA priority is resolved (based upon either the fixed or priority scheme).

After receipt of HLDA, the DMA acknowledge line  $(DACK_n)$  with the highest priority is driven low, selecting that particular peripheral for the DMA cycle. The DMA request line  $(DRQ_n)$  must remain high until either a DMA acknowledge  $(DACK_n)$  or both  $DACK_n$  and TC (terminal count) occur, indicating the end of a block or sector transfer (burst model).

Figure 1. DMA Operation State Diagram

The DMA cycle consists of four internal states; S1, S2, S3, and S4. If the access time of the memory or I/O device is not fast enough to return a ready command to the  $\mu$ PD8257 after it reaches state S3, then a wait state is initiated (SW). One or more than one wait state occurs until a ready signal is received, and the  $\mu$ PD8257 is allowed to go into state S4. Either the extended write option or the DMA verify mode may eliminate any wait state.

If the  $\mu$ PD8257 should lose control of the system bus, (i.e., HLDA goes low) then the current DMA cycle is completed; the device goes into the S1 state, and no more DMA cycles occur until the bus is reacquired. Ready setup time (t<sub>RS</sub>), write setup time (t<sub>DW</sub>), read data access time (t<sub>RD</sub>), and HLDA setup time (t<sub>OS</sub>) should all be carefully observed during the handshaking mode between the  $\mu$ PD8257 and the 8080A/8085A.

During DMA write cycles, the I/O Read (I/O R) output is generated at the beginning of state S2 and the memory write (MEMW) output is generated at the beginning of S3. During DMA read cycles, the memory read (MEMR) output is generated at the beginning of state S2 and the I/O write (I/O W) goes low at the beginning of state S3. No read or write control signals are generated during DMA verify cycles.

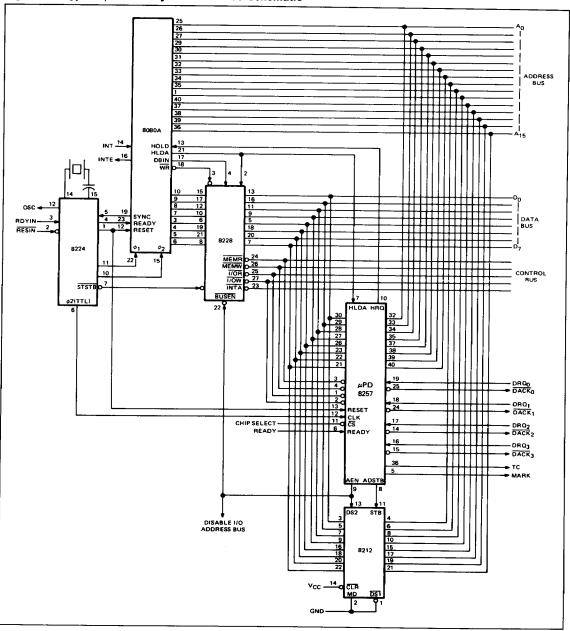

#### **System Interface**

Figure 2 is the schematic diagram of a  $\mu$ PD8257 system interface with the 8080A CPU, 8212 I/O Port, 8224 Clock Generator, and 8228 System Controller and Bus Driver.

Figure 2. Typical µPD8257 System Interface Schematic