#### **FEATURES**

- Generates all clock frequencies for VIA K7 chip sets requiring multiple CPU clocks and high speed SDRAM buffers.

- Support one pair of differential CPU clocks, one open-drain CPU, 6 PCI and 13 high-speed SDRAM buffers for 3-DIMM applications.

- One 24 48MHz clock and one 48MHz clock.

- Two14.318MHz reference clocks.

- Power management control to stop CPU, and Power down Mode from I2C programming.

- Support 2-wire I2C serial bus interface with builtin Vendor ID, Device ID and Revision ID.

- Single byte micro-step linear Frequency Programming via I2C with Glitch free smooth switching.

- Spread Spectrum ±0.25% center spread, 0 to -0.5% downspread.

- 50% duty cycle with low jitter.

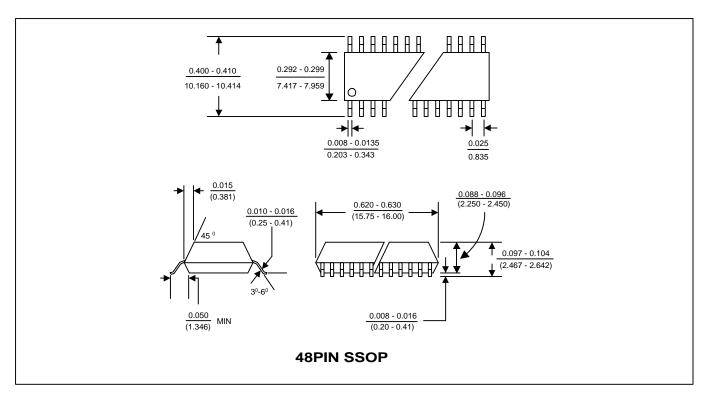

- Available in 300 mil 48 pin SSOP.

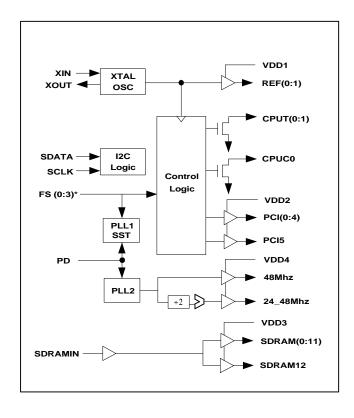

#### **BLOCK DIAGRAM**

#### PIN CONFIGURATION

Note: ^: Pull up, #: Active Low

\*: Bi-directional latched at power-up

#### I/O MODE CONFIGURATION

| MODE (Pin 7) | PIN 2    |

|--------------|----------|

| 1 (OUTPUT)   | REF0     |

| 0 (INPUT)    | CPU_STOP |

#### **POWER GROUP**

VDD0: PLL CORE

VDD1: REF(0:1), XIN, XOUT

VDD2: PCI(0:5)

VDD3: SDRAM(0:12)

VDD4: 48MHz, 24\_48MHz

#### **KEY SPECIFICATIONS**

CPU Cycle to Cycle jitter: 250ps.

PCI to PCI output skew: 500ps.

CPU to CPU output skew: ±175ps

• SDRAM to SDRAM output skew: 250ps.

• CPU to PCI skew (CPU leads): 0 ~ 3 ns.

### **PIN DESCRIPTIONS**

| Name                       | Number                                      | Туре | Description                                                                                                                                                                                       |

|----------------------------|---------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD0                       | 1                                           | Р    | Power supply for PLL CORE.                                                                                                                                                                        |

| VDD1                       | 6                                           | Р    | Power supply for REF0, REF1, and crystal oscillator.                                                                                                                                              |

| VDD2                       | 14                                          | Р    | Power supply for PCI (0:5).                                                                                                                                                                       |

| VDD3                       | 19,30,36,42                                 | Р    | Power supply for SDRAM (0:12).                                                                                                                                                                    |

| VDD4                       | 27                                          | Р    | Power supply for 24_48MHz and 48MHz.                                                                                                                                                              |

| GND                        | 3,9,16,22,<br>33,39,45,47                   | Р    | Ground.                                                                                                                                                                                           |

| XIN                        | 4                                           | I    | 14.318MHz crystal input that has internal loads cap (36pF) and feedback resistor from XOUT.                                                                                                       |

| XOUT                       | 5                                           | 0    | 14.318MHz crystal output. It has internal load cap (36pF).                                                                                                                                        |

| REF0//CPU_STOP             | 2                                           | В    | Multiplexed pin controlled by MODE signal. When CPU_STOP is low, it will halt CPUT (0:1), CPUC0 and SDRAM (0:11) outputs. In output mode, this pin will generate buffered reference clock output. |

| PCI5/MODE                  | 7                                           | В    | At power-up, MODE function will be activated. When MODE is Low, Pin 2 is input for CPU_STOP. When high, Pin 2 is output for REF0. After input data latched, this pin will generate PCI bus clock. |

| PCI0/FS3                   | 8                                           | В    | At power-up, this pin is input pin and will determine CPU clock frequency. After input sampling, this pin will generate output clocks. FS3 has internal pull up (high by default).                |

| PCI1/SEL24_48              | 10                                          | В    | At power-up, this pin will select 24MHz (when high) or 48MHz (when low) for pin25 output. After input sampling, this pin is PCI output. It has internal pull up resistor.                         |

| PCI(2:4)                   | 11,12,13                                    | 0    | PCI clock outputs.                                                                                                                                                                                |

| SDRAMIN                    | 15                                          | I    | Buffer input pin: The signal provided to this input pin is buffered to 13 SDRAM outputs.                                                                                                          |

| SDRAM(0:11)                | 17,18,20,21,28,<br>29,31,32,34,35,<br>37,38 | 0    | SDRAM clock outputs, Fan-out Buffer outputs from SDRAMIN pin.                                                                                                                                     |

| SDATA                      | 23                                          | В    | Social data inpute for carial interface part                                                                                                                                                      |

| SCLK                       | 24                                          |      | Serial data inputs for serial interface port.                                                                                                                                                     |

| 24_48MHz/FS1,<br>24MHz/FS0 | 25,26                                       | В    | At power-up, these pins are input pins and will determine the CPU clock frequency. FS0, FS1 have internal pull up (high by default).                                                              |

| SDRAM12                    | 40                                          | 0    | When CPU_STOP is low, this pin is still free running. When the power down is low, this SDRAM will be stopped.                                                                                     |

| PD#                        | 41                                          | Ī    | When low, it will stop all clock outputs. It has internal pull-up resistor.                                                                                                                       |

| CPUT(0:1)                  | 43,46                                       | 0    | "True" clocks of differential pair open-drain CPU outputs.                                                                                                                                        |

| CPUC0                      | 44                                          | 0    | "Complementary" clocks of differential pair open-drain CPU outputs.                                                                                                                               |

| REF1/FS2                   | 48                                          | В    | Buffered reference clock output after input data latched during power-up.                                                                                                                         |

# FREQUENCY (MHz) SELECTION TABLE

| I2C<br>Byte0<br>Bit2 | FS3 | FS2 | FS1 | FS0 | СРИ   | PCI  | Spread Spectrum<br>Modulation |

|----------------------|-----|-----|-----|-----|-------|------|-------------------------------|

|                      | 0   | 0   | 0   | 0   | 124.0 | 41.3 | ±0.25%                        |

|                      | 0   | 0   | 0   | 1   | 75.0  | 37.5 | ±0.25%                        |

|                      | 0   | 0   | 1   | 0   | 83.3  | 41.7 | ±0.25%                        |

|                      | 0   | 0   | 1   | 1   | 66.8  | 33.4 | ±0.25%                        |

|                      | 0   | 1   | 0   | 0   | 103.0 | 34.3 | ±0.25%                        |

|                      | 0   | 1   | 0   | 1   | 112.0 | 37.3 | ±0.25%                        |

|                      | 0   | 1   | 1   | 0   | 133.3 | 44.4 | ±0.25%                        |

| 0                    | 0   | 1   | 1   | 1   | 100.0 | 33.3 | ±0.25%                        |

| default              | 1   | 0   | 0   | 0   | 120.0 | 40.0 | ±0.25%                        |

|                      | 1   | 0   | 0   | 1   | 115.0 | 38.3 | ±0.25%                        |

|                      | 1   | 0   | 1   | 0   | 110.0 | 36.7 | ±0.25%                        |

|                      | 1   | 0   | 1   | 1   | 105.0 | 35.0 | ±0.25%                        |

|                      | 1   | 1   | 0   | 0   | 140.0 | 35.0 | ±0.25%                        |

|                      | 1   | 1   | 0   | 1   | 150.0 | 37.5 | ±0.25%                        |

|                      | 1   | 1   | 1   | 0   | 124.0 | 31.0 | ±0.25%                        |

|                      | 1   | 1   | 1   | 1   | 133.3 | 33.3 | ±0.25%                        |

|                      | 0   | 0   | 0   | 0   | 90.0  | 30.0 | ±0.25%                        |

|                      | 0   | 0   | 0   | 1   | 92.5  | 30.8 | ±0.25%                        |

|                      | 0   | 0   | 1   | 0   | 95.0  | 31.7 | ±0.25%                        |

|                      | 0   | 0   | 1   | 1   | 97.5  | 32.5 | ±0.25%                        |

|                      | 0   | 1   | 0   | 0   | 101.5 | 33.8 | ±0.25%                        |

|                      | 0   | 1   | 0   | 1   | 127.0 | 42.3 | ±0.25%                        |

|                      | 0   | 1   | 1   | 0   | 136.5 | 34.1 | ±0.25%                        |

| 1                    | 0   | 1   | 1   | 1   | 100.0 | 33.3 | 0 to -0.5%                    |

| 1                    | 1   | 0   | 0   | 0   | 120.0 | 40.0 | 0 to -0.5%                    |

|                      | 1   | 0   | 0   | 1   | 117.5 | 39.2 | ±0.25%                        |

|                      | 1   | 0   | 1   | 0   | 122.0 | 40.7 | ±0.25%                        |

|                      | 1   | 0   | 1   | 1   | 107.5 | 35.8 | ±0.25%                        |

|                      | 1   | 1   | 0   | 0   | 145.0 | 36.3 | ±0.25%                        |

|                      | 1   | 1   | 0   | 1   | 155.0 | 38.7 | ±0.25%                        |

|                      | 1   | 1   | 1   | 0   | 130.0 | 32.5 | ±0.25%                        |

|                      | 1   | 1   | 1   | 1   | 133.3 | 33.3 | 0 to -0.5%                    |

## **POWER MANAGEMENT**

| CPU_STOP | CPUC0       | CPUT (0:1)  | SDRAM (0:11) | SDRAM12 | CRYSTAL | VCO     |

|----------|-------------|-------------|--------------|---------|---------|---------|

| 0        | Stopped Low | Stopped Low | Stopped Low  | Running | Running | Running |

| 1        | Running     | Running     | Running      | Running | Running | Running |

# **POWER MANAGEMENT (Continued)**

| PD | CPUC0       | CPUT (0:1)  | SDRAM (0:11) | SDRAM12     | CRYSTAL | VCO     |

|----|-------------|-------------|--------------|-------------|---------|---------|

| 0  | Stopped Low | Stopped Low | Stopped Low  | Stopped Low | Stopped | Stopped |

| 1  | Running     | Running     | Running      | Running     | Running | Running |

#### **12C BUS CONFIGURATION SETTING**

| Address Assignment            | A6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>A</b> 5                                                                                                                                                                                           | A4 | А3 | A2 | A1 | A0 | R/W |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|-----|

| Address Assignment            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                    | 0  | 1  | 0  | 0  | 1  | _   |

| Slave<br>Receiver/Transmitter | Provid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Provides both slave write and readback functionality                                                                                                                                                 |    |    |    |    |    |     |

| Data Transfer Rate            | Stand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Standard mode at 100kbits/s                                                                                                                                                                          |    |    |    |    |    |     |

| Serial Bits Reading           | Byte (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The serial bits will be read or sent by the clock driver in the following order  Byte 0 – Bits 7, 6, 5, 4, 3, 2, 1, 0  Byte 1 – Bits 7, 6, 5, 4, 3, 2, 1, 0  -  Byte N – Bits 7, 6, 5, 4, 3, 2, 1, 0 |    |    |    |    |    |     |

| Data Protocol                 | This serial protocol is designed to allow both blocks write and read from the controller. The bytes must be accessed in sequential order from lowest to highest byte. Each byte transferred must be followed by 1 acknowledge bit. A byte transferred without acknowledged bit will terminate the transfer. The write or read block both begins with the master sending a slave address and a write condition (0xD2) or a read condition (0xD3).  Following the acknowledge of this address byte, in Write Mode: the Command Byte and Byte Count Byte must be sent by the master but ignored by the slave, in Read Mode: the Byte Count Byte will be read by the master then all other Data Byte. Byte Count Byte default at power-up is = (0x09). |                                                                                                                                                                                                      |    |    |    |    |    |     |

### **12C CONTROL REGISTERS**

## 1. BYTE 0: Functional and Frequency Select Clock Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description                                                      |

|-------|------|---------|------------------------------------------------------------------|

| Bit 7 | 8    | 0       | FS3 ( see Frequency selection Table )                            |

| Bit 6 | 48   | 1       | FS2 ( see Frequency selection Table )                            |

| Bit 5 | 25   | 0       | FS1 ( see Frequency selection Table )                            |

| Bit 4 | 26   | 0       | FS0 ( see Frequency selection Table )                            |

| Bit 3 | -    | 0       | Frequency selection control bit 1=Via I2C, 0=Via External jumper |

| Bit 2 | -    | 0       | FS4 ( see Frequency selection Table )                            |

| Bit 1 | -    | 1       | 0=Normal 1=Spread Spectrum enable                                |

| Bit 0 | -    | 0       | 0=Normal 1=Tristate Mode for all outputs                         |

# BYTE 1: CPU Clock Register (1=Enable, 0=Disable)

| Bit   | Pin#  | Default | Description                      |

|-------|-------|---------|----------------------------------|

| Bit 7 | -     | 1       | Reserved                         |

| Bit 6 | -     | 1       | Reserved                         |

| Bit 5 | -     | 1       | Reserved                         |

| Bit 4 | -     | 1       | Reserved                         |

| Bit 3 | 40    | 1       | SDRAM12 ( Active/Inactive )      |

| Bit 2 | -     | 1       | Reserved                         |

| Bit 1 | 43,44 | 1       | CPUT0, CPUC0 ( Active/Inactive ) |

| Bit 0 | 46    | 1       | CPUT1 ( Active/Inactive )        |

## 3. BYTE 2: PCI Clock Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description              |

|-------|------|---------|--------------------------|

| Bit 7 | -    | 1       | Reserved                 |

| Bit 6 | 7    | 1       | PCI5 ( Active/Inactive ) |

| Bit 5 | -    | 1       | Reserved                 |

| Bit 4 | 13   | 1       | PCI4 ( Active/Inactive ) |

| Bit 3 | 12   | 1       | PCI3 ( Active/Inactive ) |

| Bit 2 | 11   | 1       | PCI2 ( Active/Inactive ) |

| Bit 1 | 10   | 1       | PCI1 ( Active/Inactive ) |

| Bit 0 | 8    | 1       | PCI0 ( Active/Inactive ) |

## 4. BYTE 3: SDRAM Clock Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description                  |

|-------|------|---------|------------------------------|

| Bit 7 | -    | 1       | Reserved                     |

| Bit 6 | -    | 1       | Reserved                     |

| Bit 5 | 26   | 1       | 48MHz ( Active/Inactive )    |

| Bit 4 | 25   | 1       | 24_48MHz ( Active/Inactive ) |

| Bit 3 | 17   | 1       | SDRAM11 ( Active/Inactive )  |

| Bit 2 | 18   | 1       | SDRAM10 ( Active/Inactive )  |

| Bit 1 | 20   | 1       | SDRAM9 ( Active/Inactive )   |

| Bit 0 | 21   | 1       | SDRAM8 ( Active/Inactive )   |

# 5. BYTE 4: SDRAM Clock Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description                |

|-------|------|---------|----------------------------|

| Bit 7 | 28   | 1       | SDRAM7 ( Active/Inactive ) |

| Bit 6 | 29   | 1       | SDRAM6 ( Active/Inactive ) |

| Bit 5 | 31   | 1       | SDRAM5 ( Active/Inactive ) |

| Bit 4 | 32   | 1       | SDRAM4 ( Active/Inactive ) |

| Bit 3 | 34   | 1       | SDRAM3 ( Active/Inactive ) |

| Bit 2 | 35   | 1       | SDRAM2 ( Active/Inactive ) |

| Bit 1 | 37   | 1       | SDRAM1 ( Active/Inactive ) |

| Bit 0 | 38   | 1       | SDRAM0 ( Active/Inactive ) |

# 6. BYTE 5: Peripheral Clock Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description                                             |

|-------|------|---------|---------------------------------------------------------|

| Bit 7 | -    | Χ       | Inverted Power-up latched FS3 value (Read only)         |

| Bit 6 | -    | Χ       | Inverted Power-up latched FS2 value (Read only)         |

| Bit 5 | -    | Χ       | Inverted Power-up latched FS1 value (Read only)         |

| Bit 4 | -    | X       | Inverted Power-up latched FS0 value (Read only)         |

| Bit 3 | -    | 1       | Reserved                                                |

| Bit 2 | -    | X       | Inverted Power-up latched SEL24_48MHz value (Read only) |

| Bit 1 | 48   | 1       | REF1 ( Active/Inactive )                                |

| Bit 0 | 2    | 1       | REF0 ( Active/Inactive )                                |

## 7. BYTE 6: Revision ID and Vendor ID Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description        |

|-------|------|---------|--------------------|

| Bit 7 | -    | 0       | Revision ID Bit 3* |

| Bit 6 | -    | 0       | Revision ID Bit 2* |

| Bit 5 | -    | 0       | Revision ID Bit 1* |

| Bit 4 | -    | 0       | Revision ID Bit 0* |

| Bit 3 | -    | 0       | Vendor ID Bit 3*   |

| Bit 2 | -    | 0       | Vendor ID Bit 2*   |

| Bit 1 | -    | 1       | Vendor ID Bit 1*   |

| Bit 0 | -    | 1       | Vendor ID Bit 0*   |

Note: \*: Default value at power-up

# 8. BYTE 7: Linear Programming (M) Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description                                        |  |

|-------|------|---------|----------------------------------------------------|--|

| Bit 7 | -    | 0       | Linear programming sign bit ( 0 is "+", 1 is "-" ) |  |

| Bit 6 | -    | 0       | Linear programming magnitude bit 6 (MSB)           |  |

| Bit 5 | -    | 0       | Linear programming magnitude bit 5                 |  |

| Bit 4 | -    | 0       | Linear programming magnitude bit 4                 |  |

| Bit 3 | -    | 0       | Linear programming magnitude bit 3                 |  |

| Bit 2 | -    | 0       | Linear programming magnitude bit 2                 |  |

| Bit 1 | -    | 0       | Linear programming magnitude bit 1                 |  |

| Bit 0 | -    | 0       | Linear programming magnitude bit 0 (LSB)           |  |

## 9. BYTE 8: Device ID Register (1=Enable, 0=Disable)

| Bit   | Pin# | Default | Description      |

|-------|------|---------|------------------|

| Bit 7 | -    | 0       | Reserved         |

| Bit 6 | -    | 0       | Device ID Bit 6* |

| Bit 5 | -    | 0       | Device ID Bit 5* |

| Bit 4 | -    | 0       | Device ID Bit 4* |

| Bit 3 | -    | 0       | Device ID Bit 3* |

| Bit 2 | -    | 0       | Device ID Bit 2* |

| Bit 1 | -    | 1       | Device ID Bit 1* |

| Bit 0 | -    | 0       | Device ID Bit 0* |

Note: \*: Default value at power-up

#### PROGRAMMING OF CPU FREQUENCY

To simplify traditional loop counter setting, the PLL205-01 device incorporates SMART-BYTE ™ technology with a single byte programming via I2C to better optimize clock jitter and spread spectrum performance. Detail of PLL205-01's dual mode frequency programming method is described below:

## 1. ROM-table Frequency Programming:

The pre-defined 32 frequencies found in Frequency table can be accessed either through 5 external jumpers or by setting internal I2C register in BYTE0.

## 2. Micro-step Linear Frequency Programming:

CPU Frequency can be programmed via I2C in fine and linear positive or negative stepping around selected CPU frequency in Frequency table. The highest step is either +127 or -127. Other bus frequencies will be changed proportionally with the rate that CPU frequency change. The formula is as follow:

$$F_{CPU} = F_{CPU.ROM-Table} \pm \alpha (=0.22)^* M$$

Where:

- 1. M is magnitude factor defined in I2C Byte 7.bit(0:6)

- 2.  $\pm$  (sign bit) of M is defined in I2C Byte7.bit 7

- 3.  $\alpha$  is a constant  $\alpha = 0.22$

# FREQUENCY PROGRAMMING EXAMPLE:

## 1. Procedures to program target CPU frequency to 139.0 Mhz:

- A. Locate the closest CPU frequency from Frequency-ROM table: 136.5

- B.  $\alpha = 0.22$

- C. Solve M (Linear Magnitude factor) in integer:

$$M = (F_{CPU} - F_{CPU-ROMTABLE}) / \alpha$$

= (139 - 136.5) / 0.22

= 11

D. Program I2C register:

$$F_{CPU} = 136.5 + (0.22) * 11 = 138.92$$

(% of frequency increased = 1.8 %)  $F_{PCI} = 34.1 * (1+1.8\%) = 34.7$

### **ELECTRICAL SPECIFICATIONS**

#### 1. Absolute Maximum Ratings

| PARAMETERS                    | SYMBOL         | MIN.                 | MAX.                 | UNITS |

|-------------------------------|----------------|----------------------|----------------------|-------|

| Supply Voltage                | $V_{DD}$       | V <sub>SS</sub> -0.5 | 7                    | V     |

| Input Voltage, dc             | VI             | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc            | Vo             | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature           | T <sub>S</sub> | -65                  | 150                  | °C    |

| Ambient Operating Temperature | TA             | 0                    | 70                   | °C    |

| Junction Temperature          | TJ             |                      | 115                  | °C    |

| ESD Voltage                   |                |                      | 2                    | KV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

## 2. AC/DC Electrical Specifications

| PARAMETERS               | SYMBOL           | CONDITIONS                                                          | MIN.                 | TYP.   | MAX.                 | UNITS |

|--------------------------|------------------|---------------------------------------------------------------------|----------------------|--------|----------------------|-------|

| Input High Voltage       | ViH              |                                                                     | 2.0                  |        | V <sub>DD</sub> +0.3 | V     |

| Input Low Voltage        | V <sub>IL</sub>  |                                                                     | V <sub>SS</sub> -0.3 |        | 0.8                  | V     |

| Input High Current       | l <sub>IH</sub>  | VIN = VDD                                                           |                      |        | 5                    | uA    |

| Input Low Current        | l <sub>IL1</sub> | Logic inputs without internal pull-up on SCLK, V <sub>IN</sub> = 0V | -5                   |        |                      | uA    |

| Input Low Current        | l <sub>IL2</sub> | Logic inputs with internal pull-up resistors, V <sub>IN</sub> = 0V  | -200                 |        |                      | uA    |

| Power Down               | PD               |                                                                     |                      |        | 600                  | uA    |

| Pull-up resistor         | $R_{pu}$         | Pin 2,7,8,10,25,26,48                                               |                      | 120    |                      | Kohm  |

|                          | I <sub>DD</sub>  | C <sub>L</sub> =0 pF @ 66MHz                                        |                      |        |                      |       |

| Operating Supply Current |                  | C <sub>L</sub> =0 pF @ 100MHz                                       |                      |        | 180                  | mA    |

|                          |                  | C <sub>L</sub> =0 pF @ 133MHz                                       |                      |        |                      |       |

| Input frequency          | Fı               | $V_{DD} = 3.3V$                                                     | 12                   | 14.318 | 16                   | Mhz   |

| Input Canacitance        | Cin              | Logic Inputs                                                        |                      |        | 5                    | PF    |

| Input Capacitance        | CINX             | XIN & XOUT pins                                                     | 27                   |        | 45                   | PF    |

# 2. Output Buffer Electrical Specifications

Unless otherwise stated, all power supplies =  $3.3V\pm5\%$ , and ambient temperature range  $T_A=0$ °C to 70°C

| PARAMETERS          | SYMBOL | OUTPUTS                   | CONDITIONS                                               | MIN. | TYP. | MAX. | UNITS |

|---------------------|--------|---------------------------|----------------------------------------------------------|------|------|------|-------|

| Output Rise time    | Tor    | CPU (Open Drain)          | Measured @ 0.3V ~ 1.2V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 0.9  | - ns  |

|                     |        | REF(0:1)                  | Measured @ 0.4V ~ 2.4V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 4    |       |

| Output Nise time    |        | PCI(0:5)                  | Measured @ 0.4V ~ 2.4V,<br>C <sub>L</sub> =30pf, 3.3V±5% |      |      | 2    | 113   |

|                     |        | 24_48MHz, 48MHz           | Measured @ 0.4V ~ 2.4V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 4    |       |

|                     |        | CPU (Open Drain)          | Measured @ 1.2V ~ 0.3V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 0.9  |       |

| Output Fall time    | Тоғ    | REF(0:1)                  | Measured @ 2.4V ~ 0.4V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 4    | ns    |

| Output I un time    |        | PCI(0:5)                  | Measured @ 2.4V ~ 0.4V,<br>C <sub>L</sub> =30pf, 3.3V±5% |      |      | 2    |       |

|                     |        | 24_48MHz, 48MHz           | Measured @ 2.4V ~ 0.4V,<br>C <sub>L</sub> =20pf, 3.3V±5% |      |      | 4    |       |

| Duty Cycle          | DT     | REF(0:1),CPU,<br>PCI(0:5) | V <sub>T</sub> = 50%                                     | 45   |      | 55   | %     |

|                     |        | 24_48MHz, 48MHz           | $V_T = 1.5V$                                             |      |      |      |       |

|                     | TSKEW  | CPU to CPU                |                                                          |      |      | 200  | nc    |

| Clock Skew          |        | PCI to PCI                | V <sub>T</sub> = 50%                                     |      |      | 200  | ps    |

| Clock Skew          |        | CPU to PCI                |                                                          | 0    |      | 3    | nc    |

|                     |        | CPU to AGP                |                                                          | -500 |      | 500  | ns    |

| Output<br>Impedance | Zo     | СРИ                       | $V_O = V_X$                                              |      | 50   |      |       |

|                     |        | PCI(0:5)                  | V <sub>DD</sub> =3.3V±5%                                 |      | 30   |      | Ohm   |

|                     |        | REF(0:1)                  |                                                          |      | 40   |      |       |

|                     |        | REF1                      | VDD=3.3V±370 40                                          |      |      | _    |       |

|                     |        | 24_48MHz, 48MHz           |                                                          |      | 40   |      |       |

## 2. Output Buffer Electrical Specifications, continued

Unless otherwise stated, all power supplies =  $3.3V\pm5\%$ , and ambient temperature range  $T_A$ =  $0^{\circ}C$  to  $70^{\circ}C$

| PARAMETERS                        | SYMBOL           | OUTPUTS          | CONDITIONS             | MIN. | TYP. | MAX.                        | UNITS |

|-----------------------------------|------------------|------------------|------------------------|------|------|-----------------------------|-------|

|                                   | Гон              | CPU              |                        |      |      |                             | mA    |

|                                   |                  | REF(0:1)         |                        |      |      | -22                         |       |

| Output High Current               |                  | PCI(0:5)         | $V_{OH} = 2.0V$        |      |      | -16                         |       |

|                                   |                  | 24_48MHz         |                        |      |      | -22                         |       |

|                                   |                  | 48MHz            |                        |      |      | -22                         |       |

|                                   |                  | CPU              | V <sub>OL</sub> = 0.4V | 20   |      |                             | mA    |

|                                   |                  | REF(0:1)         |                        | 16   |      |                             |       |

| Output Low Current                | loL              | PCI(0:5)         | $V_{OL} = 0.8V$        | 19   |      |                             |       |

|                                   |                  | 24_48MHz         | VOL = 0.8V             | 16   |      |                             |       |

|                                   |                  | 48MHz            |                        | 16   |      |                             |       |

| Jitter, One Sigma                 | Jsigma           | REF,48MHz,24MHz  | V <sub>T</sub> = 1.5V  |      |      | 0.5                         | ns    |

| littor Abcoluto                   |                  | CPU              | V <sub>T</sub> = 50%   | -250 |      | 250                         | ps    |

| Jitter, Absolute                  | J <sub>Abs</sub> | REF,48MHz,24MHz  | V <sub>T</sub> = 1.5V  | -1   |      | -22<br>-16<br>-22<br>-22    | ns    |

| littor (qualo to qualo)           | Јсус-сус         | CPU              | $V_T = V_X$            |      |      | 250                         |       |

| Jitter (cycle to cycle)           |                  | PCI              | Measured @ 1.5V        |      |      | 250                         | ps    |

| AC Differential<br>Voltage        | V <sub>DIF</sub> |                  |                        | 0.4  |      |                             | V     |

| DC Differential<br>Voltage        | V <sub>DIF</sub> | CPU (Open Drain) |                        | 0.2  |      | V <sub>pullup</sub><br>+0.6 | V     |

| Differential<br>Crossover Voltage | V <sub>X</sub>   |                  |                        | 550  |      | 1100                        | mV    |

Note:  $V_{pullup} = 1.5V$  (external);  $V_{DIF}$  specifies the minimum input differential voltages ( $V_{TR}$ - $V_{CP}$ ) required for switching, where  $V_{TR}$  is the "true" input level and  $V_{CP}$  is the "complement" input level.

#### **PACKAGE INFORMATION**

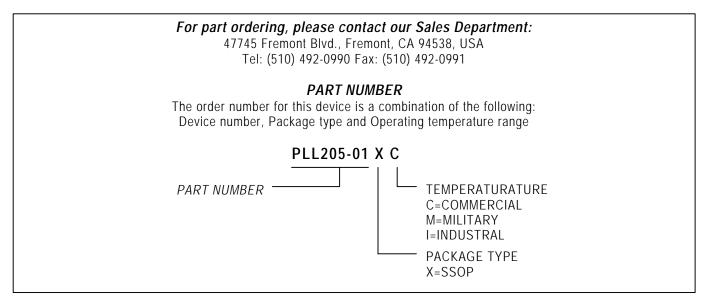

#### ORDERING INFORMATION

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by PhaseLink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: PhaseLink's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.