November 1998 Version 1.0

## PCI 9054

## PCI I/O Accelerator

I<sub>2</sub>O Compatible, CompactPCI Hot Swap Friendly PCI Bus Master Interface Chip for Adapters and Embedded Systems

#### **FEATURES**

- PCI Specification version 2.2 (v2.2) compliant 32-bit, 33-MHz Bus Master Interface Controller with PCI Power Management features for adapters and embedded systems

- General Purpose Bus Master Interface featuring advanced Data Pipe Architecture<sup>™</sup> technology, which includes two DMA engines, programmable Target and Initiator Data Transfer modes and PCI messaging functions

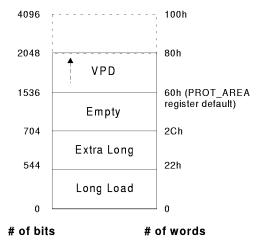

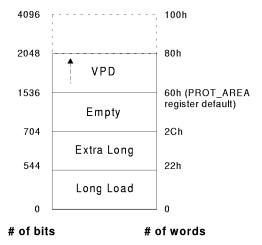

- PCI v2.2 Vital Product Data (VPD) configuration support

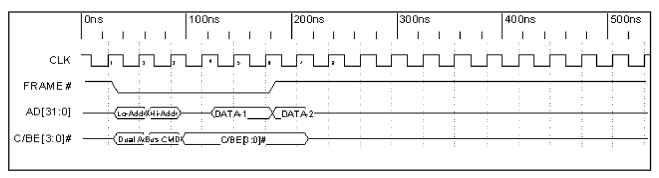

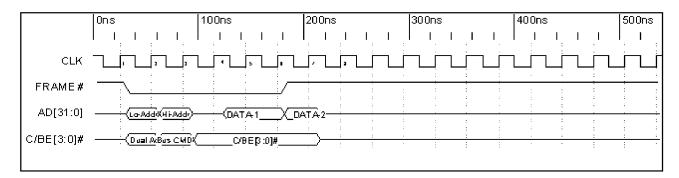

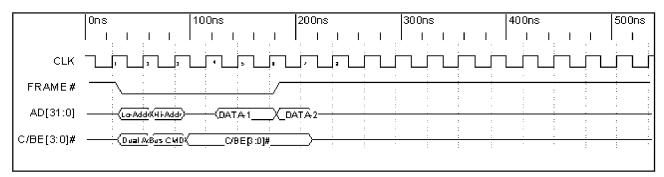

- PCI Dual Address Cycle (DAC) support

- PCI Hot Plug and CompactPCI Hot Swap compliant

- I₂O™ v1.5-Ready Messaging Unit

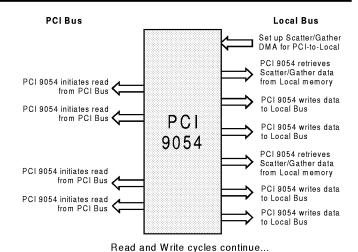

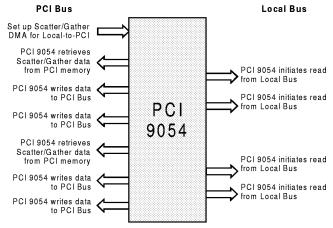

- Two independent DMA channels for Local Bus memory to and from PCI Host Bus Data transfers

- Supports Type 0 and Type 1 Configuration cycles

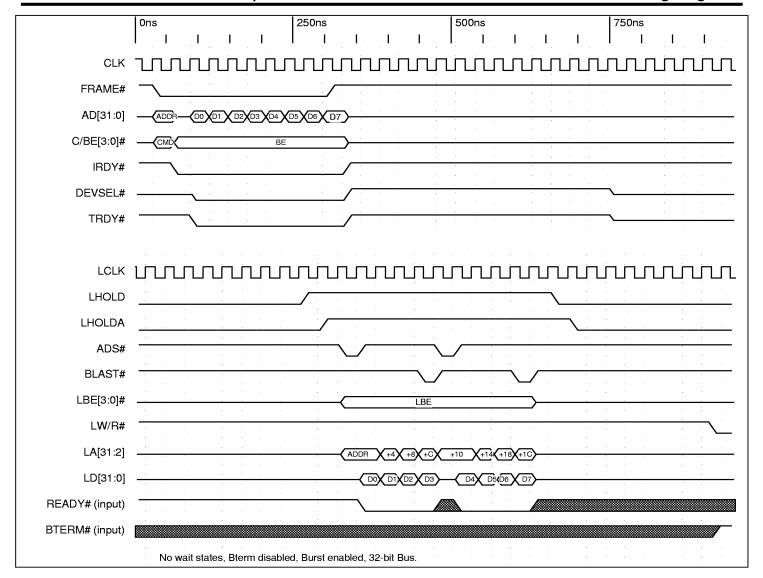

- Programmable Burst Management

- Programmable Interrupt Generator

- Six programmable FIFOs for zero wait state burst operation

- PCI ⇔ Local Data transfers up to 132 MB/s

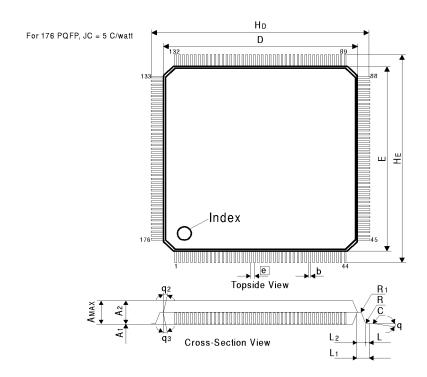

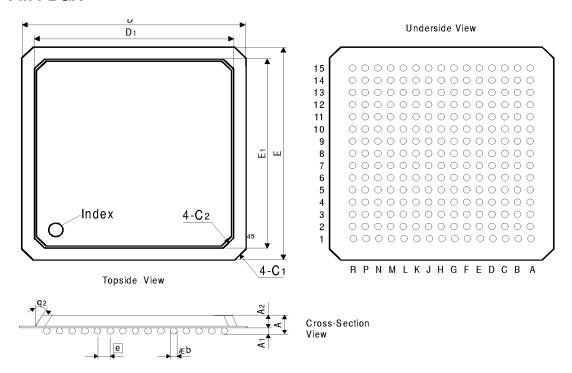

- 3.3V, 5V tolerant PCI and Local signaling supports Universal PCI Adapter designs, 3.3V core, lowpower CMOS in 176-pin PQFP and 225-pin PBGA

- Supports Local Bus Direct-Connect to MPC850 or MPC860 Power QUICC, Intel i960 family and IBM PPC401 CPUs and similar bus protocol devices

- Programmable Local Bus runs up to 50 MHz and supports non-multiplexed 32-bit address/data, multiplexed 32-bit, and slave accesses of 8-, 16-, or 32-bit Local Bus devices

- Serial EEPROM interface

- Three PCI-to-Local Address spaces

- Programmable Local Bus wait states

- Programmable prefetch counter

- Local Bus runs asynchronously to the PCI Bus

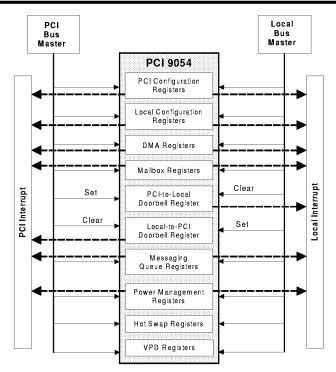

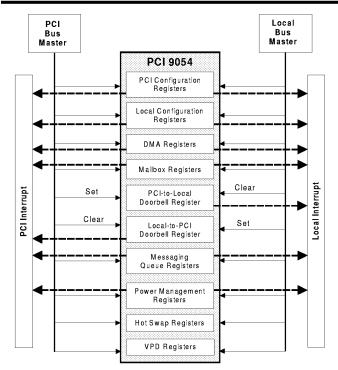

- Eight 32-bit Mailbox and two 32-bit Doorbell registers

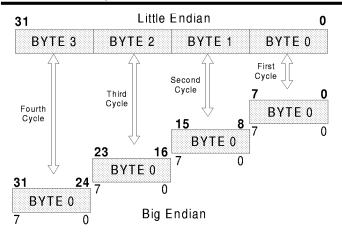

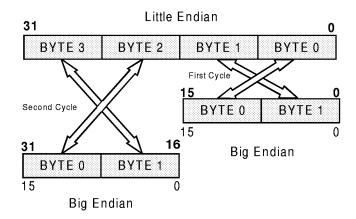

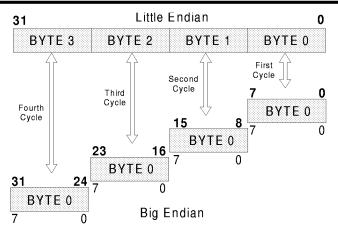

- Performs Big Endian ⇔ Little Endian conversion

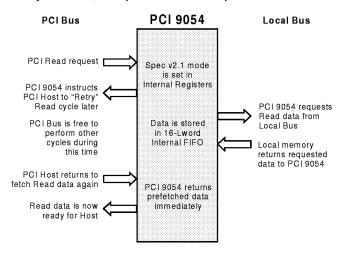

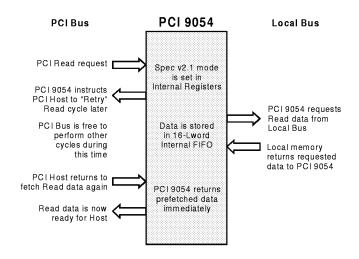

- PCI-to-Local Delayed Read mode

- Local-to-PCI Deferred Read mode (M mode only)

- Flexible 3.3V, 5V Tolerant Local Bus operation up to 50 MHz

- Industrial Temp Range operation

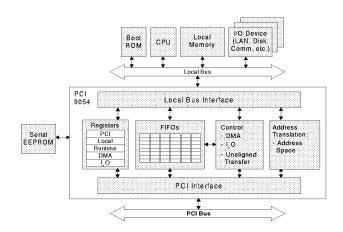

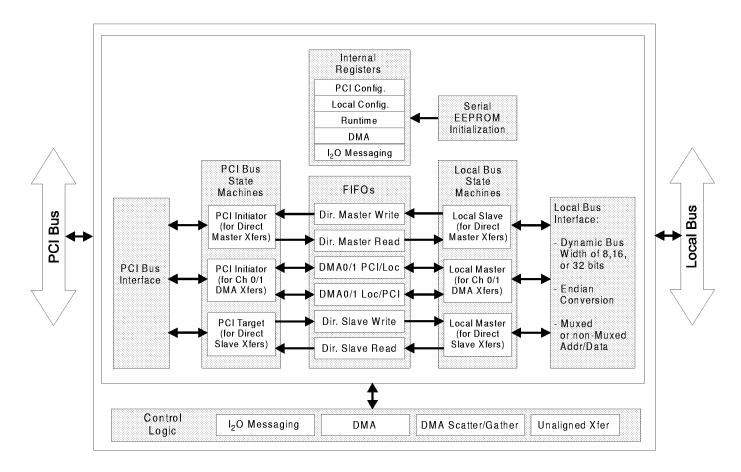

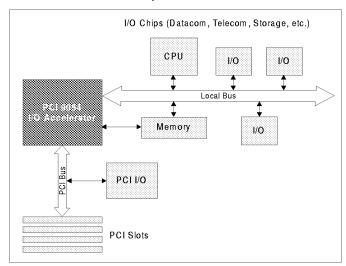

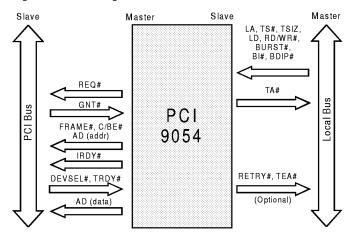

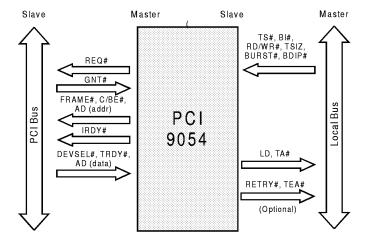

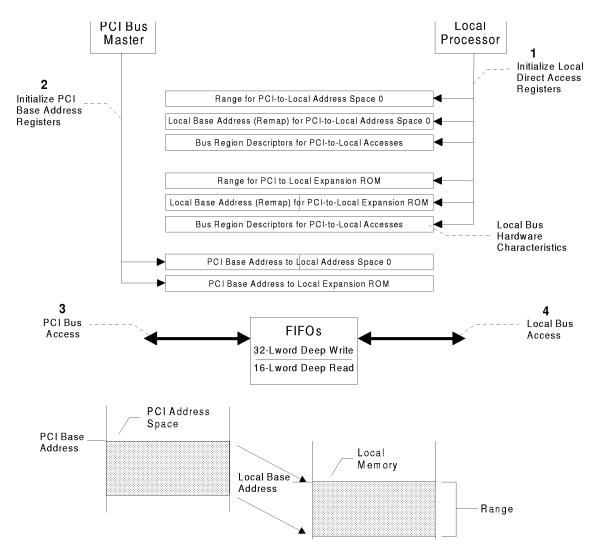

**Typical Adapter Block Diagram**

Features PCI 9054 Data Book

PCI 9054 Internal Block Diagram

# 1. COMPANY AND PRODUCT BACKGROUND

PLX Technology, Inc., the world leader in PCI-to-Local Bus I/O accelerator chips, supports more than 500 OEM customers in a wide variety of PCI applications. Customer applications include PC workstations and servers, PCI add-in boards, embedded PCI communication systems (such as routers and switches), and industrial PCI implementations (such as CompactPCI, PMC, and Passive Backplane PCI).

PLX Technology, Inc., is an active participant in industry standard committees, including the PCI SIG®, I<sub>2</sub>O SIG®, and PICMG®, and maintains active developer technology and cross-marketing partnerships with industry leaders, such as Intel, IBM, Hewlett-Packard, Motorola, Integrated Systems, WindRiver, and others.

Focused on providing complete solutions for PCI implementations, PLX provides design assistance to customers in the form of Reference Design kits and Software Development kits. Depending upon the application, these kits may include reference boards, API libraries, software debug tools, and sample device drivers with source, enabling customers to quickly bring new designs to production. New tools, application notes, FAQs, and information updates are constantly added to our website (www.plxtech.com) for the convenience of PLX customers. Our expertise and total solutions for the PCI interface allow customers to focus on adding value in their designs without worrying about the complexities of implementing PCI, I<sub>2</sub>O, and CompactPCI.

#### 1.1 PCI 9054 I/O Accelerator

The PCI 9054, a 32-bit 33-MHz PCI Bus Master I/O Accelerator, is the most advanced general-purpose bus Master device available. It offers a robust PCI Specification v2.2 implementation enabling Burst transfers up to 132 MB/second. The PCI 9054 incorporates the industry leading PLX Data Pipe Architecture™ technology, including DMA engines, programmable PCI Initiator and Target Data-Transfer modes, and PCI messaging functions.

### 1.2 Data Pipe Architecture Technology

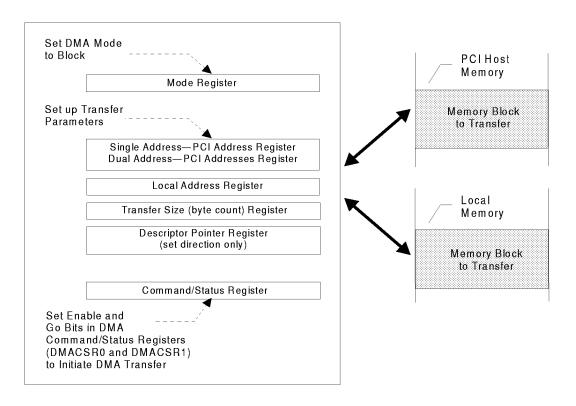

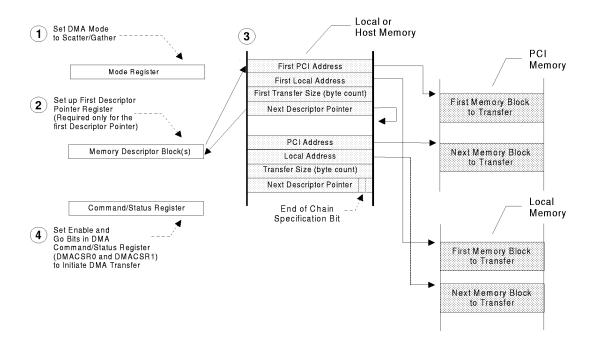

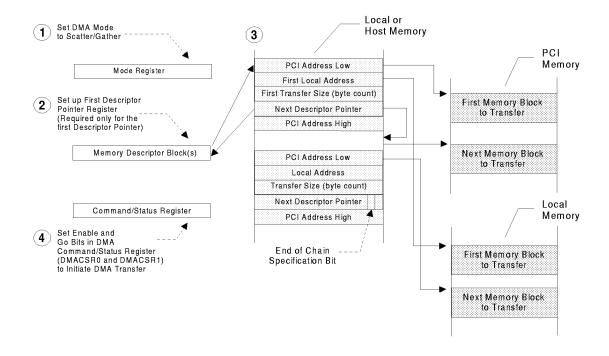

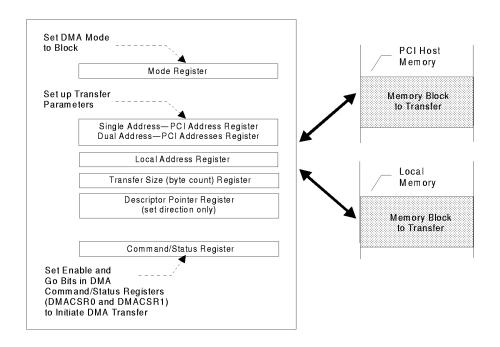

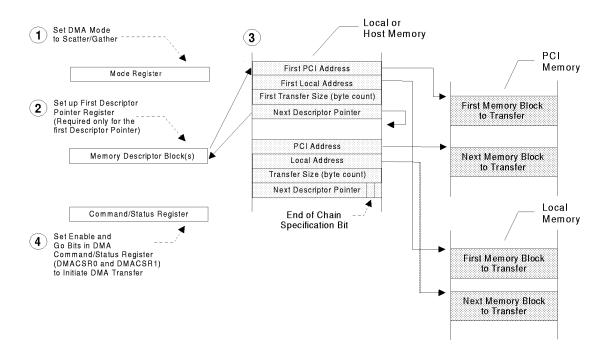

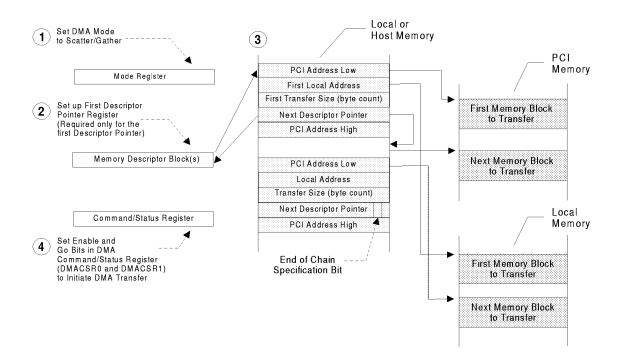

## 1.2.1 Dual DMA Channels

- Dual independent channels provide flexible prioritization scheme

- Programmable Burst length, including unlimited burst

- Direct hardware control of DMA

- Demand mode DMA operation

- Block mode or Scatter/Gather operation

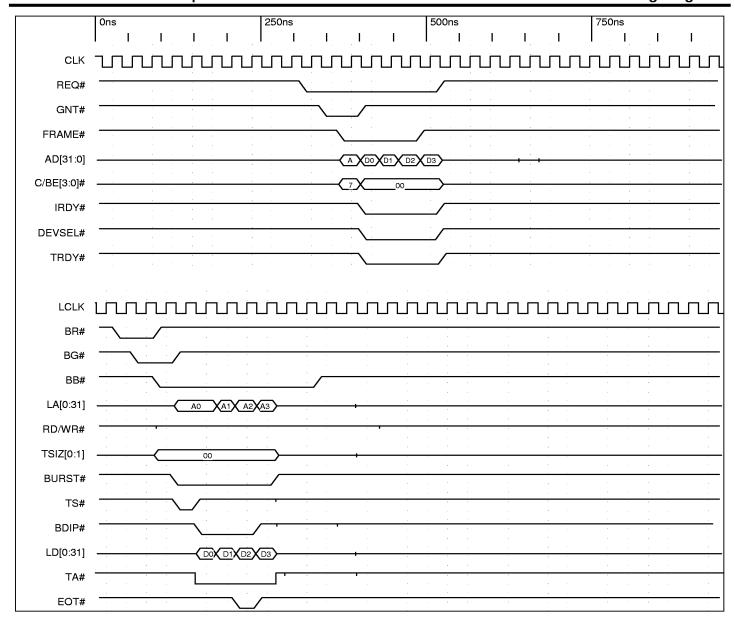

- End of Transfer (EOT) signal

- Shuttle mode DMA channel support provides automatic invalidation of used DMA descriptors

- Unaligned transfer support

- Supports PCI Bus Mastering from the Local Slave-only devices

- Scatter/Gather list management

- Descriptors can be found in PCI Bus memory or in Local Bus memory

- Allows independent Scatter/Gather ring management

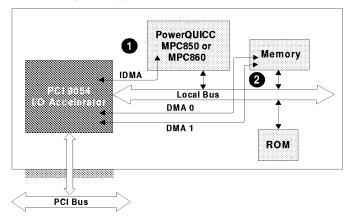

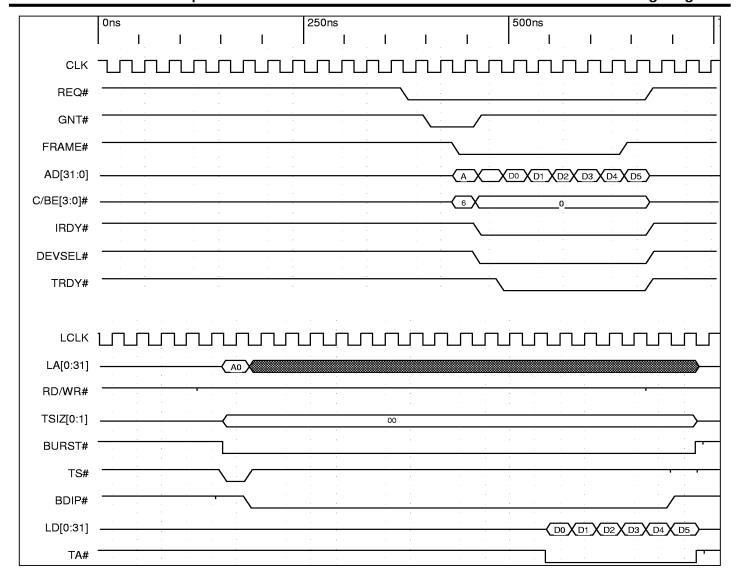

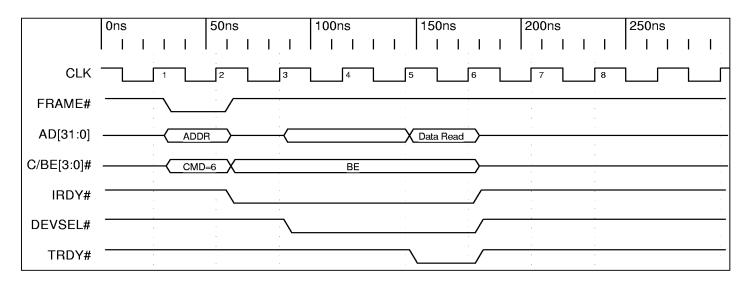

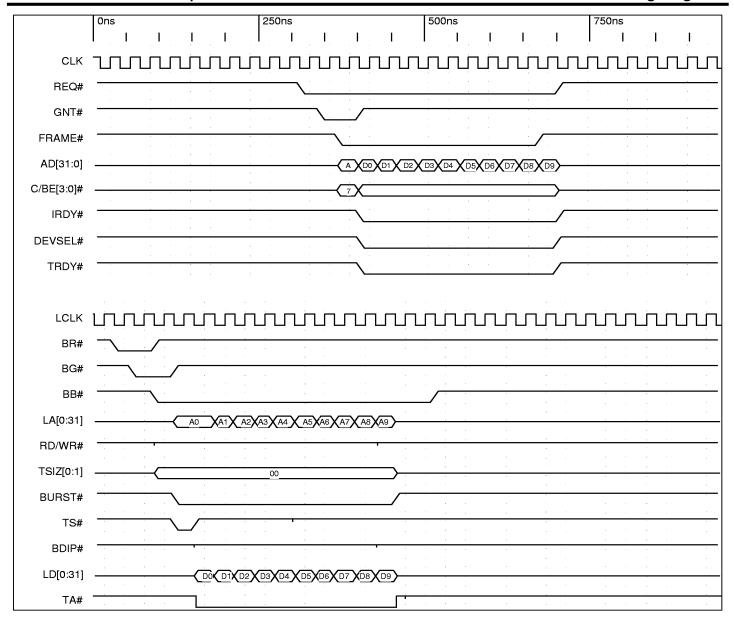

Figure 1-1. High-Performance MPC850 or MPC860 PowerQUICC Adapter Design

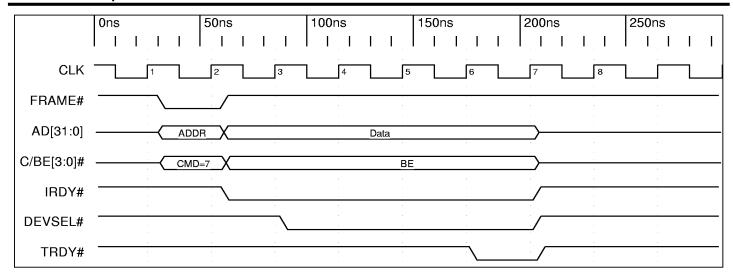

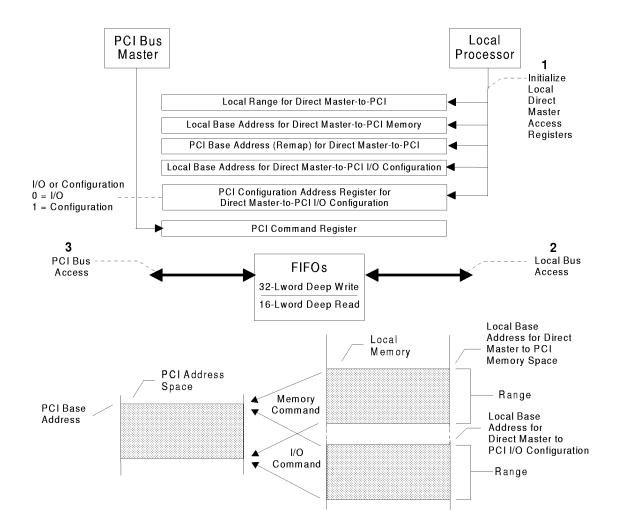

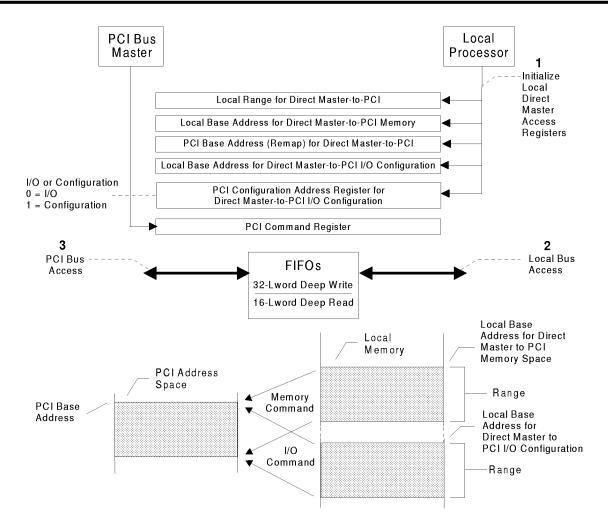

#### 1.2.2 PCI Initiator (Direct Master)

- Type 0 and Type 1 Configuration cycles

- Supports all PCI Memory and I/O cycles

- Initiator Read prefetching

- Burst length control-programmable threshold pointer

- Unaligned transfer control

- Big/Little Endian conversion

©PLX Technology, Inc., 1998 Page 3 Version 1.0

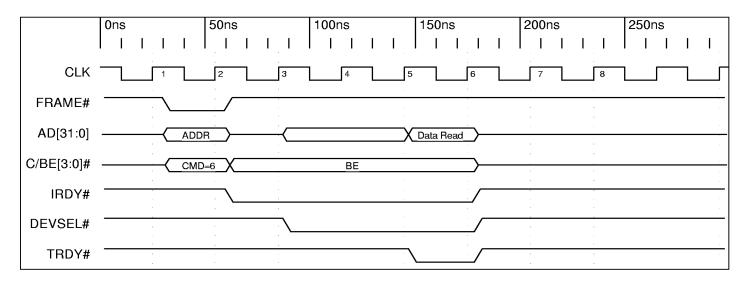

### 1.2.3 PCI Target (Direct Slave)

- Multiple independent address spaces

- Dynamic Local Bus width control

- Target Read prefetching

- Big/Little Endian conversion

- Local Bus priority control

- PCI Latency Timer

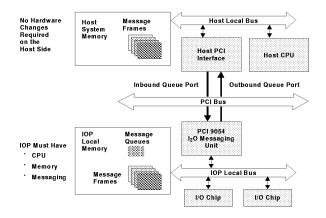

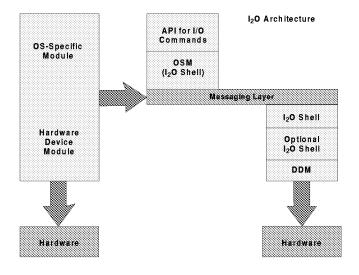

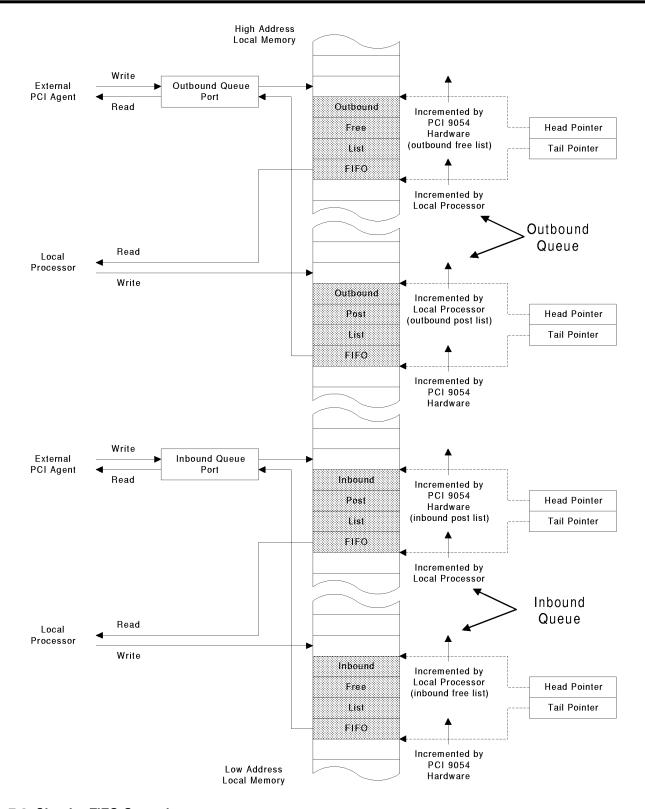

### 1.2.4 PCI Messaging

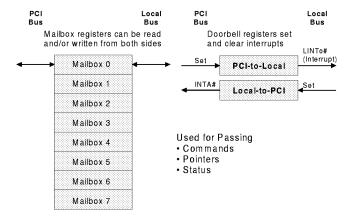

- Complete Messaging Unit with mailbox and doorbell registers

- Queue management pointers that can be used for message passing under the I<sub>2</sub>O protocol or a custom protocol

### 1.3 PCI 9054 PCI Applications

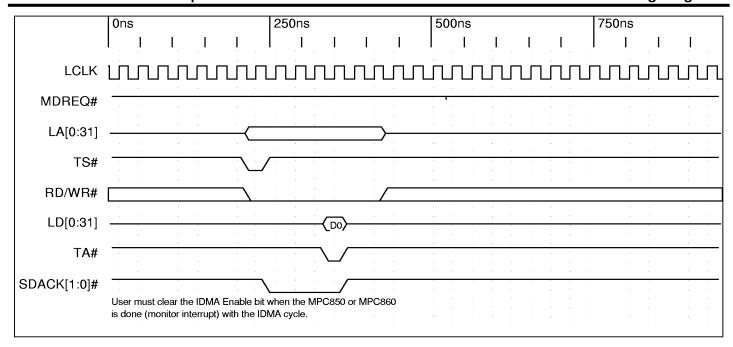

# 1.3.1 High Performance Motorola MPC850 or MPC860 PowerQUICC Designs

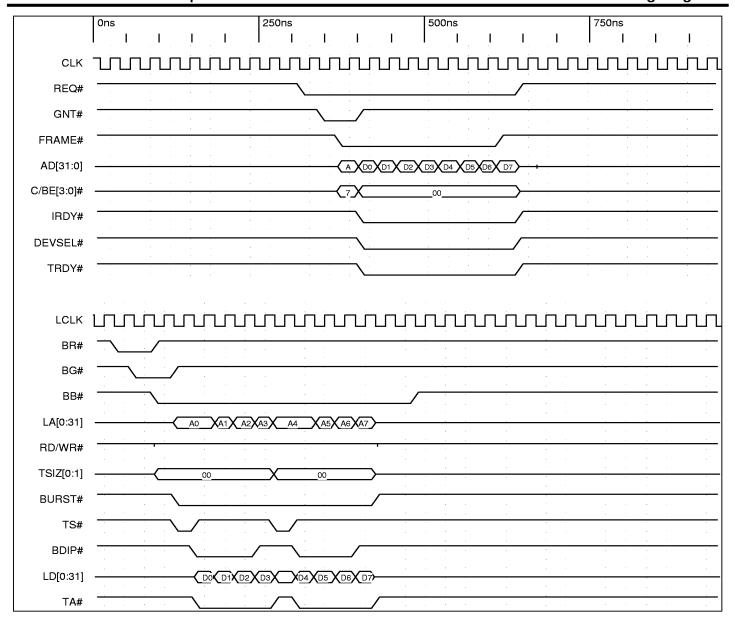

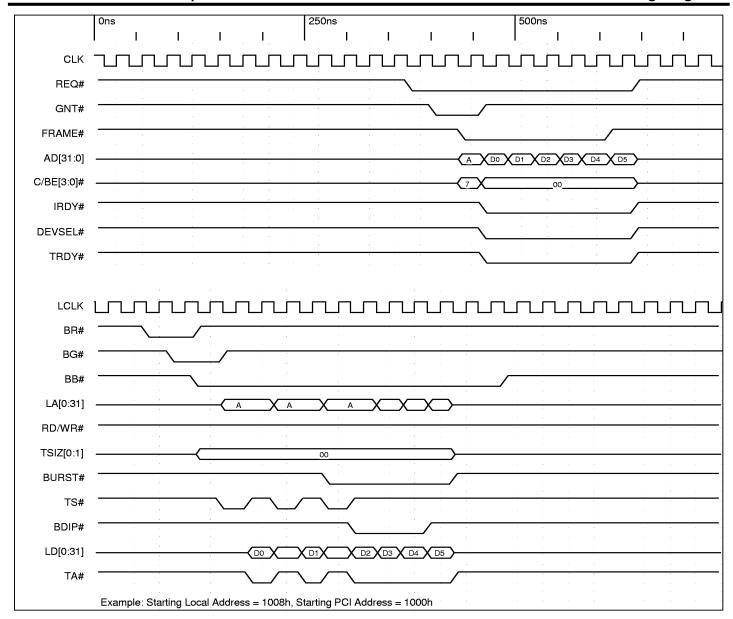

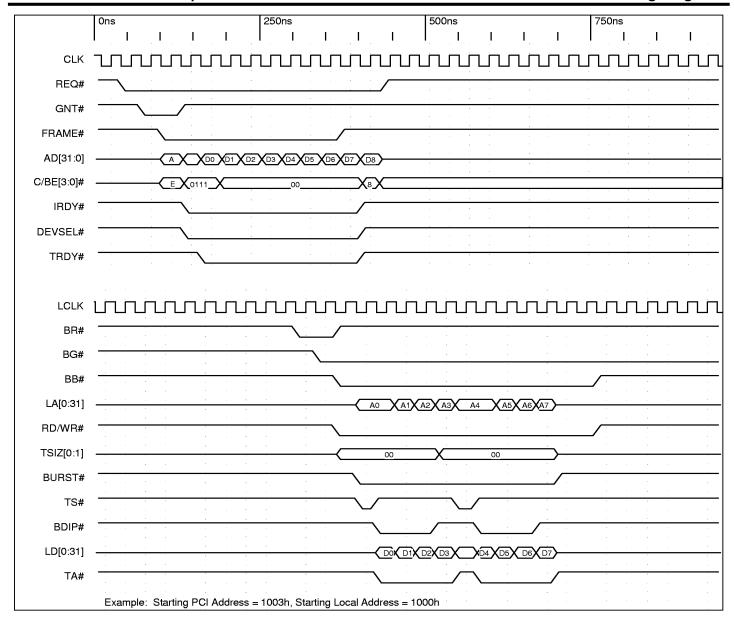

A key application for the PCI 9054 is Motorola MPC850or MPC860-based adapters for telecom and networking applications applications. These include high performance communications such WAN/LAN as controller cards, high-speed modem cards, Frame Relay cards, and routers and switches. The PCI 9054 simplifies designs by providing an industry-leading enhanced direct-connect interface to the MPC850 or MPC860 processor. The flexible PCI 9054 3.3V, 5V tolerant I/O buffers, combined with a Local Bus operation up to 50 MHz, is ideally suited for current and future PowerQUICC processors. The PCI 9054 also provides support for the MPC850 or MPC860 IDMA channel for movement of data between the internal MPC850 or MPC860 I/O and the PCI Bus. In addition, the PCI 9054 also makes use of the advanced Data Pipe Architecture technology, allowing unlimited Burst capability, as shown in Figure 1-1.

- For PowerQUICC IDMA operation, the PCI 9054 transfers data to the PCI Bus under the control of the IDMA handshake protocol.

- 2. At the same time, the PCI 9054 Data Pipe Architecture technology DMA can be operated bidirectionally, with the PCI 9054 as the Master for both buses, to manage transfers of data from the Local Bus to the PCI Bus or from the PCI Bus to the Local Bus. This is a prime example of how the PCI 9054 provides superior general purpose Bus

Master performance and provides designers using the PowerQUICC processor with greater flexibility in implementing multiple simultaneous I/O transfers. The PCI 9054 has unlimited bursting capability, which enhances any MPC850 or MPC860 PowerQUICC design.

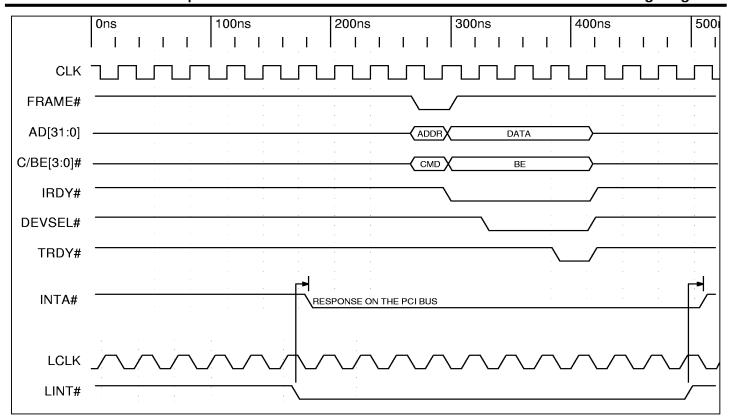

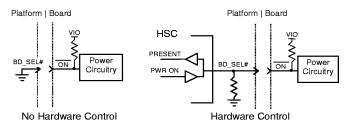

# 1.3.2 High Performance CompactPCI Adapter Designs

Another key application for the PCI 9054 is CompactPCI adapters for telecom and networking applications. These applications include high performance communications such as WAN/LAN controller cards, high-speed modem cards, Frame Relay cards, and telephony cards for telecom switches and remote-access systems.

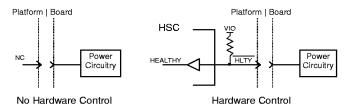

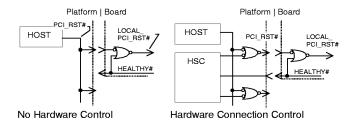

The PCI 9054 has integrated key features to enable live-insertion of Hot Swap CompactPCI adapters. The PCI 9054 PICMG v2.1-compatible Hot Swap *Friendly* PCI interface includes both Hot Swap *Capable* and Hot Swap *Friendly* features.

### 1.3.2.1 Hot Swap Capable

- PCI Specification v2.1 or better

- Tolerant of Vcc from early power

- Tolerant of asynchronous reset

- Tolerant of precharge voltage

- Limited I/O pin leakage at precharge voltage

### 1.3.2.2 Hot Swap Friendly

- Incorporates the Hot Swap Control/Status register (HS\_CSR)

- Incorporates an Extended Capability Pointer (ECP) mechanism

- Incorporates added resources for software control of ENUM#, the ejector switch, and the status LED, which indicates insertion and removal to the user

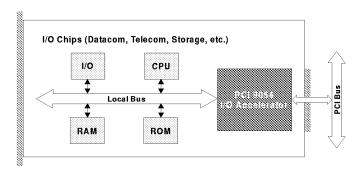

Figure 1-2. High-Performance CompactPCI Adapter

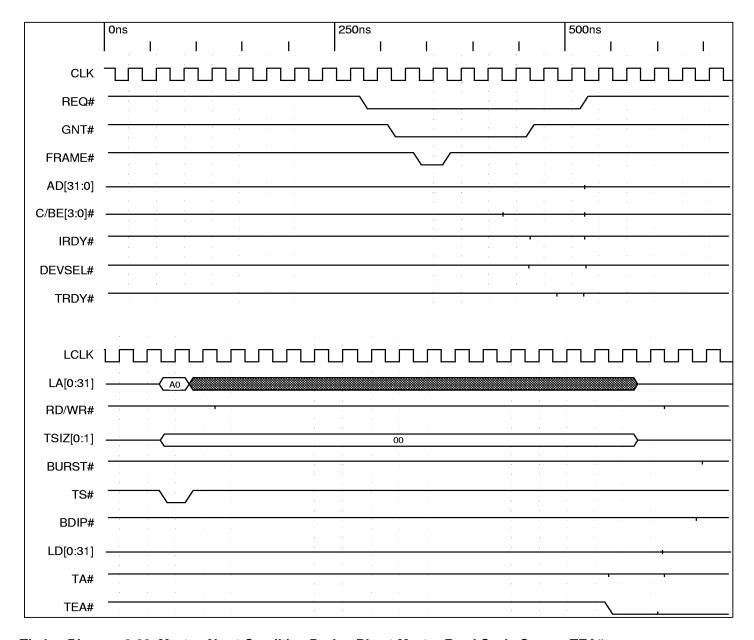

### 1.3.3 PCI Bus Embedded Host Design

Another application for the PCI 9054 is PCI Host-embedded system designs, such as network switches and routers, printer engines, set-top boxes, and industrial equipment. In this configuration, the PCI 9054 Data Pipe Architecture technology allows high-performance transfer modes. In addition, the PCI 9054 supports both Type 0 and Type 1 PCI Configuration cycles that allow the PCI 9054 to configure other PCI devices or cards in the system.

Figure 1-3. High-Performance Embedded Adapter

#### 1.4 PCI 9054 Major Features

**PCI v2.1 and v2.2 Compliant.** Compliant with all aspects of PCI Specification v2.1 and v2.2, including PCI Power Management features. Supports four power states for PCI Power Management functions— $D_0$ ,  $D_1$ ,  $D_2$ , and  $D_{3hot}$ —and the Power Management Event interrupt (PME#).

**VPD Support.** Fully supports the Vital Product Data (VPD) PCI extension, which provides an alternate access method other than Expansion ROM for VPD.

PCI Dual-Address Cycle (DAC) Support (64-bit Address Space). Supports PCI Dual Address Cycle beyond the low 4-GB Address space. PCI DAC can be used during PCI 9054 PCI Bus Master operation (DMA, Direct Master).

PCI Hot Plug and CompactPCI Hot Swap Compliant. Compliant with PCI Hot Plug and CompactPCI Hot Swap adapter specifications.

$I_2O$  Ready Messaging Unit. Incorporates the  $I_2O$  Ready Messaging Unit, which enables the adapter or embedded system to communicate with other  $I_2O$ -supported devices. The  $I_2O$  Messaging Unit is fully compatible with the PCI extension of  $I_2O$  Specification v1.5.

Dual Independently Programmable DMA Controllers with Programmable FIFOs. Provides two independently programmable DMA controllers with shared programmable FIFOs. Each channel supports Block and Scatter/Gather DMA modes, as well as End of Transfer (EOT) mode. The PCI 9054 supports Demand Mode DMA for DMA Channel 0.

**PCI Host Capability.** In Direct Master mode, the PCI 9054 can assert Type 1 and Type 0 PCI Configuration cycles.

Six Programmable FIFOs for Zero Wait State Burst Operation.

Table 1-1. FIFO Depth

| FIFO                | Length    |

|---------------------|-----------|

| Direct Master Read  | 16 Lwords |

| Direct Master Write | 32 Lwords |

| Direct Slave Read   | 16 Lwords |

| Direct Slave Write  | 32 Lwords |

| DMA Read            | 32 Lwords |

| DMA Write           | 32 Lwords |

PCI ⇔ Local Data Transfers up to 132 MB/sec.

**5 Volt Tolerant Operation.** The PCI 9054 requires 3.3V Vcc. It provides 3.3V signaling with 5V I/O tolerance on both the PCI and Local Buses.

**Local Bus Direct Interface.** Supports Local Bus direct interface to the Motorola MPC850 or MPC860 family, the Intel i960 family, the IBM PPC401 family, and other similar bus-protocol devices.

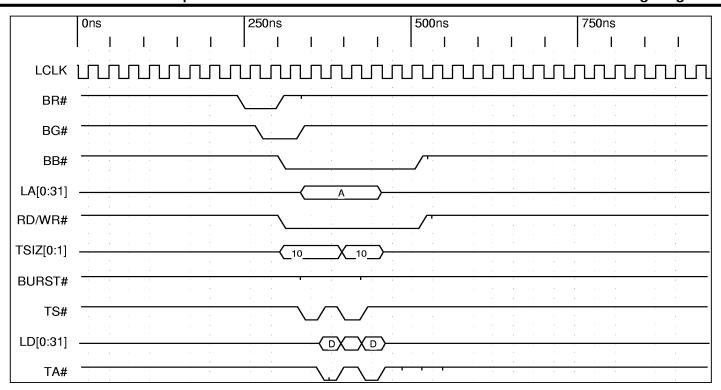

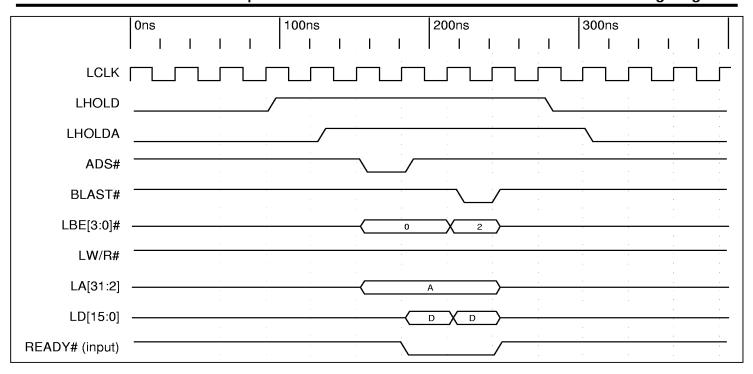

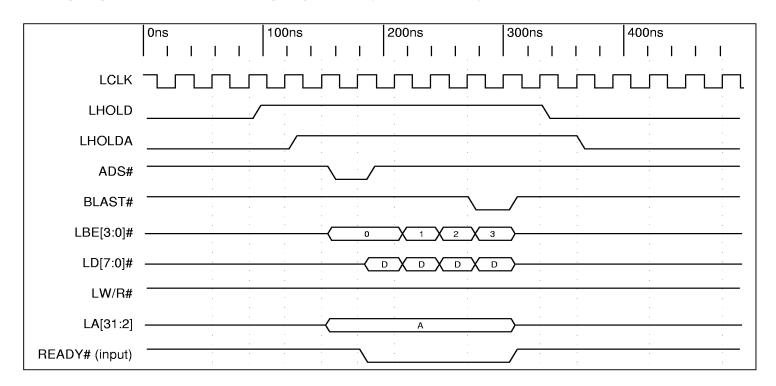

**Programmable Local Bus.** Runs up to 50 MHz and supports non-multiplexed 32-bit address/data, multiplexed 32-bit, and Slave accesses of 8-, 16-, or 32-bit Local Bus devices.

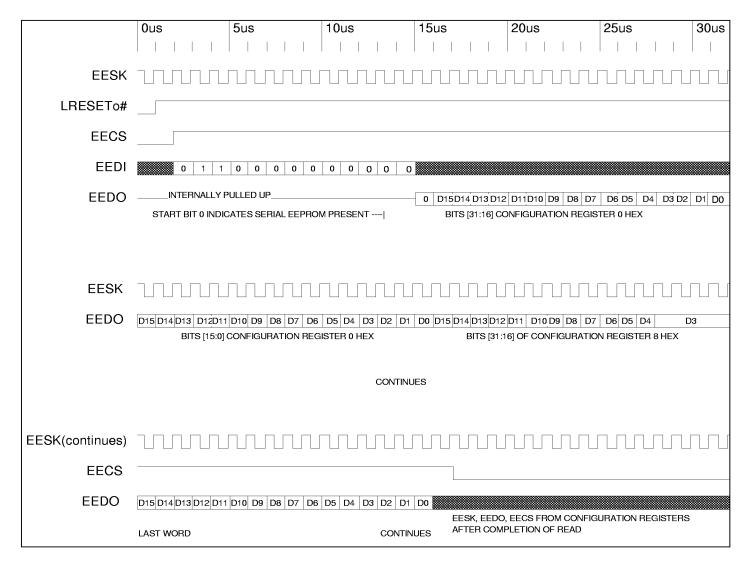

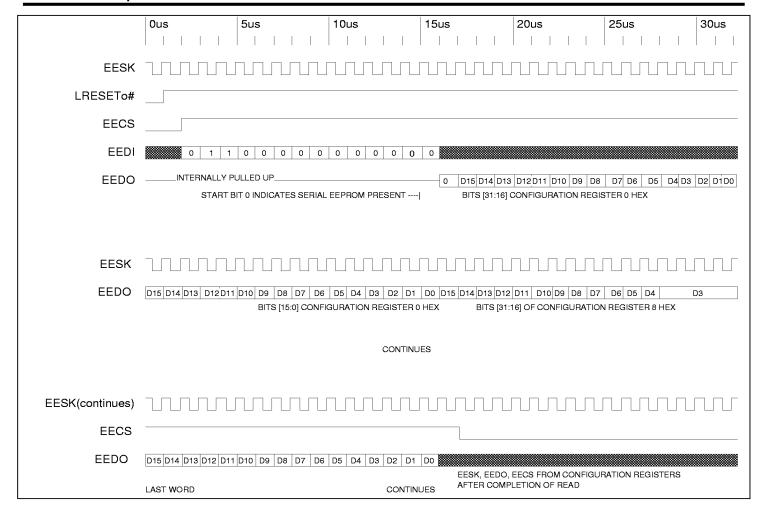

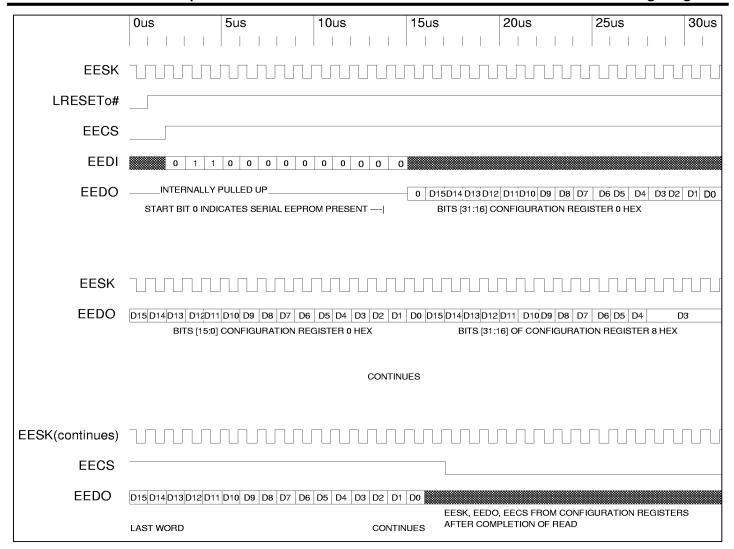

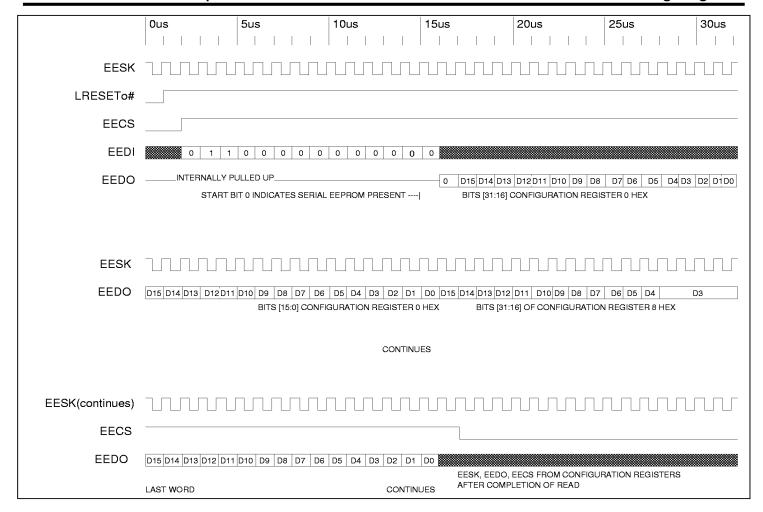

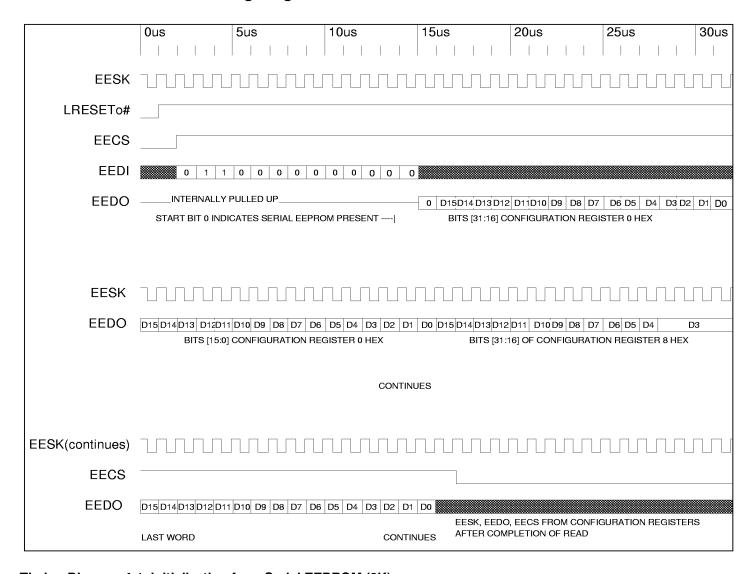

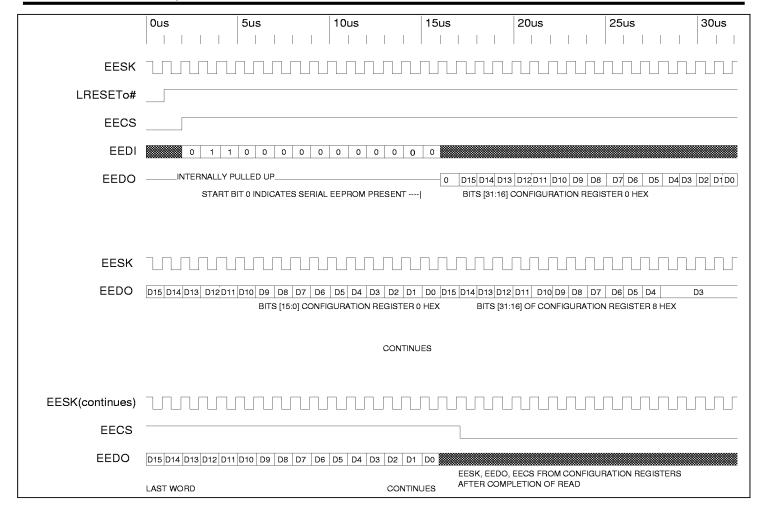

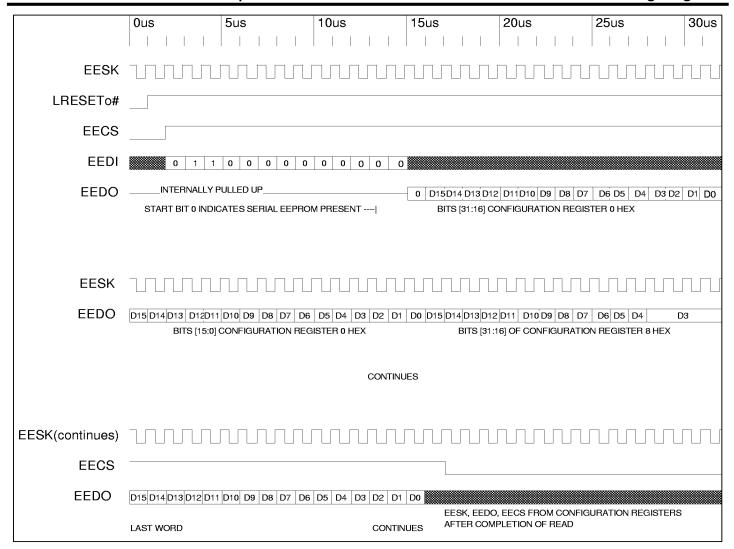

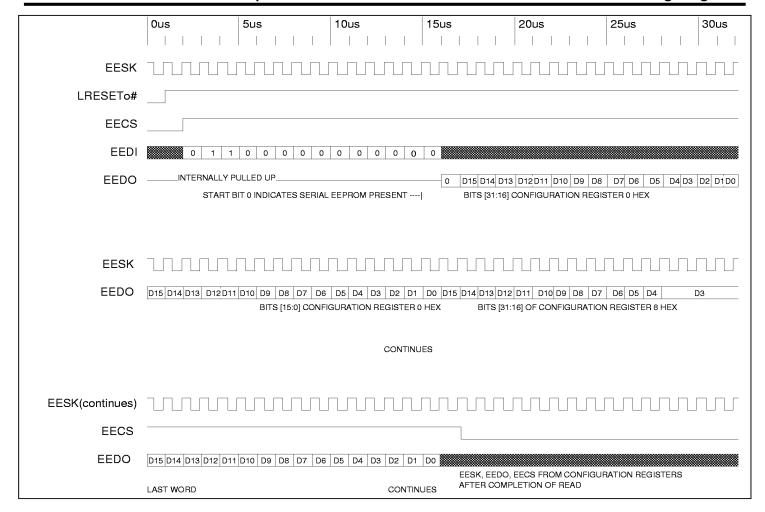

**Serial EEPROM Interface.** Contains an optional serial EEPROM interface (optional only if a Local processor is being used) that can be used to load configuration information. This is useful for loading information that is unique to a particular adapter (such as the Network ID or the Vendor ID).

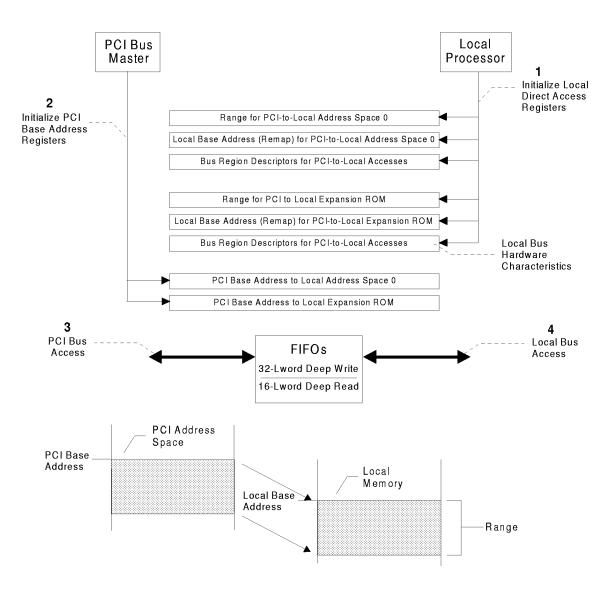

Three PCI-to-Local Address Spaces. The PCI 9054 supports three PCI-to-Local Address spaces when the PCI 9054 is in PCI Target or PCI Slave mode. These spaces (Space 0, Space 1, and Expansion ROM spaces) allow any PCI Bus Master to access the Local Memory spaces with programmable wait states, bus width, burst capabilities, and so forth.

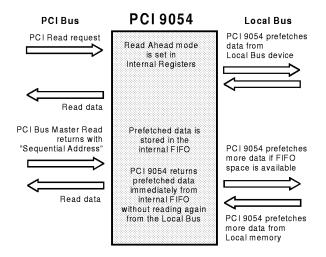

Programmable Prefetch Counter. The PCI 9054 can be programmed to prefetch data during Direct Slave and Direct Master prefetches (known or unknown size). To perform burst reads, prefetching must be enabled. The prefetch size can be programmed to match the Master burst length, or can be used as Read Ahead mode data. The PCI 9054 reads single data (8, 16, or 32 bit) if the Master initiates a single cycle; otherwise, the PCI 9054 prefetches the programmed size.

**Mailbox Registers.** Contains eight 32-bit Mailbox registers that may be accessed from the PCI or Local Bus.

**Doorbell Registers.** Includes two 32-bit doorbell registers. One asserts interrupts from the PCI Bus to the Local Bus. The other asserts interrupts from the Local Bus to the PCI Bus.

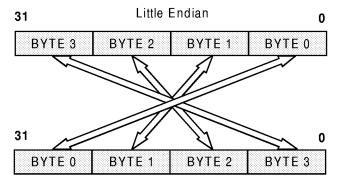

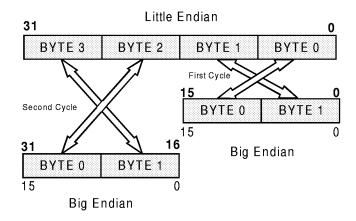

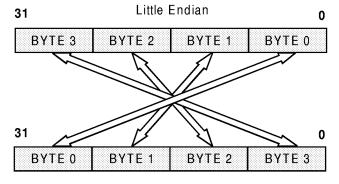

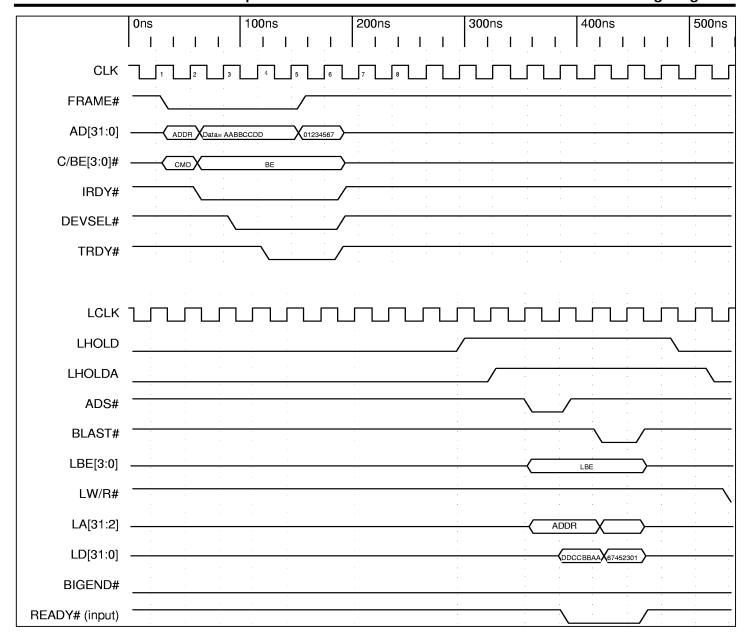

**Big/Little Endian Conversion.** Supports dynamic switching between Big Endian (Address Invariance) and Little Endian (Data Invariance) operations for Direct Slave, Direct Master, DMA, and internal register accesses on the Local Bus.

The PCI 9054 supports on-the-fly Endian conversion for Space 0, Space 1, and Expansion ROM space. The Local Bus can be Big/Little Endian by using the BIGEND# input pin or programmable internal register configuration. When BIGEND# is asserted, it overrides the internal register configuration during Direct Master and internal register accesses on the Local Bus.

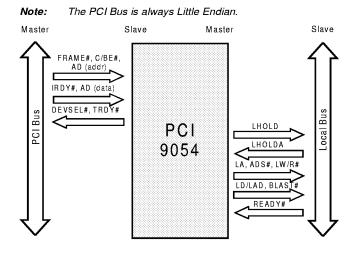

Note: The PCI Bus is always Little Endian.

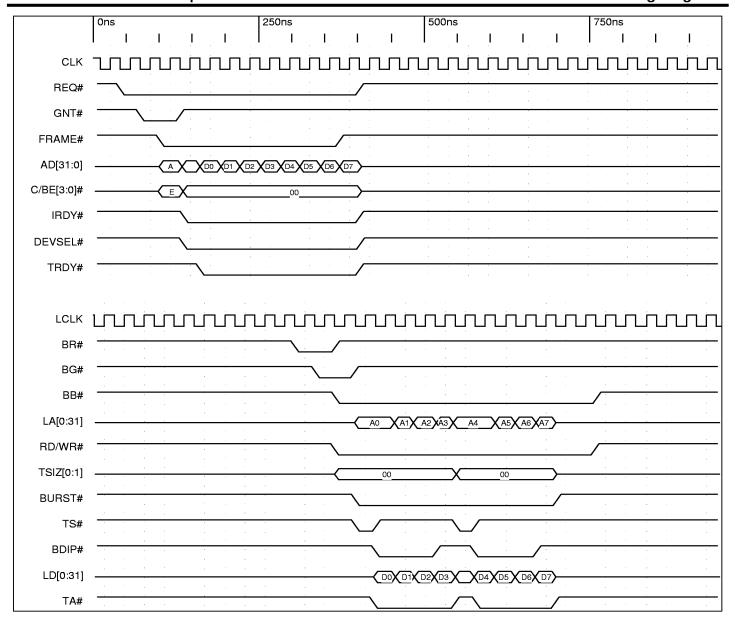

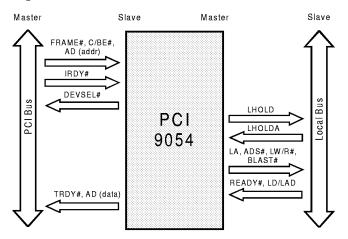

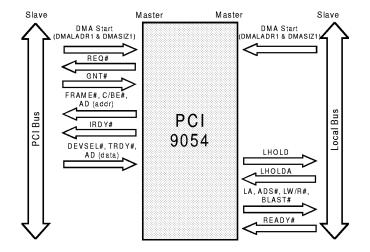

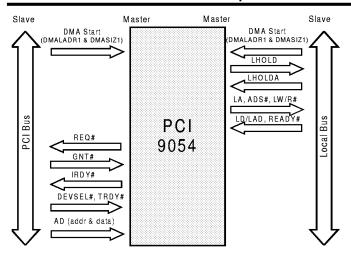

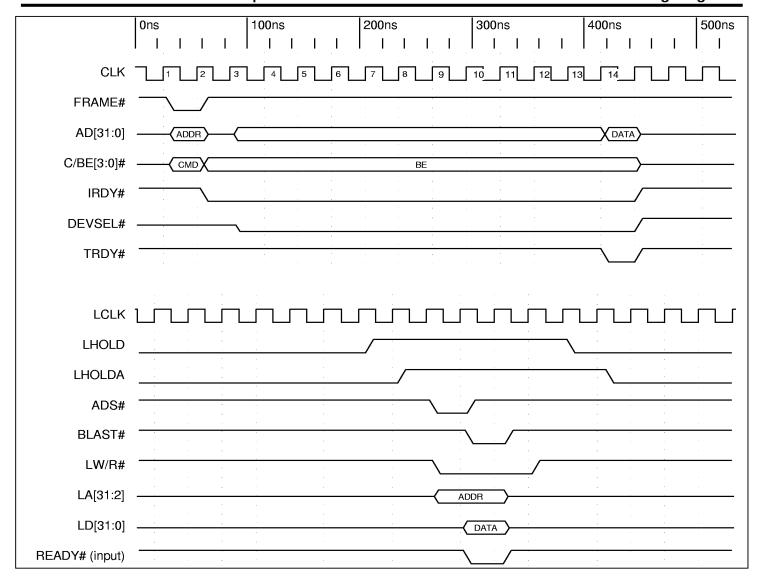

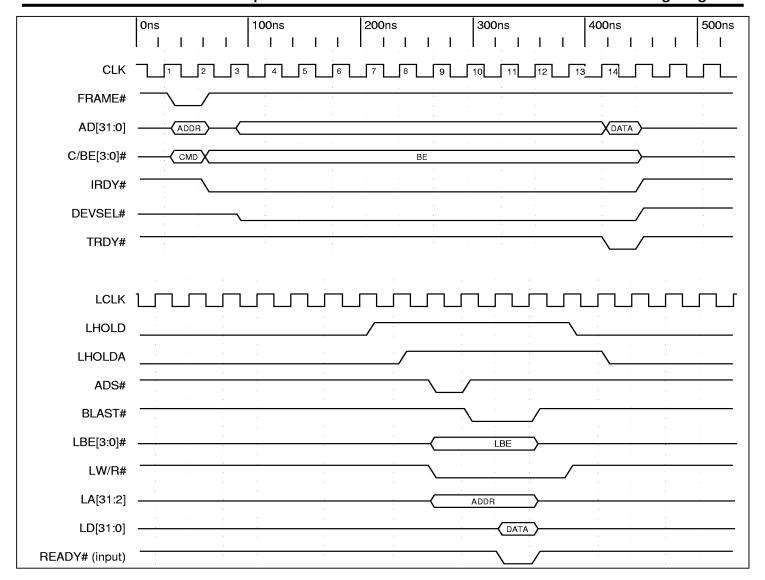

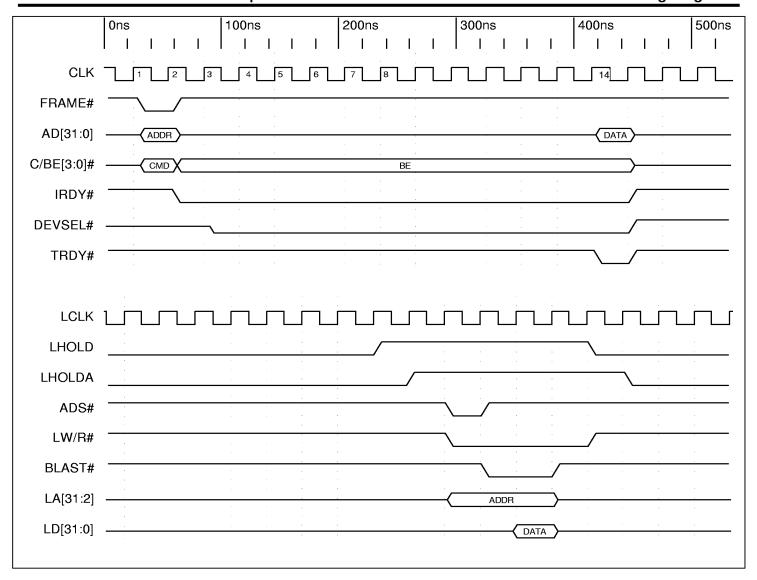

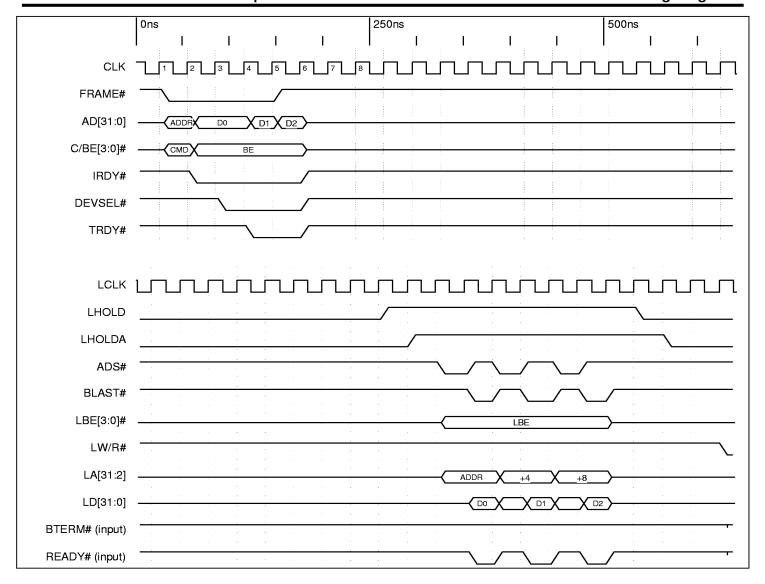

**Programmable Local Bus Modes.** The PCI 9054 is a PCI Bus Master interface chip that connects a PCI Bus to one of three Local Bus types (M, C, or J mode), selected through mode pins.

The PCI 9054 may be connected to any Local Bus with a similar design with little or no glue logic. Table 1-2 lists the three modes.

Table 1-2. Programmable Local Bus Modes

| Mo | de | Description                                                                              |

|----|----|------------------------------------------------------------------------------------------|

| N  | Л  | 32-bit address/32-bit data, non-multiplexed direct connect interface to MPC850 or MPC860 |

|    | )  | 32-bit address/32-bit data, non-multiplexed                                              |

|    | J  | 32-bit address/32-bit data, multiplexed                                                  |

**Clock.** The Local Bus interface runs from a Local clock to provide the necessary internal clocks. This clock runs asynchronously to the PCI clock.

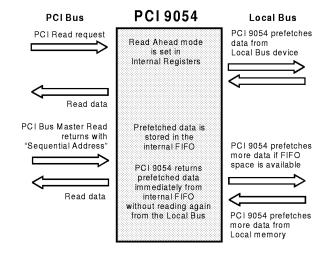

**Read Ahead Mode.** Supports Read Ahead mode, where prefetched data can be read from the PCI 9054 internal Direct Slave Read FIFO instead of from the Local Bus. The address must be subsequent to the previous address and 32-bit aligned (next address = current address + 4). This feature allows for increased bandwidth and reduced data latency.

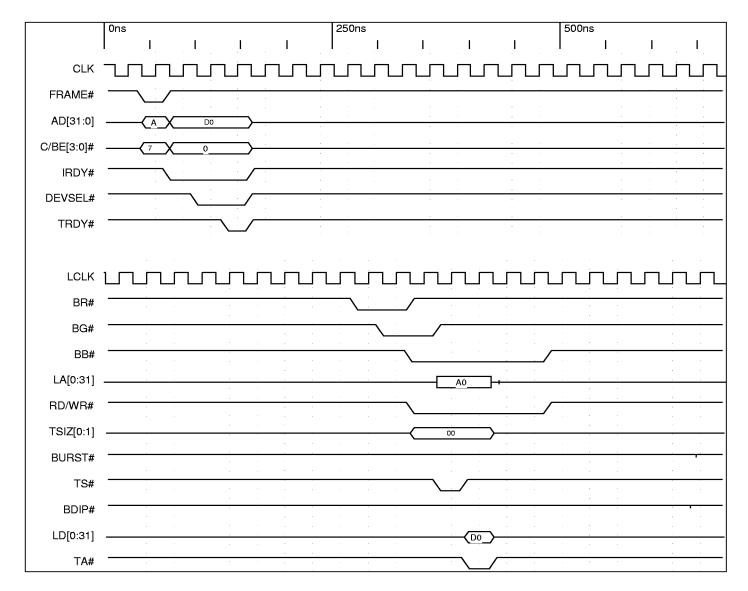

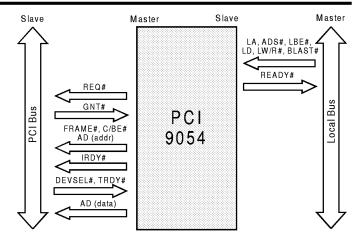

**M Mode of Operation.** The PCI 9054 is designed with a seamless interface to the Motorola MPC850 or MPC860 RISC processors. The PCI 9054 communicates with the MPC850 or MPC860 using five possible Data-Transfer modes:

- Configuration Register Access

- Direct Master Operation

- Direct Slave Operation

- DMA Operation

- IDMA/SDMA Operation

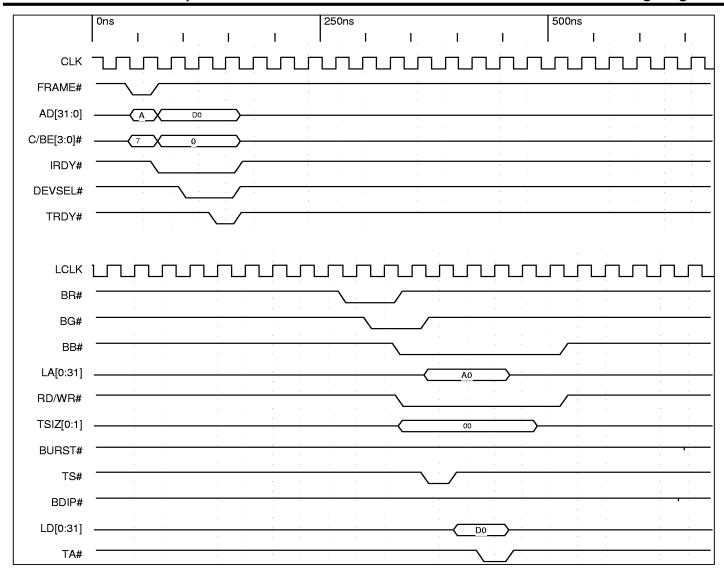

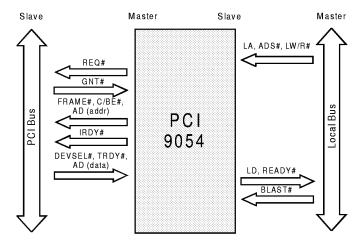

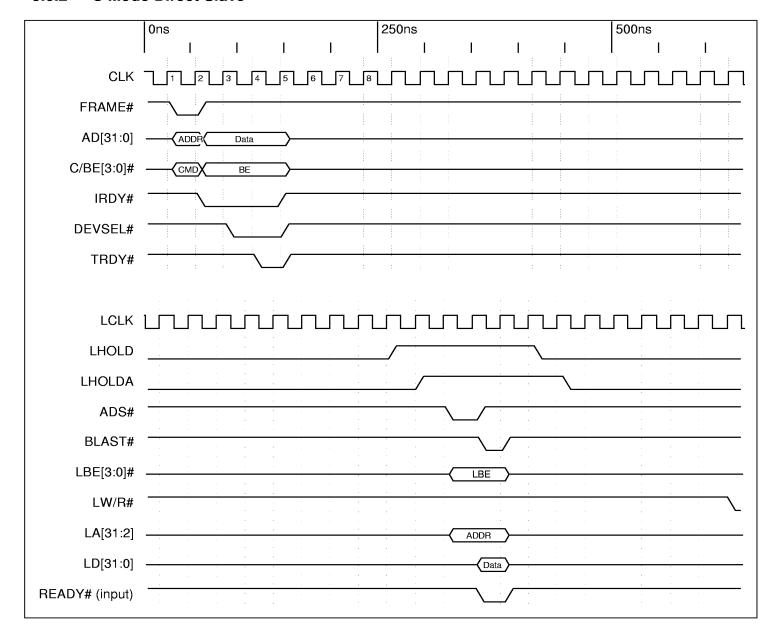

**C and J Modes of Operation.** The PCI 9054 is designed with a seamless interface to the Intel i960 and the IBM PPC401 family RISC processors. The PCI 9054 communicates with these processors using four possible Data-Transfer modes:

- Configuration Register Access

- Direct Master Operation

- Direct Slave Operation

- DMA Operation

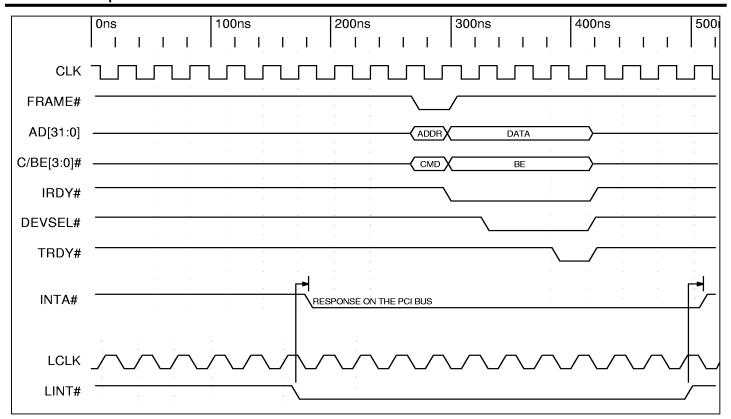

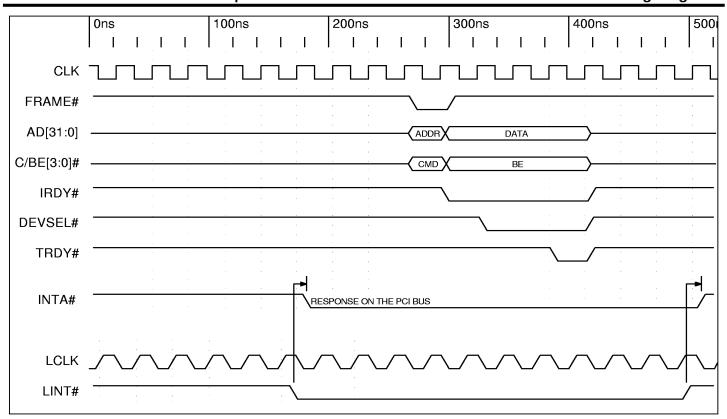

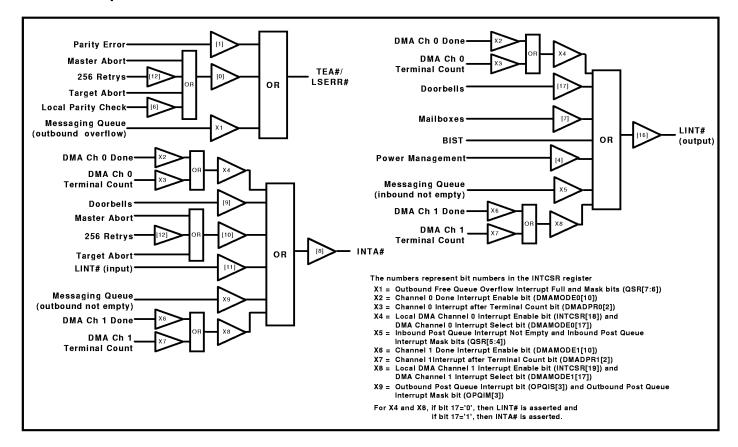

**Interrupt Generator.** Can assert PCI and Local interrupts from external and internal sources.

**Unaligned DMA Transfer Support.** Can transfer data on any byte-boundary combination of the PCI and Local Address spaces.

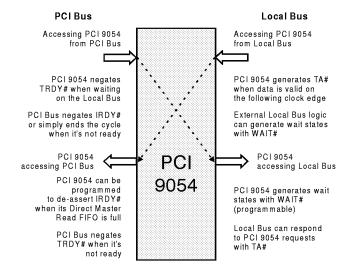

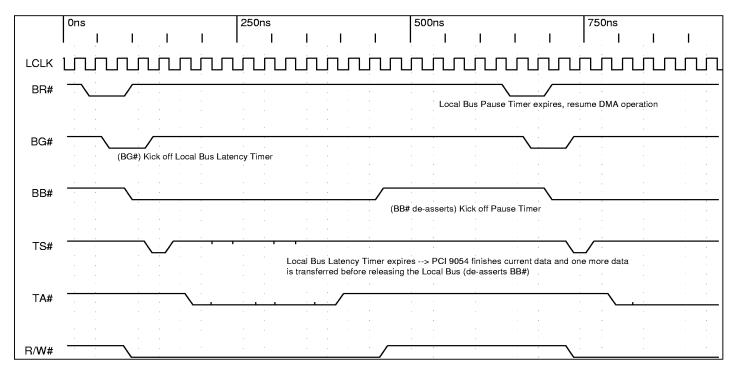

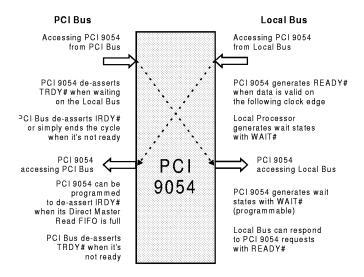

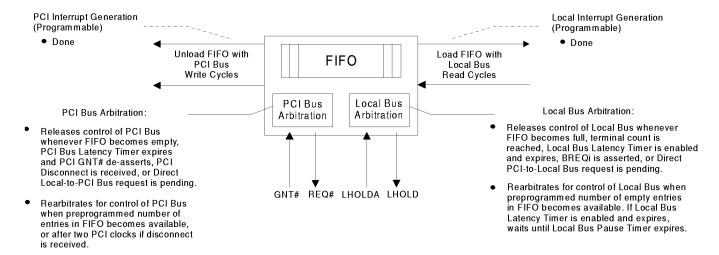

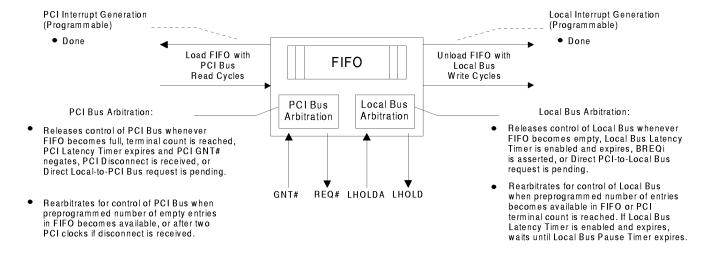

Keep Bus Mode (M Mode). The PCI 9054 can be programmed to keep the PCI Bus by generating wait state(s) if the Direct Master Write FIFO becomes full. The PCI 9054 can also be programmed to keep the Local Bus (BB# asserted) if the Direct Slave Write FIFO becomes empty or the Direct Slave Read FIFO becomes full. The Local Bus is dropped in either case when the Local Bus Latency Timer is enabled and expires.

Keep Bus Mode (C and J Modes). The PCI 9054 can be programmed to keep the PCI Bus by generating wait state(s) if the Direct Master Write FIFO becomes full. The PCI 9054 can also be programmed to keep the Local Bus (LHOLD asserted) if the Direct Slave Write FIFO becomes empty or the Direct Slave Read FIFO becomes full. The Local Bus is dropped in either case when the Local Bus Latency Timer is enabled and expires.

**New Capabilities Structure.** Supports New Capabilities registers to define additional capabilities of the PCI functions.

**Posted Memory Writes.** Supports the Posted Memory Writes (PMW) for maximum performance and to avoid potential deadlock situations.

**RST# Timing**. Supports response to first configuration accesses after de-assertion of RST# under 2<sup>25</sup> clocks.

**Subsystem ID and Subsystem Vendor ID.** Contains Subsystem ID and Subsystem Vendor ID in the PCI Configuration Register Space in addition to System and Vendor IDs. The PCI 9054 also contains a permanent Vendor ID (10B5h) and Device ID (9054h).

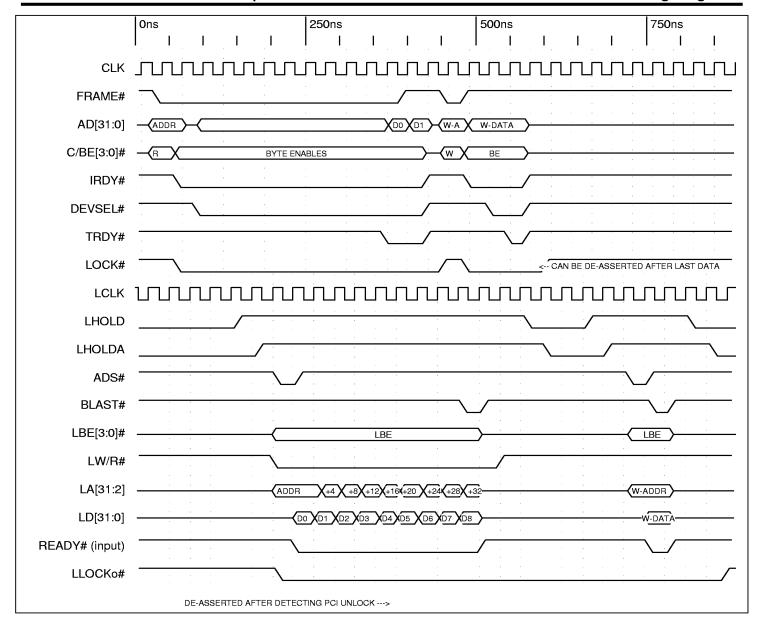

**Direct Bus Master.** Supports PCI accesses from a Local Bus Master. Burst transfers are supported for memory-mapped devices and single-transfers are supported for memory-mapped and I/O devices. The PCI 9054 also supports PCI Bus interlock (LOCK#) cycles.

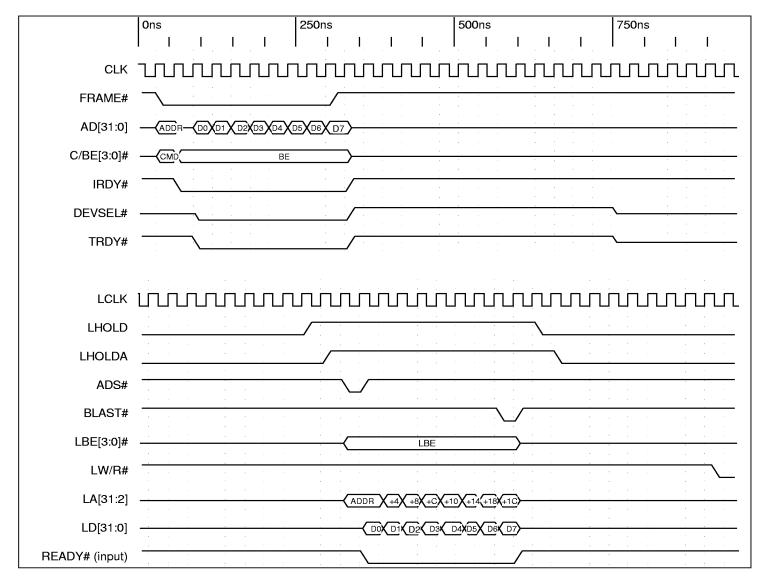

**Direct Slave.** Supports Burst Memory-Mapped and Single I/O-Mapped accesses to the Local Bus. The Read and Write FIFOs enable high-performance bursting.

# 1.5 PCI 9054 Data Assignment Convention

Table 1-3 describes the PCI 9054 data assignment convention.

Table 1-3. PCI 9054 Data Assignment Convention

| Data Width        | PCI 9054 Convention |

|-------------------|---------------------|

| 1 byte (8 bits)   | Byte                |

| 2 bytes (16 bits) | Word                |

| 4 bytes (32 bits) | Lword               |

## 1.6 PCI 9050/9080 Compatibility

## 1.6.1 Pin Compatibility

The PCI 9054 is *not* pin compatible with the PCI 9080 *nor* with the PCI 9050.

### 1.6.2 Register Compatibility

All registers implemented in the PCI 9080 are implemented in the PCI 9054. The PCI 9054 includes many new bit definitions and several new registers. Refer to Section 11.1 for details.

The PCI 9054 is **not** register-compatible with the PCI 9050.

## 1.7 PCI 9054, PCI 9080, and PCI 9050 Comparison

Table 1-4. Comparison of PCI 9054, PCI 9080, and PCI 9050

| Feature                                                                                               | PCI 9054                                                                                                       | PCI 9080                                                       | PCI 9050         |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------|

| Package Size/Type                                                                                     | 176 PQFP, 225 PBGA                                                                                             | 208 PQFP                                                       | 160 PQFP         |

| Number of DMA Channel(s)                                                                              | 2                                                                                                              | 2                                                              | 0                |

| Local Address Spaces                                                                                  | 3                                                                                                              | 3                                                              | 5                |

| Direct Master Mode                                                                                    | Yes                                                                                                            | Yes                                                            | No               |

| Mailbox Registers                                                                                     | Eight 32-bit                                                                                                   | Eight 32-bit                                                   | Eight 32 bit     |

| Doorbell Registers                                                                                    | Two 32-bit                                                                                                     | Two 32-bit                                                     | Two 32 bit       |

| Number of FIFOs                                                                                       | 6                                                                                                              | 8                                                              | _                |

| FIFO Depth—Direct Slave Write and Direct Master Write                                                 | 32 Lwords (128 bytes)                                                                                          | 32 Lwords (128 bytes)                                          | _                |

| FIFO Depth—Direct Slave Read and Direct Master Read                                                   | 16 Lwords (64 bytes)                                                                                           | 16 Lwords (64 bytes)                                           | 2                |

| FIFO Depth—DMA Channel 0                                                                              | 32 Lwords (128 bytes)<br>Single bidirectional<br>Read/Write FIFO                                               | 32 Lwords (128 bytes)<br>Read and Write FIFOs                  | N/A              |

| FIFO Depth—DMA Channel 1                                                                              | 16 Lwords<br>(64 bytes)<br>Single bidirectional<br>Read/Write FIFO                                             | 16 Lwords<br>(64 bytes)<br>Read and Write FIFOs                | N/A              |

| LLOCKo# Pin for Lock Cycles                                                                           | Yes                                                                                                            | Yes                                                            | Yes              |

| WAIT# Pin for Wait State Generation                                                                   | Yes                                                                                                            | Yes                                                            | No               |

| BPCLKo Pin; Buffered PCI Clock                                                                        | No                                                                                                             | Yes                                                            | Yes              |

| DREQ0# and DACK0# Pins for Demand Mode<br>DMA Support                                                 | Yes<br>(1 channel only)                                                                                        | Yes                                                            | No               |

| Register Addresses                                                                                    | Identical to the PCI 9080<br>except the PCI 9054 has<br>additional registers related<br>to added functionality | _                                                              | _                |

| Big Endian ⇔ Little Endian Conversion                                                                 | Yes                                                                                                            | Yes                                                            | Yes              |

| PCI Specification v2.1 Deferred Reads                                                                 | Yes                                                                                                            | Yes                                                            | Yes              |

| PCI Specification v2.2 PCI Power Management,<br>PCI Hot Plug Compliant, CompactPCI Hot Swap Compliant | Yes                                                                                                            | No                                                             | No               |

| PCI v2.2 VPD Support                                                                                  | Yes                                                                                                            | No                                                             | No               |

| Programmable Prefetch Counter                                                                         | Yes                                                                                                            | Yes                                                            | Yes              |

| Memory Write and Invalidate Cycle                                                                     | Yes                                                                                                            | Yes                                                            | No               |

| Additional Device and Vendor ID Registers                                                             | Yes                                                                                                            | Yes                                                            | No               |

| I <sub>2</sub> O Messaging Unit                                                                       | Yes                                                                                                            | Yes                                                            | No               |

| Core and Local Bus Vcc                                                                                | 3.3V                                                                                                           | 5V                                                             | 5V               |

| PCI Bus Vcc                                                                                           | 3.3V                                                                                                           | 3.3/5V                                                         | 5V               |

| 3.3V Tolerant PCI Bus and Local Bus Signaling                                                         | Yes                                                                                                            | Yes (if PCI Vcc is 3.3V)                                       | No               |

| 5V Tolerant PCI Bus and Local Bus Signaling                                                           | Yes                                                                                                            | Yes (if PCI Vcc is 5V)                                         | Yes              |

| Serial EEPROM Support                                                                                 | 2-kilobit, 4-kilobit devices                                                                                   | 1-kilobit, 2-kilobit devices                                   |                  |

| Serial EEPROM Read Control                                                                            | Reads allowed via Vital<br>Product Data Function<br>(refer to Section 10)                                      | Reads allowed via<br>Serial EEPROM<br>Control Register (CNTRL) | 1-kilobit device |

©PLX Technology, Inc., 1998 Page 8 Version 1.0

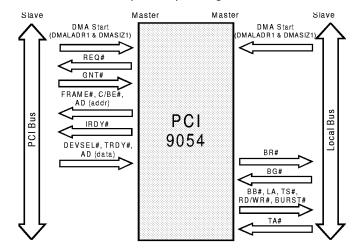

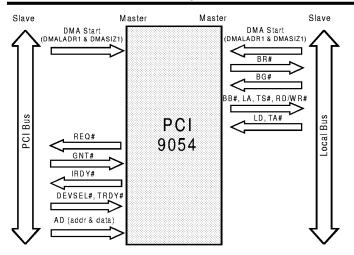

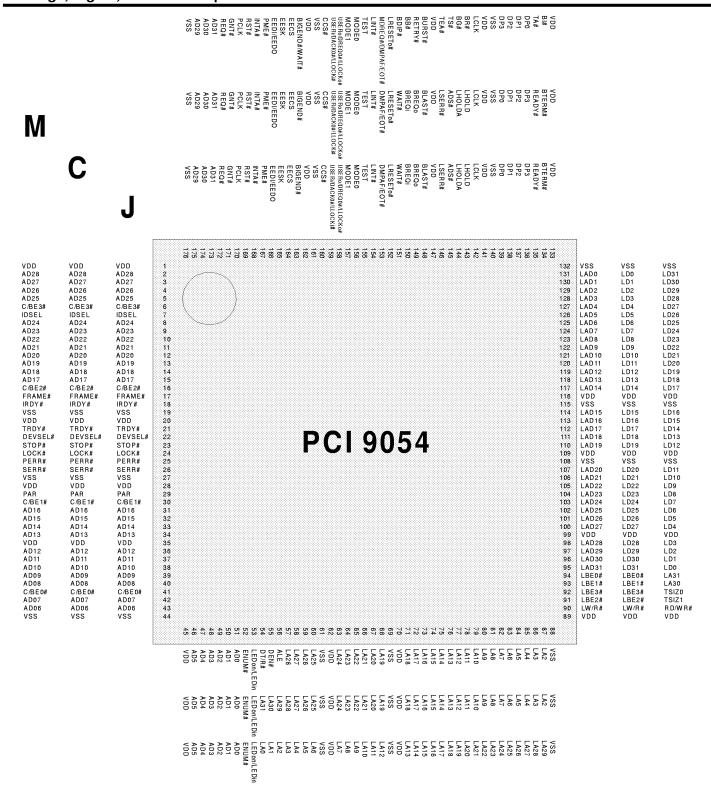

## 1.8 PCI 9054 Signal Listing (M, C, or J Modes)

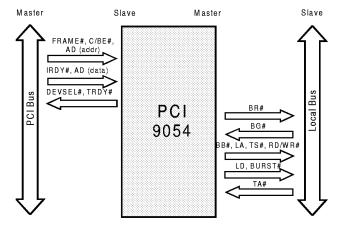

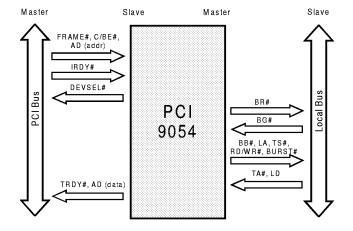

Table 1-5. PCI 9054 PCI Signal Listing (M, C, or J Modes)

| Symbol     | Bus<br>Mode | Signal Name                  | Total<br>Pins | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-------------|------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

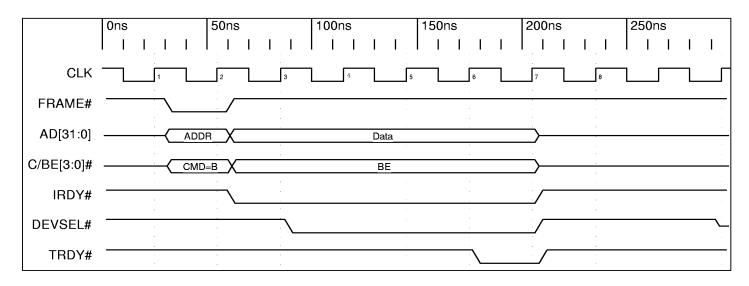

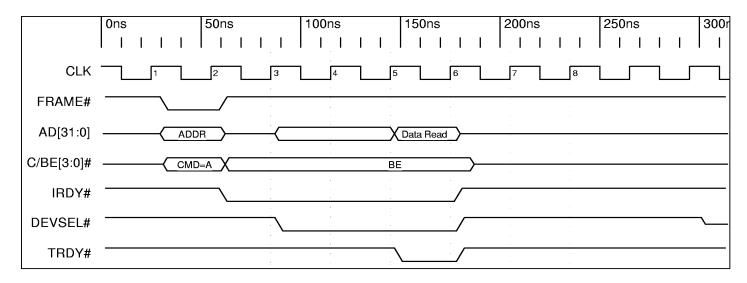

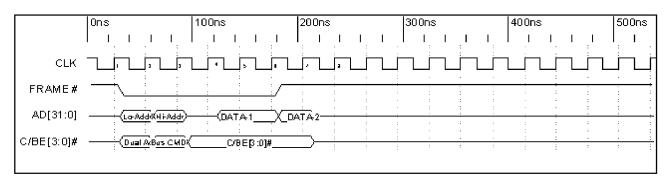

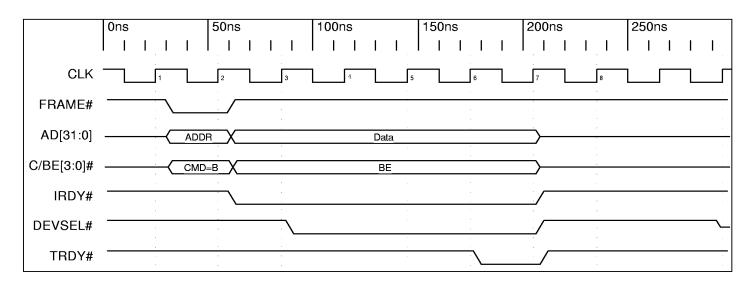

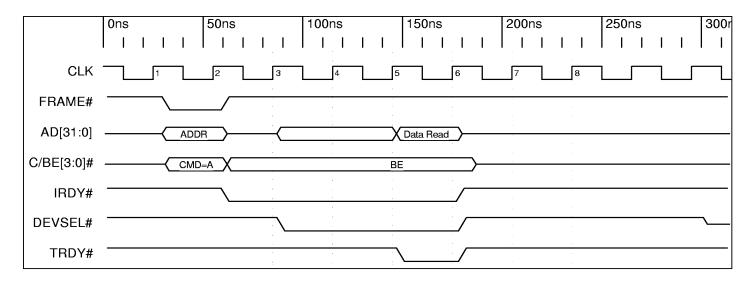

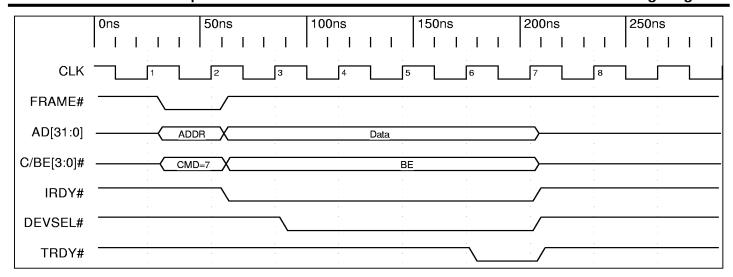

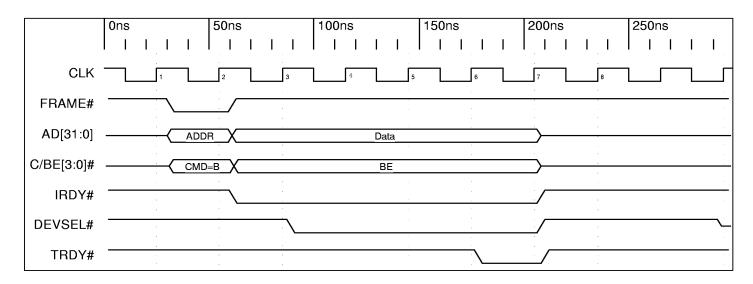

| AD[31:0]   | All         | Address and Data             | 32            | All multiplexed on the same PCI pins. The Bus transaction consists of an Address phase, followed by one or more Data phases. The PCI 9054 supports both Read and Write bursts.                                                                                                                                                                                                                |

| C/BE[3:0]# | All         | Bus Command and Byte Enables | 4             | All multiplexed on the same PCI pins. During the Address phase of a transaction, defines the bus command. During the Data phase, used as byte enables. Refer to the PCI spec for further detail if needed.                                                                                                                                                                                    |

| DEVSEL#    | All         | Device Select                | 1             | When actively driven, indicates the driving device has decoded its address as the Target of the current access. As an input, indicates whether any device on the bus is selected.                                                                                                                                                                                                             |

| FRAME#     | All         | Cycle Frame                  | 1             | Driven by the current Master to indicate beginning and duration of an access. FRAME# is asserted to indicate a bus transaction is beginning. While FRAME# is asserted, Data transfers continue. When FRAME# is de-asserted, the transaction is in the final Data phase.                                                                                                                       |

| GNT#       | All         | Grant                        | 1             | Indicates to the agent that access to the bus is granted. Every Master has its own REQ# and GNT#.                                                                                                                                                                                                                                                                                             |

| IDSEL      | All         | Initialization Device Select | 1             | Used as a chip select during Configuration Read and Write transactions.                                                                                                                                                                                                                                                                                                                       |

| INTA#      | All         | Interrupt A                  | 1             | PCI Interrupt request.                                                                                                                                                                                                                                                                                                                                                                        |

| IRDY#      | All         | Initiator Ready              | 1             | Indicates ability of the initiating agent (Bus Master) to complete the current Data phase of the transaction.                                                                                                                                                                                                                                                                                 |

| LOCK#      | All         | Lock                         | 1             | Indicates an atomic operation that may require multiple transactions to complete.                                                                                                                                                                                                                                                                                                             |

| PAR        | All         | Parity                       | 1             | Even parity across AD[31:0] and C/BE[3:0]#. All PCI agents require parity generation. PAR is stable and valid one clock after the Address phase. For Data phases, PAR is stable and valid one clock after either IRDY# is asserted on a Write transaction or TRDY# is asserted on a Read transaction. Once PAR is valid, it remains valid until one clock after current Data phase completes. |

| PCLK       | All         | Clock                        | 1             | Provides timing for all transactions on PCI and is an input to every PCI device. The PCI 9054 operates up to 33 MHz.                                                                                                                                                                                                                                                                          |

| PERR#      | All         | Parity Error                 | 1             | Reports data parity errors during all PCI transactions, except during a special cycle.                                                                                                                                                                                                                                                                                                        |

| PME#       | All         | Power Management Event       | 1             | Wake-up event interrupt.                                                                                                                                                                                                                                                                                                                                                                      |

| REQ#       | All         | Request                      | 1             | Indicates to arbiter that this agent must use the bus. Every Master has its own GNT# and REQ#.                                                                                                                                                                                                                                                                                                |

| RST#       | All         | Reset                        | 1             | Used to bring PCI-specific registers, sequencers, and signals to a consistent state.                                                                                                                                                                                                                                                                                                          |

| SERR#      | All         | Systems Error                | 1             | Reports address parity errors, data parity errors on the Special Cycle command, or any other system error where the result is catastrophic.                                                                                                                                                                                                                                                   |

| STOP#      | All         | Stop                         | 1             | Indicates the current Target is requesting that the Master stop the current transaction.                                                                                                                                                                                                                                                                                                      |

| TRDY#      | All         | Target Ready                 | 1             | Indicates ability of the Target agent (selected device) to complete the current Data phase of the transaction.                                                                                                                                                                                                                                                                                |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes)

| Symbol   | Bus<br>Mode | Signal Name                                                                         | Total<br>Pins | Function                                                                                                                                                                                                                                                                                                                |

|----------|-------------|-------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS#     | C, J        | Address Strobe                                                                      | 1             | Indicates valid address and start of new Bus access. Asserted for first clock of Bus access.                                                                                                                                                                                                                            |

| ALE      | J           | Address Latch Enable                                                                | 1             | Asserted during Address phase and de-asserted before Data phase and before next LCLK rising edge.                                                                                                                                                                                                                       |

| BB#      | М           | Bus Busy                                                                            | 1             | As an input, the PCI 9054 monitors this signal to determine whether an external Master has ended a Bus cycle.                                                                                                                                                                                                           |

|          |             |                                                                                     |               | As an output, the PCI 9054 asserts this signal after an external arbiter has granted ownership of the Local Bus and BB# is inactive from another Master.                                                                                                                                                                |

|          |             |                                                                                     |               | Signal requires an external pull-up resistor value of $510\Omega$ be applied to guarantee a fast transition to the inactive state when the PCI 9054 relinquishes ownership of the Local Bus.                                                                                                                            |

| BDIP#    | М           | Burst Data<br>in Progress                                                           | 1             | As an input, driven by the Bus Master during a Burst transaction. The Master de-asserts before the last Data phase on the bus.                                                                                                                                                                                          |

|          |             |                                                                                     |               | As an output, driven by the PCI 9054 during the Data phase of a Burst transaction. The PCI 9054 de-asserts before the last Burst Data phase on the bus.                                                                                                                                                                 |

| BG#      | М           | Bus Grant                                                                           | 1             | Asserted by the Local Bus arbiter in response to BR#. Indicates the requesting Master is next.                                                                                                                                                                                                                          |

| BI#      | М           | Burst Inhibit                                                                       | 1             | Whenever BR# is asserted, indicates that the Target device does not support Burst transactions.                                                                                                                                                                                                                         |

| BIGEND#/ | All         | Big Endian Select                                                                   | 1             | Multiplexed input/output pin.                                                                                                                                                                                                                                                                                           |

| WAIT#    | М           | WAIT input/output Select<br>(WAIT# is available at this location<br>only in M mode) |               | Can be asserted during the Local Bus Address phase of a Direct Master transfer or Configuration register access to specify use of Big Endian Byte ordering. Big Endian Byte order for Direct Master transfers or Configuration register accesses is also programmable through the Configuration registers.              |

|          |             |                                                                                     |               | If wait is selected, then PCI 9054 issues WAIT# when it is a Master on the Local Bus and has internal wait states setup. As a Slave, the PCI 9054 accepts WAIT# as an input from the Bus Master.                                                                                                                        |

| BLAST#   | C, J        | Burst Last                                                                          | 1             | Signal driven by the current Local Bus Master to indicate the last transfer in a Bus access.                                                                                                                                                                                                                            |

| BR#      | М           | Bus Request                                                                         | 1             | Asserted by the Master to request use of the Local Bus. The Local Bus arbiter asserts BG# when the Master is next in line for bus ownership.                                                                                                                                                                            |

| BREQi    | C, J        | Bus Request                                                                         | 1             | Asserted to indicate a Local Bus Master requires the bus. If enabled through the PCI 9054 Configuration registers, the PCI 9054 releases the bus during a DMA transfer if this signal is asserted.                                                                                                                      |

| BREQo    | C, J        | Bus Request Out                                                                     | 1             | Asserted to indicate the PCI 9054 requires the bus to perform a Direct Slave PCI-to-Local Bus access while a Direct Master access is pending on the Local Bus. Can be used with external logic to assert backoff to a Local Bus Master. Operational parameters are set up through the PCI 9054 Configuration registers. |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes) (continued)

| Symbol             | Bus<br>Mode | Signal Name                                            | Total<br>Pins | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-------------|--------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

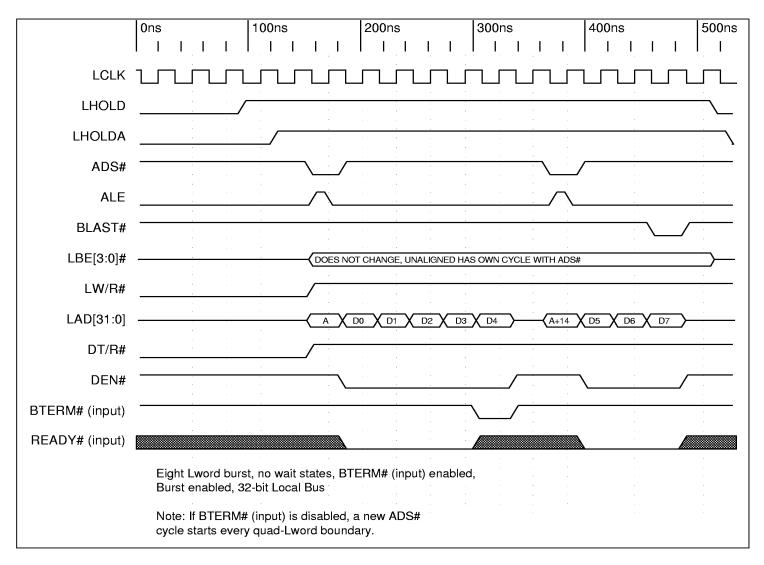

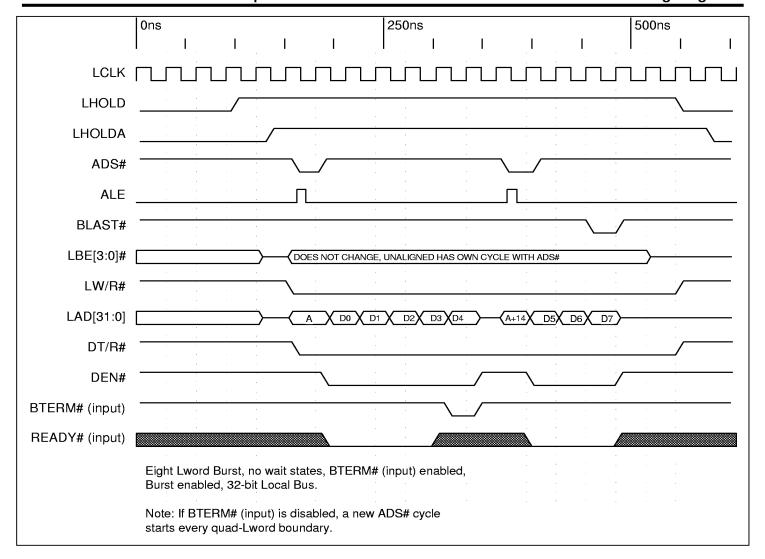

| BTERM#             | C, J        | Burst Terminate                                        | 1             | As input to the PCI 9054: For processors that burst up to four Lwords. If the Bterm Mode bit is disabled through the PCI 9054 Configuration registers, the PCI 9054 also bursts up to four Lwords. If enabled, the PCI 9054 continues to burst until a BTERM# input is asserted. BTERM# is a Ready input that breaks up a Burst cycle and causes another Address cycle to occur. Used in conjunction with the PCI 9054 programmable wait state generator. |

|                    |             |                                                        |               | As output from the PCI 9054: Asserted, along with READY#, to request break up of a burst and start of a new Address cycle (PCI Aborts only).                                                                                                                                                                                                                                                                                                              |

| BURST#             | М           | Burst                                                  | 1             | As an input, driven by the Master along with address and data indicating a Burst transfer is in progress.                                                                                                                                                                                                                                                                                                                                                 |

|                    |             |                                                        |               | As an output, driven by the PCI 9054 along with address and data indicating a Burst transfer is in progress.                                                                                                                                                                                                                                                                                                                                              |

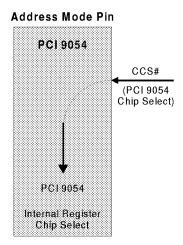

| CCS#               | All         | Configuration Register Select                          | 1             | Internal PCI 9054 registers are selected when CCS# is asserted low.                                                                                                                                                                                                                                                                                                                                                                                       |

| DACK0#             | All         |                                                        |               | See USERi/DACK0#/LLOCKi#.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DEN#               | J           | Data Enable                                            | 1             | Used in conjunction with DT/R# to provide control for data transceivers attached to the Local Bus.                                                                                                                                                                                                                                                                                                                                                        |

| DMPAF              | All         |                                                        |               | See MDREQ#/DMPAF/EOT#.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DP[0:3]<br>DP[3:0] | M<br>C, J   | Data Parity                                            | 4             | Parity is even for each of up to four byte lanes on the Local Bus. Parity is checked for writes or reads to the PCI 9054. Parity is asserted for reads from or writes by the PCI 9054.                                                                                                                                                                                                                                                                    |

| DREQ0#             | All         |                                                        |               | See USERo/DREQ0#/LLOCKo#.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DT/R#              | J           | Data Transmit/Receive                                  | 1             | Used in conjunction with DEN# to provide control for data transceivers attached to the Local Bus. When asserted, indicates the PCI 9054 receives data.                                                                                                                                                                                                                                                                                                    |

| EECS               | All         | Serial EEPROM Chip Select                              | 1             | Serial EEPROM Chip Select.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EEDI/EEDO          | All         | Serial EEPROM<br>Data IN/<br>Serial EEPROM<br>Data OUT | 1             | Multiplexed Write/Read data to serial EEPROM pin.                                                                                                                                                                                                                                                                                                                                                                                                         |

| EESK               | All         | Serial DataClock                                       | 1             | Serial EEPROM clock pin.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ENUM#              | All         | Enumeration                                            | 1             | Interrupt output asserted when an adapter using PCI 9054 has been freshly inserted or is ready to be removed from a PCI slot.                                                                                                                                                                                                                                                                                                                             |

| EOT#               | All         |                                                        |               | See MDREQ#/DMPAF/EOT#.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes) (continued)

| Symbol    | Bus<br>Mode | Signal Name       | Total<br>Pins | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LA[28:2]  | J           | Local Address Bus | 27            | Carries the middle 27 bits of the physical address bus. During bursts, it is incremented to indicate successive Data cycles. The lowest two bits, LA[3:2], carry the Word address of the 32-bit Memory address. All bits are incremented during a Burst access.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LA[0:31]  | М           | Address Bus       | 32            | Carries the 32 bits of the physical Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LA[31:2]  | С           | Address Bus       | 30            | Carries the upper 30 bits of physical Address Bus. During bursts, LA[31:2] increment to indicate successive Data cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LAD[31:0] | J           | Address/Data Bus  | 32            | During an Address phase, the bus carries the upper 30 bits of the physical Address Bus. During a Data phase, the bus carries 32 bits of data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LBE[3:0]# | C           | Byte Enables      | 4             | Encoded, based on the bus-width configuration, as follows:  32-Bit Bus: The four byte enables indicate which of the four bytes are active during a Data cycle:  BE3# Byte Enable 3—LD[31:24] BE2# Byte Enable 2—LD[23:16] BE1# Byte Enable 1—LD[15:8] BE0# Byte Enable 0—LD[7:0]  16-Bit Bus: BE3#, BE1# and BE0# are encoded to provide BHE#, LA1, and BLE#, respectively:  BE3# Byte High Enable (BHE#)—LD[15:8] BE2# not used BE1# Address bit 1 (LA1) BE0# Byte Low Enable (BLE#)—LD[7:0]  8-Bit Bus: BE1# and BE0# are encoded to provide LA1 and LA0, respectively:  BE3# not used BE2# not used BE2# not used BE1# Address bit 1 (LA1) BE0# Address bit 1 (LA1) BE0# Address bit 0 (LA0) |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes) (continued)

| Symbol          | Bus<br>Mode | Signal Name                | Total<br>Pins | Function                                                                                                                                                                                                                                                                                              |

|-----------------|-------------|----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LBE[3:0]#       | J           | Byte Enables               | 4             | Encoded, based on the bus-width configuration, as follows:                                                                                                                                                                                                                                            |

|                 |             |                            |               | 32-Bit Bus: The four byte enables indicate which of the four bytes are active during a Data cycle:                                                                                                                                                                                                    |

|                 |             |                            |               | BE3# Byte Enable 3—LAD[31:24]<br>BE2# Byte Enable 2—LAD[23:16]<br>BE1# Byte Enable 1—LAD[15:8]<br>BE0# Byte Enable 0—LAD[7:0]                                                                                                                                                                         |

|                 |             |                            |               | 16-Bit Bus: BE3#, BE1# and BE0# are encoded to provide BHE#, LAD1, and BLE#, respectively:                                                                                                                                                                                                            |

|                 |             |                            |               | BE3# Byte High Enable (BHE#)—LAD[15:8]<br>BE2# not used<br>BE1# Address bit 1 (LAD1)<br>BE0# Byte Low Enable (BLE#)—LAD[7:0]                                                                                                                                                                          |

|                 |             |                            |               | 8-Bit Bus: BE1# and BE0# are encoded to provide LAD1 and LAD0, respectively:                                                                                                                                                                                                                          |

|                 |             |                            |               | BE3# not used<br>BE2# not used<br>BE1# Address bit 1 (LAD1)<br>BE0# Address bit 0 (LAD0)                                                                                                                                                                                                              |

| LCLK            | All         | Local processor Clock      | 1             | Local clock input.                                                                                                                                                                                                                                                                                    |

| LD[0:31]        | М           | Data Bus                   | 32            | Carries 8-, 16-, or 32-bit data quantities, depending upon bus-width                                                                                                                                                                                                                                  |

| LD[31:0]        | С           |                            |               | configuration. All Master accesses to the PCI 9054 are 32 bits only.                                                                                                                                                                                                                                  |

| LEDon/<br>LEDin | All         | LEDon/LEDin                | 1             | As an output, acts as the Hot Swap board indicator LED. As an input, monitors the CompactPCI board latch status.                                                                                                                                                                                      |

| LFRAME#         | All         | PCI Buffered FRAME# Signal | 1             | Could be used to monitor PCI Bus activity. Available only on the PBGA package.                                                                                                                                                                                                                        |

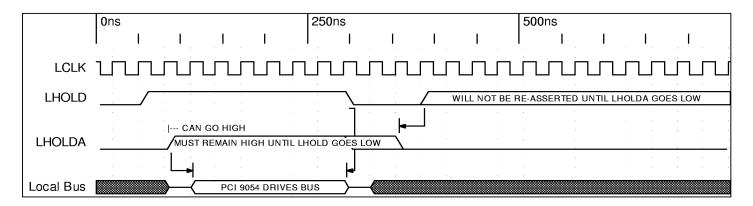

| LHOLD           | C, J        | Hold Request               | 1             | Asserted to request use of the Local Bus. The Local Bus arbiter asserts LHOLDA when control is granted.                                                                                                                                                                                               |

| LHOLDA          | C, J        | Hold Acknowledge           | 1             | Asserted by the Local Bus arbiter when control is granted in response to LHOLD. Bus should not be granted to the PCI 9054 unless requested by LHOLD.                                                                                                                                                  |

| LINT#           | All         | Local Interrupt            | 1             | As an input to the PCI 9054, when asserted low, causes a PCI interrupt.                                                                                                                                                                                                                               |

|                 |             |                            |               | As an output, a synchronous level output that remains asserted as long as an interrupt condition exists. If edge level interrupt is required, disabling and then enabling Local interrupts through INTCSR creates an edge if an interrupt condition still exists or a new interrupt condition occurs. |

| LLOCKi#         | All         |                            |               | See USERi/DACK0#/LLOCKi#.                                                                                                                                                                                                                                                                             |

| LLOCKo#         | All         |                            |               | See USERo/DREQ0#/LLOCKo#.                                                                                                                                                                                                                                                                             |

| LRESETo#        | All         | Local Bus Reset Out        | 1             | Asserted when the PCI 9054 chip is reset. Can be used to drive RESET# input of a Local processor.                                                                                                                                                                                                     |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes) (continued)

| Symbol    | Bus<br>Mode | Signal Name                                                                            | Total<br>Pins | Function                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------|----------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSERR#    | C, J        | System Error<br>Interrupt Output                                                       | 1             | Synchronous level output asserted when the PCI Bus Target Abort bit is set (PCISR[11]=1) or Received Master Abort bit is set (PCISR[13]=1). If edge level interrupt is required, disabling and then enabling LSERR# interrupts through the interrupt/control status creates an edge if an interrupt condition still exists or a new interrupt condition occurs. |

| LW/R#     | C, J        | Write/Read                                                                             | 1             | Asserted low for reads and high for writes.                                                                                                                                                                                                                                                                                                                     |

| MDREQ#/   | М           | IDMA Data Transfer Request<br>(MDREQ# is available at this<br>location in M mode only) | 1             | Multiplexed input or output pin.  MDREQ#: IDMA M mode Data transfer request start. Always asserted, indicating Data transfer should start. De-asserted only when the Direct Master FIFO becomes full. Programmable through a Configuration register.                                                                                                            |

| DMPAF/    | All         | Direct Master Programmable<br>Almost Full                                              |               | DMPAF: Direct Master Write FIFO Almost Full status output. Programmable through a Configuration register.                                                                                                                                                                                                                                                       |

| EOT#      | All         | End of Transfer for Current<br>DMA Channel                                             |               | EOT#: Terminates the current DMA transfer.  Note: EOT# serves as a general purpose EOT. Before asserting EOT#, user should be aware of DMA channel activity.                                                                                                                                                                                                    |

| MODE[1:0] | All         | Bus Mode                                                                               | 2             | Selects the PCI 9054 bus operation mode:           Mode 0         Mode 1         Bus Mode           1         1         M           1         0         J           0         1         Reserved           0         0         C                                                                                                                                |

| RD/WR#    | М           | Read/Write                                                                             | 1             | Asserted high for reads and low for writes.                                                                                                                                                                                                                                                                                                                     |

| READY#    | C, J        | Ready Input/Output                                                                     | 1             | When the PCI 9054 is a Bus Master, indicates that Read data on the bus is valid or that a Write Data transfer is complete. Used in conjunction with the PCI 9054 programmable wait state generator. When a Local Bus access is made to the PCI 9054, indicates that Read data on the bus is valid or that a Write Data transfer is complete.                    |

| RETRY#    | М           | Retry                                                                                  | 1             | Driven by the PCI 9054 when it is a Slave to indicate a Local Master must back off and restart the cycle. In Deferred Read mode, indicates the Master should return for requested data.                                                                                                                                                                         |

Table 1-6. PCI 9054 Local Signal Listing (M, C, or J Modes) (continued)

| Symbol    | Bus<br>Mode | Signal Name                 | Total<br>Pins | Function                                                                                                                                                                                             |

|-----------|-------------|-----------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TA#       | М           | Transfer Acknowledge        | 1             | As an input, when a Local Bus access is made to the PCI 9054, indicates a Write Data transfer can complete or that Read data on the bus is valid.                                                    |

|           |             |                             |               | As an output, when the PCI 9054 is a Bus Master, indicates a Write<br>Data transfer is complete or that Read data on the bus is valid.                                                               |

| TEA#      | М           | Transfer Error Acknowledge  | 1             | Driven by the Target device, indicating an error condition has occurred during a Bus cycle.                                                                                                          |

| TEST      | All         | Test Pin                    | 1             | Pulled high for test and low for normal operation.                                                                                                                                                   |

|           |             |                             |               | When pulled high: All outputs except USERo/DREQ0#/LLOCKo# and LEDon/LEDin are placed in tri-state. USERo/DREQ0#/LLOCKo# provide NANDTREE output.                                                     |

| TS#       | М           | Address Strobe              | 1             | Indicates the valid address and start of new Bus access. Asserted for the first clock of a Bus access.                                                                                               |

| TSIZ[0:1] | М           | Transfer Size               | 2             | Driven by current Master along with the address, indicating the data-transfer size. Refer to Section 3.4.3.5.3 for more information.                                                                 |

|           | All         |                             | 1             | Multiplexed input/output pin.                                                                                                                                                                        |

| USERi/    |             | User Input                  |               | USERi:<br>General-purpose input that can be read by way of the PCI 9054<br>Configuration registers.                                                                                                  |

| DACK0#/   |             | Demand Mode DMA Acknowledge |               | DACK0#: When a channel is programmed through the Configuration registers to operate in Demand mode, this output indicates a DMA transfer is being executed. DACK0# corresponds to PCI 9054 DMA Ch 0. |

| LLOCKi#   |             | Local Lock Input            |               | LLOCKi#: Indicates an atomic operation that may require multiple transactions to complete. Used by the PCI 9054 for direct Local access to the PCI Bus.                                              |

|           | All         |                             | 1             | Multiplexed input/output pin.                                                                                                                                                                        |