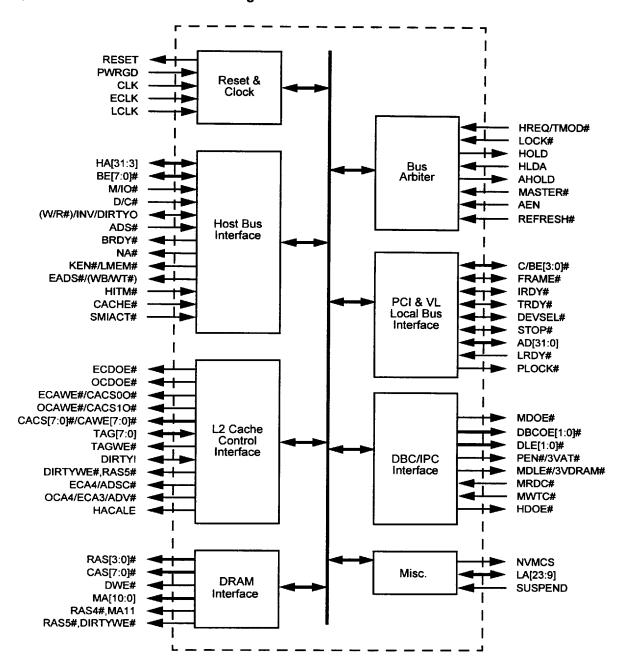

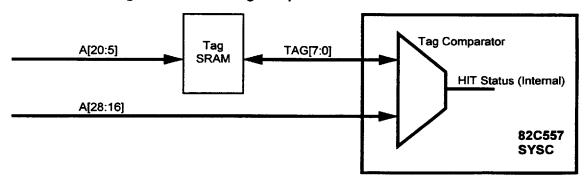

Figure 2-3 82C557 SYSC Block Diagram

Page 4

912-3000-023

**==** 9004196 0000278 918 **==**

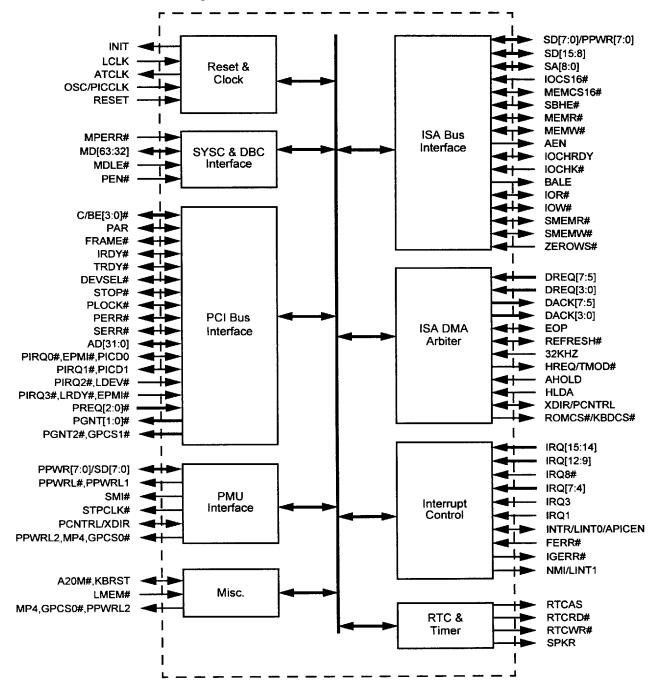

Figure 2-4 82C558 IPC Block Diagram

912-3000-023

Page 5

**9004196 0000279 854**

## 3.0 Signal Definitions

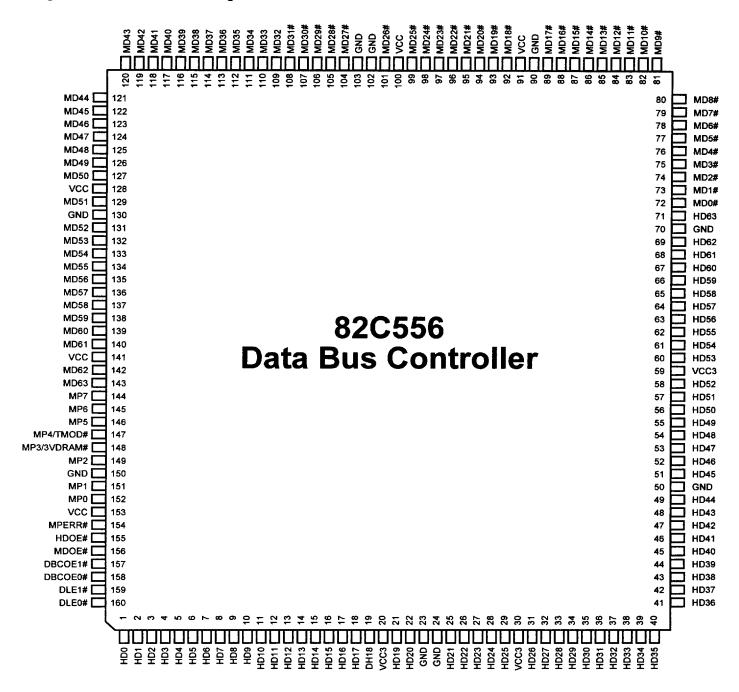

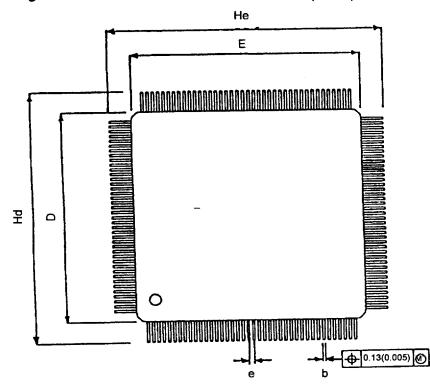

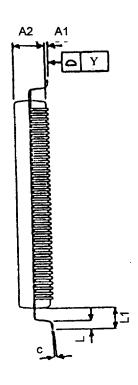

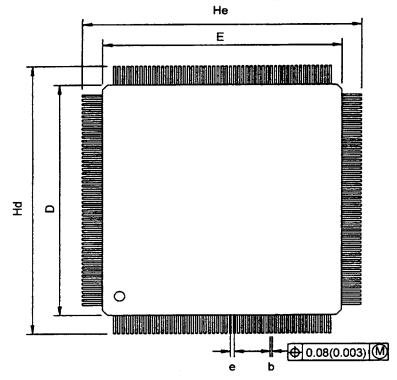

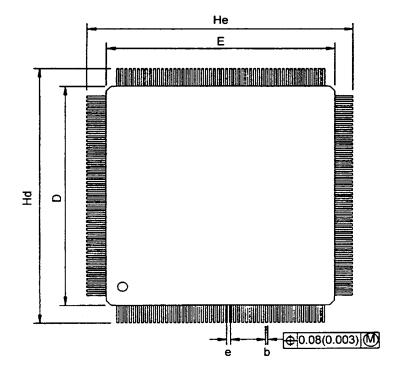

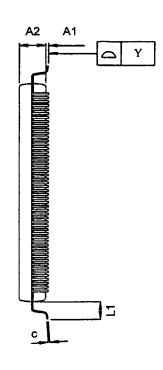

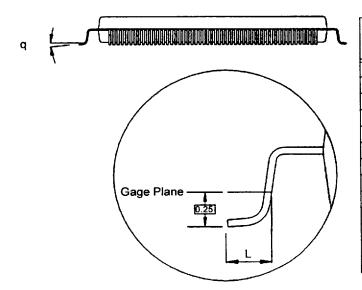

Figure 3-1 82C556 Pin Diagram

Page 6

912-3000-023

9004196 0000280 576

Table 3-1 82C556 160-Pin Numerical Pin Cross-Reference List

| Pin No. | Pin Name |

|---------|----------|

| 1       | HD0      |

| 2       | HD1      |

| 3       | HD2      |

| 4       | HD3      |

| 5       | HD4      |

| 6       | HD5      |

| 7       | HD6      |

| 8       | HD7      |

| 9       | HD8      |

| 10      | HD9      |

| 11      | HD10     |

| 12      | HD11     |

| 13      | HD12     |

| 14      | HD13     |

| 15      | HD14     |

| 16      | HD15     |

| 17      | HD16     |

| 18      | HD17     |

| 19      | HD18     |

| 20      | VCC3     |

| 21      | HD19     |

| 22      | HD20     |

| 23      | GND      |

| 24      | GND      |

| 25      | HD21     |

| 26      | HD22     |

| 27      | HD23     |

| 28      | HD24     |

| 29      | HD25     |

| 30      | VCC3     |

| 31      | HD26     |

| 32      | HD27     |

| 33      | HD28     |

| 34      | HD29     |

| 35      | HD30     |

| 36      | HD31     |

| 37      | HD32     |

| 38      | HD33     |

| 39      | HD34     |

| 40      | HD35     |

| Pin No. | Pin Name |

|---------|----------|

| 41      | HD36     |

| 42      | HD37     |

| 43      | HD38     |

| 44      | HD39     |

| 45      | HD40     |

| 46      | HD41     |

| 47      | HD42     |

| 48      | HD43     |

| 49      | HD44     |

| 50      | GND      |

| 51      | HD45     |

| 52      | HD46     |

| 53      | HD47     |

| 54      | HD48     |

| 55      | HD49     |

| 56      | HD50     |

| 57      | HD51     |

| 58      | HD52     |

| 59      | VCC3     |

| 60      | HD53     |

| 61      | HD54     |

| 62      | HD55     |

| 63      | HD56     |

| 64      | HD57     |

| 65      | HD58     |

| 66      | HD59     |

| 67      | HD60     |

| 68      | HD61     |

| 69      | HD62     |

| 70      | GND      |

| 71      | HD63     |

| 72      | MD0#     |

| 73      | MD1#     |

| 74      | MD2#     |

| 75      | MD3#     |

| 76      | MD4#     |

| 77      | MD5#     |

| 78      | MD6#     |

| 79      | MD7#     |

|         | i .      |

MD8#

| Pin No. | Pin Name |

|---------|----------|

| 81      | MD9#     |

| 82      | MD10#    |

| 83      | MD11#    |

| 84      | MD12#    |

| 85      | MD13#    |

| 86      | MD14#    |

| 87      | MD15#    |

| 88      | MD16#    |

| 89      | MD17#    |

| 90      | GND      |

| 91      | VCC      |

| 92      | MD18#    |

| 93      | MD19#    |

| 94      | MD20#    |

| 95      | MD21#    |

| 96      | MD22#    |

| 97      | MD23#    |

| 98      | MD24#    |

| 99      | MD25#    |

| 100     | vcc      |

| 101     | MD26#    |

| 102     | GND      |

| 103     | GND      |

| 104     | MD27#    |

| 105     | MD28#    |

| 106     | MD29#    |

| 107     | MD30#    |

| 108     | MD31#    |

| 109     | MD32     |

| 110     | MD33     |

| 111     | MD34     |

| 112     | MD35     |

| 113     | MD36     |

| 114     | MD37     |

| 115     | MD38     |

| 116     | MD39     |

| 117     | MD40     |

| 118     | MD41     |

| 119     | MD42     |

| 120     | MD43     |

| Pin No. | Pin Name    |

|---------|-------------|

| 121     | MD44        |

| 122     | MD45        |

| 123     | MD46        |

| 124     | MD47        |

| 125     | MD48        |

| 126     | MD49        |

| 127     | MD50        |

| 128     | VCC         |

| 129     | MD51        |

| 130     | GND         |

| 131     | MD52        |

| 132     | MD53        |

| 133     | MD54        |

| 134     | MD55        |

| 135     | MD56        |

| 136     | MD57        |

| 137     | MD58        |

| 138     | MD59        |

| 139     | MD60        |

| 140     | MD61        |

| 141     | VCC         |

| 142     | MD62        |

| 143     | MD63        |

| 144     | MP7         |

| 145     | MP6         |

| 146     | MP5         |

| 147     | MP4/TMOD#   |

| 148     | MP3/3VDRAM# |

| 149     | MP2         |

| 150     | GND         |

| 151     | MP1         |

| 152     | MP0         |

| 153     | vcc         |

| 154     | MPERR#      |

| 155     | HDOE#       |

| 156     | MDOE#       |

| 157     | DBCOE1#     |

| 158     | DBCOE0#     |

| 159     | DLE1#       |

| 160     | DLE0#       |

912-3000-023

**= 9004196 0000281 402 =**

Table 3-2 82C556 160-Pin Alphabetical Cross-Reference List

| Pin No. | Pin Name    |

|---------|----------|---------|----------|---------|----------|---------|-------------|

| 158     | DBCOE0#  | 32      | HD27     | 74      | MD2#     | 119     | MD42        |

| 157     | DBCOE1#  | 33      | HD28     | 75      | MD3#     | 120     | MD43        |

| 160     | DLE0#    | 34      | HD29     | 76      | MD4#     | 121     | MD44        |

| 159     | DLE1#    | 35      | HD30     | 77      | MD5#     | 122     | MD45        |

| 23      | GND      | 36      | HD31     | 78      | MD6#     | 123     | MD46        |

| 24      | GND      | 37      | HD32     | 79      | MD7#     | 124     | MD47        |

| 50      | GND      | 38      | HD33     | 80      | MD8#     | 125     | MD48        |

| 70      | GND      | 39      | HD34     | 81      | MD9#     | 126     | MD49        |

| 90      | GND      | 40      | HD35     | 82      | MD10#    | 127     | MD50        |

| 102     | GND      | 41      | HD36     | 83      | MD11#    | 129     | MD51        |

| 103     | GND      | 42      | HD37     | 84      | MD12#    | 131     | MD52        |

| 130     | GND      | 43      | HD38     | 85      | MD13#    | 132     | MD53        |

| 150     | GND      | 44      | HD39     | 86      | MD14#    | 133     | MD54        |

| 1       | HD0      | 45      | HD40     | 87      | MD15#    | 134     | MD55        |

| 2       | HD1      | 46      | HD41     | 88      | MD16#    | 135     | MD56        |

| 3       | HD2      | 47      | HD42     | 89      | MD17#    | 136     | MD57        |

| 4       | HD3      | 48      | HD43     | 92      | MD18#    | 137     | MD58        |

| 5       | HD4      | 49      | HD44     | 93      | MD19#    | 138     | MD59        |

| 6       | HD5      | 51      | HD45     | 94      | MD20#    | 139     | MD60        |

| 7       | HD6      | 52      | HD46     | 95      | MD21#    | 140     | MD61        |

| 8       | HD7      | 53      | HD47     | 96      | MD22#    | 142     | MD62        |

| 9       | HD8      | 54      | HD48     | 97      | MD23#    | 143     | MD63        |

| 10      | HD9      | 55      | HD49     | 98      | MD24#    | 156     | MDOE#       |

| 11      | HD10     | 56      | HD50     | 99      | MD25#    | 152     | MP0         |

| 12      | HD11     | 57      | HD51     | 101     | MD26#    | 151     | MP1         |

| 13      | HD12     | 58      | HD52     | 104     | MD27#    | 149     | MP2         |

| 14      | HD13     | 60      | HD53     | 105     | MD28#    | 148     | MP3/3VDRAM# |

| 15      | HD14     | 61      | HD54     | 106     | MD29#    | 147     | MP4/TMOD#   |

| 16      | HD15     | 62      | HD55     | 107     | MD30#    | 146     | MP5         |

| 17      | HD16     | 63      | HD56     | 108     | MD31#    | 145     | MP6         |

| 18      | HD17     | 64      | HD57     | 109     | MD32     | 144     | MP7         |

| 19      | HD18     | 65      | HD58     | 110     | MD33     | 154     | MPERR#      |

| 21      | HD19     | 66      | HD59     | 111     | MD34     | 153     | vcc         |

| 22      | HD20     | 67      | HD60     | 112     | MD35     | 91      | vcc         |

| 25      | HD21     | 68      | HD61     | 113     | MD36     | 100     | vcc         |

| 26      | HD22     | 69      | HD62     | 114     | MD37     | 128     | VCC         |

| 27      | HD23     | 71      | HD63     | 115     | MD38     | 141     | VCC         |

| 28      | HD24     | 155     | HDOE#    | 116     | MD39     | 20      | VCC3        |

| 29      | HD25     | 72      | MD0#     | 117     | MD40     | 30      | VCC3        |

| 31      | HD26     | 73      | MD1#     | 118     | MD41     | 59      | VCC3        |

Page 8

912-3000-023

■ 9004196 0000282 349 ■

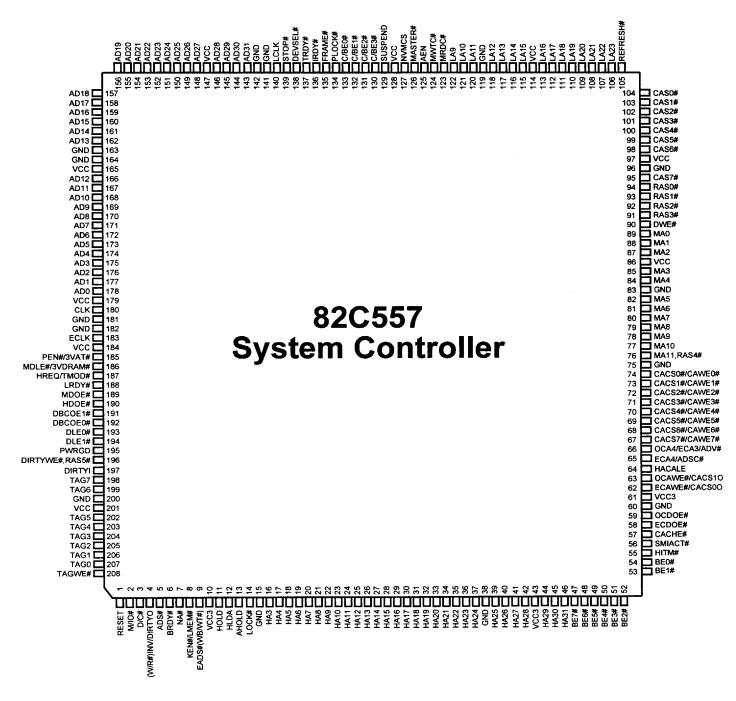

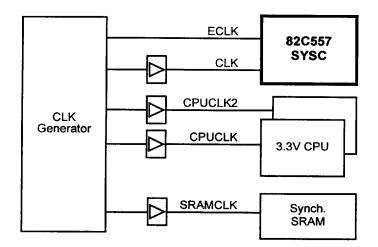

Figure 3-2 82C557 SYSC Pin Diagram

912-3000-023

Page 9

■ 900419b 0000283 285 ■

Table 3-3 82C557 Numerical Pin Cross-Reference List

| Pin No. | Pin Name          | Pin No. | Pin Name       | Pin No. | Pin Name | Pin No. | Pin Name       |

|---------|-------------------|---------|----------------|---------|----------|---------|----------------|

| 1       | RESET             | 53      | BE1#           | 105     | REFRESH# | 157     | AD18           |

| 2       | M/IO#             | 54      | BE0#           | 106     | LA23     | 158     | AD17           |

| 3       | D/C#              | 55      | HITM#          | 107     | LA22     | 159     | AD16           |

| 4       | (W/R#)/INV/DIRTYO | 56      | SMIACT#        | 108     | LA21     | 160     | AD15           |

| 5       | ADS#              | 57      | CACHE#         | 109     | LA20     | 161     | AD14           |

| 6       | BRDY#             | 58      | ECDOE#         | 110     | LA19     | 162     | AD13           |

| 7       | NA#               | 59      | OCDOE#         | 111     | LA18     | 163     | GND            |

| 8       | KEN#/LMEM#        | 60      | GND            | 112     | LA17     | 164     | GND            |

| 9       | EADS#/(WB/WT#)    | 61      | VCC3           | 113     | LA16     | 165     | vcc            |

| 10      | VCC3              | 62      | ECAWE#/CACS0O# | 114     | VCC      | 166     | AD12           |

| 11      | HOLD              | 63      | OCAWE#/CACS1O# | 115     | LA15     | 167     | AD11           |

| 12      | HLDA              | 64      | HACALE         | 116     | LA14     | 168     | AD10           |

| 13      | AHOLD             | 65      | ECA4/ADSC#     | 117     | LA13     | 169     | AD9            |

| 14      | LOCK#             | 66      | OCA4/ECA3/ADV# | 118     | LA12     | 170     | AD8            |

| 15      | GND               | 67      | CACS7#/CAWE7#  | 119     | GND      | 171     | AD7            |

| 16      | HA3               | 68      | CACS6#/CAWE6#  | 120     | LA11     | 172     | AD6            |

| 17      | HA4               | 69      | CACS5#CAWE5#   | 121     | LA10     | 173     | AD5            |

| 18      | HA5               | 70      | CACS4#/CAWE4#  | 122     | LA9      | 174     | AD4            |

| 19      | HA6               | 71      | CACS3#/CAWE3#  | 123     | MRDC#    | 175     | AD3            |

| 20      | HA7               | 72      | CACS2#/CAWE2#  | 124     | MWTC#    | 176     | AD2            |

| 21      | HA8               | 73      | CACS1#/CAWE1#  | 125     | AEN      | 177     | AD1            |

| 22      | HA9               | 74      | CACS0#/CAWE0#  | 126     | MASTER#  | 178     | AD0            |

| 23      | HA10              | 75      | GND            | 127     | NVMCS    | 179     | VCC            |

| 24      | HA11              | 76      | MA11,RAS4#     | 128     | vcc      | 180     | CLK            |

| 25      | HA12              | 77      | MA10           | 129     | SUSPEND  | 181     | GND            |

| 26      | HA13              | 78      | MA9            | 130     | C/BE3#   | 182     | GND            |

| 27      | HA14              | 79      | MA8            | 131     | C/BE2#   | 183     | ECLK           |

| 28      | HA15              | 80      | MA7            | 132     | C/BE1#   | 184     | VCC            |

| 29      | HA16              | 81      | MA6            | 133     | C/BE0#   | 185     | PEN#/3VAT#     |

| 30      | HA17              | 82      | MA5            | 134     | PLOCK#   | 186     | MDLE#/3VDRAM#  |

| 31      | HA18              | 83      | GND            | 135     | FRAME#   | 187     | HREQ/TMOD#     |

| 32      | HA19              | 84      | MA4            | 136     | IRDY#    | 188     | LRDY#          |

| 33      | HA20              | 85      | MA3            | 137     | TRDY#    | 189     | MDOE#          |

| 34      | HA21              | 86      | VCC            | 138     | DEVSEL#  | 190     | HDOE#          |

| 35      | HA22              | 87      | MA2            | 139     | STOP#    | 191     | DBCOE1#        |

| 36      | HA23              | 88      | MA1            | 140     | LCLK     | 192     | DBCOE0#        |

| 37      | HA24              | 89      | MA0            | 141     | GND      | 193     | DLE0#          |

| 38      | GND               | 90      | DWE#           | 142     | GND      | 194     | DLE1#          |

| 39      | HA25              | 91      | RAS3#          | 143     | AD31     | 195     | PWRGD          |

| 40      | HA26              | 92      | RAS2#          | 144     | AD30     | 196     | DIRTYWE#,RAS5# |

| 41      | HA27              | 93      | RAS1#          | 145     | AD29     | 197     | DIRTYI         |

| 42      | HA28              | 94      | RAS0#          | 146     | AD28     | 198     | TAG7           |

| 43      | VCC3              | 95      | CAS7#          | 147     | VCC      | 199     | TAG6           |

| 44      | HA29              | 96      | GND            | 148     | AD27     | 200     | GND            |

| 45      | HA30              | 97      | VCC            | 149     | AD26     | 201     | VCC            |

| 46      | HA31              | 98      | CAS6#          | 150     | AD25     | 202     | TAG5           |

| 47      | BE7#              | 99      | CAS5#          | 151     | AD24     | 203     | TAG4           |

| 48      | BE6#              | 100     | CAS4#          | 152     | AD23     | 204     | TAG3           |

| 49      | BE5#              | 101     | CAS3#          | 153     | AD22     | 205     | TAG2           |

| 50      | BE4#              | 102     | CAS2#          | 154     | AD21     | 206     | TAG1           |

| 51      | BE3#              | 103     | CAS1#          | 155     | AD20     | 207     | TAG0           |

| 52      | BE2#              | 104     | CAS0#          | 156     | AD19     | 208     | TAGWE#         |

Page 10

912-3000-023

9004196 0000284 111 📟

Table 3-4 82C557 Alphabetical Pin Cross-Reference List

| 1 able 3-4 82C | Alpi    | iabeticai Pin Cross | -Veielei    |

|----------------|---------|---------------------|-------------|

| Pin Name       | Pin No. | Pin Name            | Pin No.     |

| AD0            | 178     | CACS3#/CAWE3#       | 71          |

| AD1            | 177     | CACS4#/CAWE4#       | 70          |

| AD2            | 176     | CACS5#/CAWE5#       | 69          |

| AD3            | 175     | CACS6#/CAWE6#       | 68          |

| AD4            | 174     | CACS7#/CAWE7#       | 67          |

| AD5            | 173     | CAS0#               | 104         |

| AD6            | 172     | CAS1#               | 103         |

| AD7            | 171     | CAS2#               | 102         |

| AD8            | 170     | CAS3#               | 101         |

| AD9            | 169     | CAS4#               | 100         |

| AD10           | 168     | CAS5#               | 99          |

| AD11           | 167     | CAS6#               | 98          |

| AD12           | 166     | CAS7#               | 95          |

| AD13           | 162     | CLK                 | 180         |

| AD14           | 161     | D/C#                | 3           |

| AD15           | 160     | DBCOE0#             | 192         |

| AD16           | 159     | DBCOE1#             | 191         |

| AD17           | 158     | DEVSEL#             | 138         |

| AD18           | 157     | DIRTYI              | 197         |

| AD19           | 156     | DIRTYWE# RAS5#      | 196         |

| AD20           | 155     | DLEO#               | 193         |

| AD21           | 154     | DLE1#               | 194         |

| AD22           | 153     | DWE#                | 90          |

| AD23           | 152     | EADS#/(WB/WT#)      | 9           |

| AD24           | 151     | ECA4/ADSC#          | 65          |

| AD25           | 150     | ECAWE#/CACSOO#      | 62          |

| AD26           | 149     | ECDOE#              | 58          |

| AD27           | 148     | ECLK                | 183         |

| AD28           | 146     | FRAME#              | 135         |

| AD29           | 145     | GND                 | 15          |

| AD30           | 144     | GND                 | 38          |

| AD31           | 143     | GND                 | 60          |

| ADS#           | 5       | GND                 | 75          |

| AEN            | 125     | GND                 | 83          |

| AHOLD          | 13      | GND                 | 96          |

| BE0#           | 54      | GND                 | 119         |

| BE1#           | 53      | GND                 | 141         |

| BE2#           | 52      | GND                 | 142         |

| BE3#           | 51      | GND                 | 163         |

| BE4#           | 50      | GND                 | 164         |

|                | 49      | GND                 | 181         |

| BE5#           | 49      | GND                 | 182         |

| BE6#           | 46      | GND                 | 200         |

| BE7#           |         | HA3                 | <del></del> |

| BRDY#          | 6       |                     | 16          |

| C/BE0#         | 133     | HA4                 | 17          |

| C/BE1#         | 132     | HA5                 | 18          |

| C/BE2#         | 131     | HA6                 | 19          |

| C/BE3#         | 130     | HA7                 | 20          |

| CACHE#         | 57      | HA8                 | 21          |

| CACS0#/CAWE0#  | 74      | HA9                 | 22          |

| CACS1#/CAWE1#  | 73      | HA10                | 23          |

| CACS2#/CAWE2#  | 72      | HA11                | 24          |

| Pin Name   | Pin No.  |

|------------|----------|

| HA12       | 25       |

| HA13       | 26       |

| HA14       | 27       |

| HA15       | 28       |

| HA16       | 29       |

| HA17       | 30       |

| HA18       | 31       |

| HA19       | 32       |

| HA20       | 33       |

| HA21       | 34       |

| HA22       | 35       |

| HA23       | 36       |

| HA24       | 37       |

| HA25       | 39       |

| HA26       | 40       |

| HA27       | 41       |

| HA28       | 42       |

| HA29       | 44       |

| HA30       |          |

| HA31       | 45       |

|            | 46       |

| HACALE     | 64       |

| HDOE#      | 190      |

| HITM#      | 55       |

| HLDA       | 12       |

| HOLD       | 11       |

| HREQ/TMOD# | 187      |

| IRDY#      | 136      |

| KEN#/LMEM# | 8        |

| LA9        | 122      |

| LA10       | 121      |

| LA11       | 120      |

| LA12       | 118      |

| LA13       | 117      |

| LA14       | 116      |

| LA15       | 115      |

| LA16       | 113      |

| LA17       | 112      |

| LA18       | 111      |

| LA19       | 110      |

| LA20       | 109      |

| LA21       | 108      |

| LA22       | 107      |

| LA23       | 106      |

| LCLK       | 140      |

| LOCK#      | 14       |

| LRDY#      | 188      |

| M/IO#      | 2        |

| MAO        | 89       |

| MA1        | 88       |

| MA2        | 87       |

| MA3        |          |

| MA4        | 85<br>84 |

|            | 1 04     |

| Pin Name             | Pin No. |

|----------------------|---------|

| MA5                  | 82      |

| MA6                  | 81      |

| MA7                  | 80      |

| MA8                  | 79      |

| MA9                  | 78      |

| MA10                 | 77      |

| MA11,RAS4#           | 76      |

| MASTER#              | 126     |

| MDLE#/3VDRAM#        | 186     |

| MDOE#                | 189     |

| MRDC#                | 123     |

| MWTC#                | 124     |

| NA#                  | 7       |

| NVMCS                | 127     |

| OCA4/ECA3/ADV#       | 66      |

| OCAWE#/CACS1O#       | 63      |

|                      | 59      |

| OCDOE#<br>PEN#/3VAT# |         |

|                      | 185     |

| PLOCK#               | 134     |

| PWRGD                | 195     |

| RAS0#                | 94      |

| RAS1#                | 93      |

| RAS2#                | 92      |

| RAS3#                | 91      |

| REFRESH#             | 105     |

| RESET                | 1       |

| SMIACT#              | 56      |

| STOP#                | 139     |

| SUSPEND              | 129     |

| TAG0                 | 207     |

| TAG1                 | 206     |

| TAG2                 | 205     |

| TAG3                 | 204     |

| TAG4                 | 203     |

| TAG5                 | 202     |

| TAG6                 | 199     |

| TAG7                 | 198     |

| TAGWE#               | 208     |

| TRDY#                | 137     |

| VCC                  | 128     |

| VCC                  | 147     |

| VCC                  | 165     |

| VCC                  | 179     |

| VCC                  | 184     |

| VCC                  | 201     |

| VCC                  | 86      |

| VCC                  | 97      |

| VCC                  | 114     |

| VCC3                 | 10      |

| VCC3                 | 43      |

| VCC3                 | 61      |

| (W/R#)/INV/DIRTYO    | 4       |

912-3000-023

Page 11

**9**004196 0000285 058 **1**

Page 12 912-3000-023

■ 9004196 0000286 T94 **■**

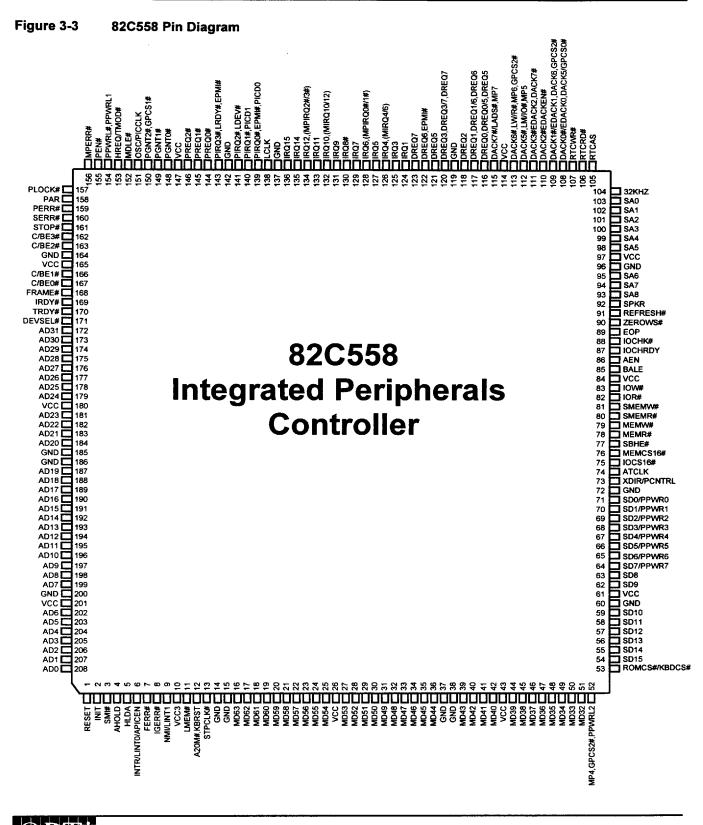

Table 3-5 82C558 Numerical Pin Cross-Reference List

| Dim Mr. | Di- N             | Dir. M. | Din Maria   |

|---------|-------------------|---------|-------------|

| Pin No. | Pin Name          | Pin No. | Pin Name    |

| 1       | RESET             | 54      | SD15        |

| 2       | INIT              | 55      | SD14        |

| 3       | SMI#              | 56      | SD13        |

| 4       | AHOLD             | 57      | SD12        |

| 5       | HLDA              | 58      | SD11        |

| 6       | INTR/LINTO/APICEN | 59      | SD10        |

| 7       | FERR#             | 60      | GND         |

| 8       | IGERR#            | 61      | VCC         |

| 9       | NMI/LINT1         | 62      | SD9         |

| 10      | VCC3              | 63      | SD8         |

| 11      | LMEM#             | 64      | SD7/PPWR7   |

| 12      | A20M#,KBRST       | 65      | SD6/PPWR6   |

| 13      | STPCLK#           | 66      | SD5/PPWR5   |

| 14      | GND               | 67      | SD4/PPWR4   |

| 15      | GND               | 68      | SD3/PPWR3   |

| 16      | MD63              | 69      | SD2/PPWR2   |

| 17      | MD62              | 70      | SD1/PPWR1   |

| 18      | MD61              | 71      | SD0/PPWR0   |

| 19      | MD60              | 72      | GND         |

| 20      | MD59              | 73      | XDIR/PCNTRL |

| 21      | MD58              | 74      | ATCLK       |

| 22      | MD57              | 75      | IOCS16#     |

| 23      | MD56              | 76      | MEMCS16#    |

| 24      | MD55              | 77      | SBHE#       |

| 25      | MD54              | 78      | MEMR#       |

| 26      | VCC               | 79      | MEMW#       |

| 27      | MD53              | 80      | SMEMR#      |

| 28      | MD52              | 81      | SMEMW#      |

| 29      | MD51              | 82      | IOR#        |

| 30      | MD50              | 83      | IOW#        |

| 31      | MD49              | 84      | vcc         |

| 32      | MD48              | 85      | BALE        |

| 33      | MD47              | 86      | AEN         |

| 34      | MD46              | 87      | IOCHRDY     |

| 35      | MD45              | 88      | IOCHK#      |

| 36      | MD44              | 89      | EOP         |

| 37      | GND               | 90      | ZEROWS#     |

| 38      | GND               | 91      | REFRESH#    |

| 39      | MD43              | 92      | SPKR        |

| 40      | MD42              | 93      | SAB         |

| 41      | MD41              | 94      | SA7         |

| 42      | MD40              | 95      | SA6         |

| 43      | vcc               | 96      | GND         |

| 44      | MD39              | 97      | vcc         |

| 45      | MD38              | 98      | SA5         |

| 46      | MD37              | 99      | SA4         |

| 47      | MD36              | 100     | SA3         |

| 48      | MD35              | 101     | SA2         |

| 49      | MD34              | 102     | SA1         |

| 50      | MD33              | 103     | SA0         |

| 51      | MD32              | 103     | 32KHZ       |

| 52      | MP4,GPCS0#,PPWRL2 | 105     | RTCAS       |

| 53      | ROMCS#/KBDCS#     | 106     | RTCRD#      |

|         | NOINICO#/NBDCO#   | 100     | INTONO#     |

| Pin No. | Pin Name                        |

|---------|---------------------------------|

| 107     | RTCWR#                          |

| 108     | DACK0#,EDACK0,<br>DACK5#,GPCS0# |

| 109     | DACK1#,EDACK1,<br>DACK6#,GPCS2# |

| 110     | DACK2#,EDACKEN#                 |

| 111     | DACK3#,EDACK2,<br>DACK7#        |

| 112     | DACK5#,LM/IO#,MP5               |

| 113     | DACK6#,LW/R#,<br>MP6,GPCS3#     |

| 114     | VCC                             |

| 115     | DACK7#,LADS#,MP7                |

| 116     | DREQ0,DREQ0/5,<br>DREQ5         |

| 117     | DREQ1,DREQ1/6,<br>DREQ6         |

| 118     | DREQ2                           |

| 119     | GND                             |

| 120     | DREQ3,DREQ3/7,<br>DREQ7         |

| 121     | DREQ5                           |

| 122     | DREQ6,EPMI#                     |

| 123     | DREQ7                           |

| 124     | IRQ1                            |

| 125     | IRQ3                            |

| 126     | IRQ4,(MIRQ4/6)                  |

| 127     | IRQ5                            |

| 128     | IRQ6,(MPIRQ0#/1#)               |

| 129     | IRQ7                            |

| 130     | IRQ8#                           |

| 131     | IRQ9                            |

| 132     | IRQ10,(MIRQ10/12)               |

| 133     | IRQ11                           |

| 134     | IRQ12,(MPIRQ2#/3#)              |

| 135     | IRQ14                           |

| 136     | IRQ15                           |

| 137     | GND                             |

| 138     | LCLK                            |

| 139     | PIRQ0#,EPMI#,PICD0              |

| 140     | PIRQ1#,PICD1                    |

| 141     | PIRQ2#,LDEV#                    |

| 142     | GND                             |

| 143     | PIRQ3#,LRDY#,EPMI#              |

| 144     | PREQ0#                          |

| 145     | PREQ1#                          |

| 146     | PREQ2#                          |

| 147     | VCC                             |

| 148     | PGNT0#                          |

| 149     | PGNT1#                          |

| 150     | PGNT2#,GPCS1#                   |

| 151     | OSC/PICCLK                      |

| 152     | MDLE#                           |

| 153     | HREQ/TMOD#                      |

| Pin No. | Pin Name      |

|---------|---------------|

| 154     | PPWRL#,PPWRL1 |

| 155     | PEN#          |

| 156     | MPERR#        |

| 157     | PLOCK#        |

| 158     | PAR           |

| 159     | PERR#         |

| 160     | SERR#         |

| 161     | STOP#         |

| 162     | C/BE3#        |

| 163     | C/BE2#        |

| 164     | GND           |

| 165     | VCC           |

| 166     | C/BE1#        |

| 167     | C/BE0#        |

| 168     | FRAME#        |

| 169     | IRDY#         |

| 170     | TRDY#         |

| 171     | DEVSEL#       |

| 172     | AD31          |

| 173     | AD30          |

| 174     | AD29          |

| 175     | AD28          |

| 176     | AD27          |

| 177     | AD26          |

| 178     | AD25          |

| 179     | AD24          |

| 180     | vcc           |

| 181     | AD23          |

| 182     | AD22          |

| 183     | AD21          |

| 184     | AD20          |

| 185     | GND           |

| 186     | GND           |

| 187     | AD19          |

| 188     | AD18          |

| 189     | AD17          |

| 190     | AD16          |

| 191     | AD15          |

| 192     | AD13          |

| 193     | AD13<br>AD12  |

| 194     | AD11          |

| 195     | AD10          |

| 197     | AD9           |

| 198     | AD8           |

| 199     | AD7           |

| 200     | GND           |

| 201     | VCC           |

| 202     | AD6           |

| 203     | AD5           |

| 204     | AD4           |

| 205     | AD3           |

| 206     | AD2           |

| 207     | AD1           |

| 208     | AD0           |

|         | 1             |

Page 13

912-3000-023

**■** 9004196 0000287 920 **■**

Table 3-6 82C558 Alphabetical Pin Cross-Reference List

| Dia No.    | 5: 4:                           |

|------------|---------------------------------|

| Pin No.    | Pin Name                        |

| 208        | AD0                             |

| 207        | AD1                             |

| 206        | AD2                             |

| 205        | AD3                             |

| 204        | AD4                             |

| 203        | AD5                             |

| 202        | AD6                             |

| 199        | AD7                             |

| 198        | AD8                             |

| 197<br>196 | AD9<br>AD10                     |

| 195        | AD10                            |

| 194        | AD12                            |

| 193        | AD12                            |

| 192        | AD14                            |

| 191        | AD15                            |

| 190        | AD16                            |

| 189        | AD17                            |

| 188        | AD18                            |

| 187        | AD19                            |

| 184        | AD20                            |

| 183        | AD21                            |

| 182        | AD22                            |

| 181        | AD23                            |

| 179        | AD24                            |

| 178        | AD25                            |

| 177        | AD26                            |

| 176        | AD27                            |

| 175        | AD28                            |

| 174        | AD29                            |

| 173        | AD30                            |

| 172        | AD31                            |

| 86         | AEN                             |

| 4          | AHOLD                           |

| 74         | ATCLK                           |

| 12         | A20M# KBRST                     |

| 85         | BALE                            |

| 167        | C/BE0#                          |

| 166        | C/BE1#                          |

| 163        | C/BE2#                          |

| 162        | C/BE3#                          |

| 108        | DACK0#,EDACK0,<br>DACK5#,GPCS0# |

| 109        | DACK1#,EDACK1,<br>DACK6#,GPCS2# |

| 110        | DACK2#,EDACKEN#                 |

| 111        | DACK3#,EDACK2,<br>DACK7#        |

| 112        | DACK5#,LM/IO#,MP5               |

| 1          | DACK6#,LW/R#,                   |

| 113        | MP6,GPCS2#                      |

| 115        | DACK7#,LADS#,MP7                |

| 171        | DEVSEL#                         |

| 116        | DREQ0,DREQ0/5,                  |

| 3 | betical    | Pin Cross-Refere         |

|---|------------|--------------------------|

|   | Pin No.    | Pin Name                 |

|   | 117        | DREQ1,DREQ1/6,<br>DREQ6  |

| ĺ | 118        | DREQ2                    |

|   | 120        | DREQ3,DREQ3/7,<br>DREQ7  |

| Į | 121        | DREQ5                    |

|   | 122        | DREQ6,EPMI#              |

| I | 123        | DREQ7                    |

| I | 89         | EOP                      |

|   | 7          | FERR#                    |

|   | 168        | FRAME#                   |

| I | 14         | GND                      |

| I | 15         | GND                      |

| l | 37         | GND                      |

| l | 38         | GND                      |

|   | 60         | GND                      |

| I | 72         | GND                      |

| ĺ | 96         | GND                      |

| l | 119        | GND                      |

| L | 137        | GND                      |

| Ĺ | 142        | GND                      |

| Į | 164        | GND                      |

| l | 185        | GND                      |

| L | 186        | GND                      |

| L | 200        | GND                      |

| l | 5          | HLDA                     |

| Ļ | 153        | HREQ/TMOD#               |

| L | 8          | IGERR#                   |

| Ļ | 2          | INIT                     |

| L | 6          | INTR/LINTO/APICEN        |

| Ļ | 88         | IOCHK#                   |

| Ļ | 87         | IOCHRDY                  |

| Ļ | 75         | IOCS16#                  |

| - | 82         | IOR#                     |

|   | 83         | IOW#                     |

| Ļ | 169        | IRDY#                    |

| Ļ | 124        | IRQ1                     |

| L | 125        | IRQ3                     |

| - | 126        | IRQ4,(MIRQ4/6)           |

| - | 127        | IRQ5                     |

| _ | 128        | IRQ6,(MPIRQ0#/1#)        |

| _ | 129        | IRQ7                     |

|   | 130        | IRQ8#                    |

|   | 131        | IRQ9                     |

| _ | 132        | IRQ10,(MIRQ10/12)        |

| _ | 133        | IRQ11                    |

| - | 134        | IRQ12,(MPIRQ2#/3#) IRQ14 |

| _ | 135<br>136 | IRQ15                    |

| - | 138        | LCLK                     |

| • | 11         | LMEM#                    |

|   | 51         | MD32                     |

| - | 50         | MD33                     |

| _ |            |                          |

| Pin No. | Pin Name           |

|---------|--------------------|

| 48      | MD35               |

| 47      | MD36               |

| 46      | MD37               |

| 45      | MD38               |

| 44      | MD39               |

| 42      | MD40               |

| 41      | MD41               |

| 40      | MD42               |

| 39      | MD43               |

| 36      | MD44               |

| 35      | MD45               |

| 34      | MD46               |

| 33      | MD47               |

| 32      | MD48               |

| 31      | MD49               |

| 30      | MD50               |

| 29      | MD51               |

| 28      | MD52               |

| 27      | MD53               |

| 25      | MD54               |

| 24      | MD55               |

| 23      | MD56               |

| 22      | MD57               |

| 21      | MD58               |

| 20      | MD59               |

| 19      | MD60               |

| 18      | MD61               |

| 17      | MD62               |

| 16      | MD63               |

| 152     | MDLE#              |

| 76      | MEMCS16#           |

| 78      | MEMR#              |

| 79      | MEMW#              |

| 52      | MP4,GPCS0#,PPWRL2  |

| 156     | MPERR#             |

| 9       | NMI/LINT1          |

| 151     | OSC/PICCLK         |

| 158     | PAR                |

| 155     | PEN#               |

| 159     | PERR#              |

| 148     | PGNT0#             |

| 149     | PGNT1#             |

| 150     | PGNT2#,GPCS1#      |

| 139     | PIRQ0#,EPMI#,PICD0 |

| 140     | PIRQ1#,PICD1       |

| 141     | PIRQ2#,LDEV#       |

| 143     | PIRQ3#,LRDY#,EPMI# |

| 157     | PLOCK#             |

| 154     | PPWRL#,PPWRL1      |

| 144     | PREQ0#             |

| 145     | PREQ1#             |

| 146     | PREQ2#             |

| 91      | REEKENHE           |

| Pin No. | Pin Name      |

|---------|---------------|

| 1       | RESET         |

| 53      | ROMCS#/KBDCS# |

| 105     | RTCAS         |

| 106     | RTCRD#        |

| 107     | RTCWR#        |

| 103     | SA0           |

| 102     | SA1           |

| 101     | SA2           |

| 100     | SA3           |

| 99      | SA4           |

| 98      | SA5           |

| 95      | SA6           |

| 94      | SA7           |

| 93      | SA8           |

| 77      | SBHE#         |

| 71      | SD0/PPWR0     |

| 70      | SD1/PPWR1     |

| 69      | SD2/PPWR2     |

| 68      | SD3/PPWR3     |

| 67      | SD4/PPWR4     |

| 66      | SD5/PPWR5     |

| 65      | SD6/PPWR6     |

| 64      | SD7/PPWR7     |

| 63      | SD8           |

| 62      | SD9           |

| 59      | SD10          |

| 58      | SD11          |

| 57      | SD12          |

| 56      | SD13          |

| 55      | SD14          |

| 54      | SD15          |

| 160     | SERR#         |

| 80      | SMEMR#        |

| 81      | SMEMW#        |

| 3       | SMI#          |

| 92      | SPKR          |

| 161     | STOP#         |

| 13      | STPCLK#       |

| 170     | TRDY#         |

| 26      | VCC           |

| 43      | VCC           |

| 61      | VCC           |

| 84      | VCC           |

| 97      | VCC           |

| 114     | VCC           |

| 147     | VCC           |

| 165     | VCC           |

| 180     | VCC           |

| 201     | VCC           |

| 10      | VCC3          |

| 73      | XDIR/PCNTRL   |

| 90      | ZEROWS#       |

| 104     | 32KHZ         |

|         |               |

Page 14

912-3000-023

**9**004196 0000288 867 **=**

### 3.1 Signal Description Definitions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term "assert", or "assertion" indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term "negate", or "negation" indicates that a signal is inactive.

The "/" symbol between signal names indicates that the signals are "multiplexed" and they use the same pin to deliver the various functions. These signals are time-multiplexed and take on different functions at different instances of time. The "()" symbol is used to provide a grouping information for the "multiplexed" signals. The "," symbol between signal names indicates that signals are "pin-wise" programmable depending on the configuration registers. The functions that these signals take on has to be decided on boot-up and can only be changed by reprogramming the registers.

Abbreviations: I = TTL level input, O = CMOS level output, and IS = Schmitt-trigger level input.

#### 3.2 82C556 Signal Descriptions

#### 3.2.1 Host Bus Interface Signals

| Signal Name | Pin<br>No.                       | Signal<br>Type                                                                                                                                                                                                       | Signal Description                                                                                              |

|-------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| HD[63:0]    | 71, 69:60,<br>58:51,             | 1/0                                                                                                                                                                                                                  | Host Data Bus: These pins are bidirectional and connected directly to the CPU data bus and L2 cache data lines. |

|             | 49:31,<br>29:25, 22,<br>21, 19:1 | There are internal pull-downs on these lines which can be engaged during the Suspend mode or if the HD/MD lines are idle, depending on the strap information sampled on the MP1 and MP2 lines during power-on reset. |                                                                                                                 |

#### 3.2.2 SYSC Interface Signals

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DBCOE[1:0]# | 157, 158   | 1              | DBC Output Enables: They are connected to the 82C557's DBCOE[1:0]# pins. These signals, along with the MDOE# and the HDOE# signals, form the encoded command sent from the SYSC to the DBC. These commands indicate the type of cycle currently underway and it enables the DBC to perform the appropriate data steering, latching and direction control. The encoded commands are defined in Table 3-9. |  |

| MDOE#       | 156        | I              | Memory Data Output Enable: This signal is used along with the DBCOE[1:0]# signals and the HDOE# signal to form the encoded commands that are sent out by the SYSC. When asserted, this signal enables data to be outputted on the MD bus. MDOE# is asserted for CPU writes to cache/DRAM, CPU writes to PCI, PCI reads from cache/DRAM, L2 cache write-back cycles, and PCI writes to DRAM.              |  |

| HDOE#       | 155        | I              | Host Data Output Enable: This signal is used along with the DBCOE[1:0]# signals and the MDOE# signal to form the encoded commands that are sen out by the SYSC. When asserted, this signal enables data to be outputted to the HD bus. HDOE# is asserted for CPU reads from DRAM/PCI/VL bus, PC writes to cache, CPU linefills, Suspend mode indication, and reset state indition.                       |  |

| DLE[1:0]#   | 159, 160   | 1              | Data Latch Enables: These lines are connected to the SYSC's DLE[1:0]# pins and used to latch the HD and MD data bus depending on which cycle is occurring.                                                                                                                                                                                                                                               |  |

912-3000-023

9004196 0000289 ?T3 **=**

## 82C556 Signal Descriptions (Cont.)

## 3.2.3 DRAM Interface Signals

| Signal Name                                               | Pin<br>No.                               | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------|------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD[63:32]                                                 | 143, 142,<br>140:131,<br>129,<br>127:109 | 1/0            | Higher Order Memory Data Bus: These pins are connected directly to the higher order DRAM data bus and the IPC. This bus serves as a conduit for all high order reads/writes to and from system memory, CPU writes/reads to/from PCI/VL bus/ISA. These lines have internal pull-up resistors.                                                                                 |

| MD[31:0]#                                                 | 108:104,<br>101,<br>99:92,<br>89:72      | 1/0            | Lower Order Memory Data Bus: These pins are connected directly to the lower order DRAM data bus. During lower order CPU/PCI writes to DRAM, this bus carries the inverted version of the MD[31:0] bus or the MD[63:32] bus. These lines have internal pull-up resistors.                                                                                                     |

| MP[7:6],<br>MP5,<br>MP4/TMOD#,<br>MP3/3VDRAM#,<br>MP[2:0] | 144:149,<br>151, 152                     | I/O            | Memory Parity: These pins are connected directly to the system DRAM data bus. As outputs, these lines are only driven when DWE# is active. MP[7:4] can be configured as outputs for PCI master writes with the aid of the strap option on MP0. During power-up reset, MP[4:0] are used to provide strap functions. Table 3-7 details the strap functionality for these pins. |

|                                                           |                                          | <del>!</del>   | MP[7:4] have internal pull-up resistors and MP[3:0] have internal pull-down resistors.                                                                                                                                                                                                                                                                                       |

| MPERR#                                                    | 154                                      | 0              | Memory Parity Error Indication: This pin is connected to the MPERR# input of the IPC. It indicates the detection of a parity error during a read from the system DRAM and is qualified within the IPC only when the PEN# output from the SYSC is active.                                                                                                                     |

### 3.2.4 Power and Ground Pins

| Signal Name | Pin<br>No.                                      | Signal<br>Type | Signal Description    |

|-------------|-------------------------------------------------|----------------|-----------------------|

| GND         | 23, 24, 50,<br>70, 90,<br>102, 103,<br>130, 150 | I              | Ground Connection     |

| VCC3        | 20, 30, 59                                      | ı              | 3.3V Power Connection |

| VCC         | 91, 100,<br>128, 141,<br>153                    | ı              | 5.0V Power Connection |

Page 16

912-3000-023

**3004196 0000290 415**

Table 3-7 DBC Strap Pin Mapping Functions

| Signals     | High                                                              | Low                                                                |

|-------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| MPO         | Enable MP[7:4] as outputs from the DBC during PCI master writes.  | Disable MP[7:4] as outputs from the DBC during PCI master writes.  |

| MP1         | Enable internal pull-downs or pull-ups when HD/MD are not driven. | Disable internal pull-downs or pull-ups when HD/MD are not driven. |

| MP2         | Disable internal pull-downs and pull-ups in Suspend mode.         | Enable internal pull-downs and pull-ups in Suspend mode.           |

| MP3/3VDRAM# | 5.0V DRAM operation: Should always be high.                       | 3.3V DRAM operation: Only for notebooks.                           |

| MP4/TMOD#   | Normal Mode                                                       | Test Mode                                                          |

Table 3-8 DBC Operating Voltage Groups

| 5.0V TTL    | CPU/Cache<br>(3.3V) | DRAM<br>(5.0V) |

|-------------|---------------------|----------------|

| DBCOE[1:0]# | HD[63:0]            | MD[63:32]      |

| DLE[1:0]#   |                     | MD[31:0]#      |

| MPERR#      |                     | MP[7:6]        |

| MDOE#       |                     | MP5            |

| HDOE#       |                     | MP4/TMOD#      |

|             |                     | MP3/3VDRAM#    |

|             |                     | MP2            |

|             |                     | MP1            |

|             |                     | MP0            |

| 7           | 64                  | 72             |

Page 17

912-3000-023

**-** 9004196 0000291 351 **-**

Table 3-9 DBC Encoded Commands

| DBCOE[1:0]# | MDOE# | HDOE# | Description                                                                                                                                      |

|-------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 01          | 0     | 1     | This code indicates that one of the following cycles is underway:                                                                                |

|             |       |       | - CPU write low order data to PCI<br>- PCI read low order data from cache                                                                        |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 11          | 0     | 1     | This code indicates that one of the following cycles is underway:                                                                                |

|             |       |       | - L2 cache write-back cycle - CPU write to cache/DRAM - CPU write high order data to PCI - PCI read high order data from cache                   |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 10          | 0     | 1     | This code indicates that the following cycles is underway:                                                                                       |

|             |       |       | - PCI read low order data from DRAM                                                                                                              |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 10          | 1     | 0     | This code indicates that currently the system is in the Suspend state and all the buffer outputs should be tristated.                            |

| 00          | 1     | 0     | This code indicates that one of the following cycles is underway:                                                                                |

|             |       |       | - CPU read 64 bits of data from PCI/VLB - CPU read high order data from PCI/VLB - CPU read low order data from PCI/VLB                           |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 00          | 0     | 0     | This code indicates that the following cycle is underway:                                                                                        |

|             |       |       | - PCI write to cache/DRAM                                                                                                                        |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 11          | 1     | 0     | This code indicates that one of the following cycles is underway:                                                                                |

|             |       |       | - CPU read from DRAM, and the cache line being replaced is not dirty - CPU linefill                                                              |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control  |

| 11          | 1     | 1     | This code indicates that one of the following cycles is underway:                                                                                |

|             |       |       | - PCI read from PCI - PCI write to PCI - CPU read/write cache hit - PCI read VLB - PCI write VLB - Idle                                          |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control. |

| 10          | 1     | 1     | This code indicates that the following cycle is underway.                                                                                        |

| ļ           | İ     |       | - PCI read high order data from DRAM                                                                                                             |

|             |       |       | The DBC then, along with the appropriate control signals from the SYSC, performs the required data bus steering, buffering and latching control  |

| 01          | 1     | 0     | This code indicates that the system is in the reset state.                                                                                       |

Page 18

912-3000-023

■ 9004196 0000292 298 ■

## 3.3 82C557 SYSC Signal Description

### 3.3.1 Reset and Clock Signals

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                                   |  |

|-------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET       | 1          | 0              | System Reset: When asserted, this signal resets the CPU. RESET is asserted in response to a PWRGD only and is guaranteed to be active for 1ms such that CLK and VCC are stable.                      |  |

| PWRGD       | 195        | IS             | Power Good: This input reflects the "wired-OR" status of the external reset switch and the power good status from the power supply.                                                                  |  |

| CLK         | 180        | I              | Clock: This input is used as the master single frequency clock. This signal has be identical to the clock signal sent to the CPU.                                                                    |  |

| ECLK        | 183        | I              | <b>Early Clock:</b> This input clock is required to be 3 to 6ns earlier than CLK. This signal is used by the SYSC to generate some critical signals for the host CPU and the cache controller logic. |  |

| LCLK        | 140        | I              | Local Bus Clock: This clock is used by the PCI and local bus state machine within the SYSC. The same clock or another identical signal is used by the local bus devices.                             |  |

|             |            |                | For a synchronous PCI/VL implementation, the skew between this input and the CLK input should satisfy the following requirements:                                                                    |  |

|             |            |                | LCLK < 1/2 CLK period ahead in phase of CLK<br>LCLK < 0.5ns behind in phase of CLK                                                                                                                   |  |

### 3.3.2 Host Bus Interface Signals

| Signal Name | Pin<br>No.                | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA[31:3]    | 46:44,<br>42:39,<br>37:16 | 1/0            | Host Address Bus: HA[31:3] are the address lines of the CPU bus. HA[31:3] are connected to the CPU A[31:3] lines. Along with the byte enable signals, the HA[31:3] lines define the physical area of memory or I/O being accessed.                                                                                                                                                                                                            |

|             |                           |                | During CPU cycles, the HA[31:3] lines are inputs to the SYSC. They are used for address decoding and second level cache tag lookup sequences.                                                                                                                                                                                                                                                                                                 |

|             |                           |                | During inquire cycles, the HA[31:5] are outputs from the SYSC to the CPU to snoop the first level cache tags. They also are outputs from the SYSC to the L2 cache.                                                                                                                                                                                                                                                                            |

|             |                           |                | HA[31:3] have internal pull-downs, however, external pull-ups are required on HA3 and HA4.                                                                                                                                                                                                                                                                                                                                                    |

| BE[7:0]#    | 47:54                     | I/O            | Byte Enable: The byte enables indicate which byte lanes on the CPU data bus are carrying valid data during the current bus cycle. They are inputs to the SYSC for CPU cycles and outputs for master or DMA cycles. In the case of cacheable reads, all eight bytes of data are driven to the CPU, regardless of the state of the byte enables. The byte enable signals indicate the type of special cycle when M/IO# = D/C# = 0 and W/R# = 1. |

|             |                           |                | BE[7:0]# have internal pull-downs that are activated during Suspend or when HLDA is active.                                                                                                                                                                                                                                                                                                                                                   |

912-3000-023

Page 19

## 82C557 Signal Descriptions (Cont.)

| Signal Name                                           | Pin<br>No.    | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M/IO#,<br>D/C#,<br>(W/R#)/INV/<br>DIRTYO <sup>a</sup> | 2,<br>3,<br>4 | I,<br>B(W/R#)  | Bus Cycle Definition (Memory/Input-Output, Data/Control, Write/Read): M/IO#, D/C#, W/R# define CPU bus cycles. Interrupt acknowledge cycles are forwarded to the PCI bus as PCI interrupt acknowledge cycles. All I/O cycles and any memory cycles that are not directed to memory controlled by the SYSC's DRAM interface are forwarded to PCI. The W/R# pin serves also as an output signal and is used as INV for L1 cache and DIRTYO for L2 cache during an inquire cycle. If a combined Tag/Dirty RAM implementation is being used, then the W/R# pin does not serve as a DIRTYO pin. |

| ADS#                                                  | 5             | ı              | Address Strobe: The CPU asserts ADS# to indicate that a new bus cycle is beginning. ADS# is driven active in the same clock as the address, byte enables, and cycle definition signals.                                                                                                                                                                                                                                                                                                                                                                                                    |

| BRDY#                                                 | 6             | 0              | Burst Ready: BRDY# indicates that the system has responded in one of three ways:  1) Valid data has been placed on the CPU data bus in response to a read, 2) CPU write data has been accepted by the system, or 3) the system has responded to a special cycle.                                                                                                                                                                                                                                                                                                                           |

| NA#                                                   | 7             | 0              | Next Address: This signal is connected to the CPU's NA# pin to request pipe-lined addressing for local memory cycle. The SYSC asserts NA# for one clock when the system is ready to accept a new address from the CPU, even if all data transfers for the current cycle have not completed.  The 3.3V Pentium processor and the M1 processor support pipelined memory                                                                                                                                                                                                                      |

| KEN#/LMEM#                                            | 8             | 0              | accesses, however, the K5 processor does not support this feature.  Cache Enable or Local Memory Accessed: This pin is connected to the KEN# input of the CPU and is used to determine whether the current cycle is cacheable. During master cycles, the SYSC asserts this signal to inform the IPC that local system memory needs to be accessed. The IPC is then responsible for providing the data path to the corresponding master.                                                                                                                                                    |

| EADS#/<br>(WB/WT#)                                    | 9             | 0              | External Address Strobe or Write-Back/Write-Through: This output has two functions. It indicates that a valid address has been driven onto the CPU's address bus by an external device. This address will be used to perform an internal cache inquiry cycle when the CPU samples EADS# active. It is also used to control write-back or write-through policy for the primary cache during CPU cycles.                                                                                                                                                                                     |

| HITM#                                                 | 55            | ı              | Hit Modified: Indicates that the CPU has had a hit on a modified line in its internal cache during an inquire cycle. It is used to prepare for write-back.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CACHE#                                                | 57            | 1              | Cacheability: It is connected to the CPU's CACHE# pin. It goes active during a CPU initiated cycle to indicate when, an internal cacheable read cycle or a burst write-back cycle, occurs.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SMIACT#                                               | 56            | I              | System Management Interrupt Active: The CPU asserts SMIACT# in response to the SMI# signal to indicate that it is operating in System Management Mode (SMM).                                                                                                                                                                                                                                                                                                                                                                                                                               |

Page 20

912-3000-023

**■ 9004196 0000294 060** ■

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                            |

|-------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD        | 11         | 0              | CPU Hold Request: This output is connected to the HOLD input of the CPU. This signal requests that the CPU allow another bus master complete control of its buses. In response to HOLD going active, the CPU will float most of its output and I/O pins and then assert HLDA. |

| HLDA        | 12         | ł              | CPU Hold Acknowledge: This input is connected to the CPU's HLDA line. This signal indicates, in response to a HOLD, when the CPU has relinquished bus control to another bus master.                                                                                          |

| AHOLD       | 13         | 0              | Address Hold: This signal is used to tristate the CPU address bus for internal cache snooping.                                                                                                                                                                                |

| LOCK#       | 14         | 1              | CPU Bus Lock: The processor asserts LOCK# to indicate the current bus cycle is locked. It is used to generate PLOCK# for the PCI bus.                                                                                                                                         |

|             | 1          |                | LOCK# has an internal pull-down resistor that is engaged when HLDA is active.                                                                                                                                                                                                 |

a. In this case the ", " does not mean that they are group-wise programmable, they are separate pins

#### 3.3.3 Cache Control Interface Signals

| Signal Name               | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECDOE#                    | 58         | 0              | Even Bank Cache Output Enable: It is connected to the output enables of the SRAMs in the even bank of the L2 cache to enable data read.                                                                                                                                                                                                                                                   |

| OCDOE#                    | 59         | 0              | Odd Bank Cache Output Enable: It is connected to output enables of the SRAMs in the odd bank of the L2 cache to enable data read.                                                                                                                                                                                                                                                         |

| ECAWE#/<br>CACS0O#        | 62         | 0              | Even Bank Cache Write Enable or Bank 0 Synchronous SRAM Chip Select: For asynchronous L2 cache operations this pin becomes ECAWE#, and is connected to the write enables of the SRAMs in the even bank of the L2 cache to enable data update. For synchronous L2 cache operation, this pin provides the chip select for the second bank (synchronous L2 cache is always non-interleaved). |

| OCAWE#/<br>CACS1O#        | 63         | 0              | Odd Bank Cache Write Enable or Bank 1 Synchronous SRAM Chip Select: For asynchronous L2 cache operations this pin becomes OCAWE#, and is connected to the write enables of the SRAMs in the odd bank of the L2 cache to enable data update. For synchronous L2 cache operation, this pin provides the chip select for the first bank (synchronous L2 cache is always non-interleaved).    |

| CACS[7:0]#/<br>CAWE[7:0]# | 67:74      | 0              | Cache Chip Selects 7-0 or Cache Write Enables 7-0: For asynchronous L2 cache operations these pins become chip selects and are connected to the chip selects of the SRAMs in the L2 cache in both banks to enable data read/write operations. For synchronous L2 cache operation these pins become cache write enables for the SRAMs.                                                     |

912-3000-023

Page 2

| 9004196 0000295 TT? 🖿

# 82C557 Signal Descriptions (Cont.)

| Signal Name        | Pin<br>No.          | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                      |

|--------------------|---------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|