# **VRAM**

# 64K x 4 DRAM **WITH 256 x 4 SAM**

#### **FEATURES**

- Industry standard pinout, timing and functions

- High performance CMOS silicon gate process

- Single +5V ±10% power supply

- Inputs and outputs are fully TTL and CMOS compatible

- Refresh modes: RAS ONLY, CAS-BEFORE-RAS, and HIDDEN

- 256-cycle refresh within 4ms

- Optional PAGE MODE access cycles

- Dual port organization: 64K x 4 DRAM port 256 x 4 SAM port

- Bit MASKED WRITE mode capability on DRAM port

- No refresh required for Serial Access Memory

- Low power: 15mW standby; 250mW active, typical

- Fast access times 100ns parallel, 33ns serial

| OPTIONS               | MARKING |

|-----------------------|---------|

| Timing (DRAM, SAM)    |         |

| 100ns, 33ns           | -10     |

| 120ns, 40ns           | -12     |

| 150ns, 60ns           | -15     |

| • Packages            |         |

| Plastic DIP (400 mil) | None    |

| Ceramic DIP (400 mil) | С       |

| Plastic ZIP           | Z       |

#### PIN ASSIGNMENT (Top View)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (A-8,                                                                               |                                                                                                                  | 4                                                                             | 24-Pin Zi<br>(C-4)                                 | Ρ                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------|

| and the second s | SC 1 1 • SDQ1 12 SDQ2 13 TR/OE 14 DQ1 15 DQ2 16 ME/WE 17 RAS 18 A6 19 A5 110 Vcc 12 | 24 Vss<br>23 SDQ4<br>22 SDQ3<br>21 SE<br>20 DQ4<br>19 DQ3<br>18 CAS<br>17 A0<br>16 A1<br>15 A2<br>14 A3<br>13 A7 | DQ3<br>SE<br>SDQ4<br>SC<br>SDQ2<br>DQ1<br>ME/WE<br>A6<br>A4<br>A7<br>A2<br>A0 | 1 5 5 5 6 8 11 15 5 5 6 16 18 19 19 19 12 22 23 24 | DQ4<br>SDQ3<br>Vss<br>SDQ1<br>TR/OE<br>DQ2<br>RAS<br>A5<br>Vcc<br>A3<br>A1<br>CAS |

#### **GENERAL DESCRIPTION**

The MT42C4064 is a high speed, dual port CMOS dynamic random access memory, or video RAM (VRAM) containing 262,144 bits. They may be accessed by a four bit wide DRAM port or by a 256 x 4 bit serial access memory (SAM) port. Data may be transferred bidirectionally between the DRAM and the SAM.

The DRAM portion of the VRAM is functionally identical to the MT4067 (64K x 4) bit DRAM. Four 256-bit data registers make up the serial access memory portion of the VRAM. Data I/O and internal data transfer are accomplished using three separate bidirectional data paths: the 4-bit random access I/O port, the four internal 256 bit wide paths between the DRAM and the SAM, and the 4-bit serial I/O port for the SAM. The rest of the circuitry consists of the control, timing, and address-decoding logic.

Each of the ports may be operated asynchronously and independently of the other except when data is being transferred internally between them. As with all DRAMs, the VRAM must be refreshed to maintain data. The refresh cycles must be timed so that all 256 combinations of RAS addresses are executed at least every 4ms (regardless of sequence). Micron recommends evenly spaced refresh cycles for maximum data integrity. An internal transfer between the DRAM and the SAM counts as a refresh cycle. The SAM portion of the VRAM is fully static and does not require any

MT42C4064 REV.1/91

Micron Technology, Inc., reserves the right to change products or specifications without notice.

3-1

# MU42C4064

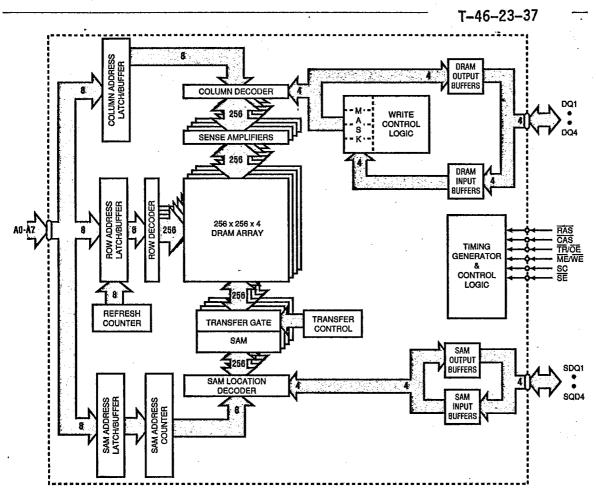

Figure 1

MT42C4064 BLOCK DIAGRAM

#### **PIN DESCRIPTIONS**

T-46-23-37

| DIP PIN<br>NUMBER(S)             | ZIP PIN<br>NUMBER(S)             | SYMBOL      | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                             |

|----------------------------------|----------------------------------|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                | 7                                | SC          | Input            | Serial Clock: Clock input to the serial address counter for the SAM registers.                                                                                                                                                                                                                          |

| 4                                | 8, 9, 4, 5                       | TR/OE       | Input            | Transfer Enable: Enables an internal TRANSFER operation at RAS (H → L), or Output Enable: Enables the DRAM output buffers when taken                                                                                                                                                                    |

|                                  |                                  |             | _                | LOW after RAS goes LOW (CAS must also be LOW); otherwise, the output buffers are in a High-Z.                                                                                                                                                                                                           |

| 7                                | 13                               | ME/WE       | Input            | Mask Enable: If ME/WE is LOW at the falling edge of RAS a MASKED WRITE cycle is performed, or                                                                                                                                                                                                           |

|                                  |                                  |             |                  | Write Enable: WE is used to select a READ (WE = H) or WRITE (WE = L) cycle when accessing the DRAM. This includes a DRAM-TO-SAM TRANSFER (WE = H) or SAM-TO-DRAM TRANSFER (WE = L).                                                                                                                     |

| 8                                | 14                               | RAS         | Input            | Row Address Strobe: RAS is used to clock in the 8 row-address bits and as a strobe for the MASK ENABLE and TRANSFER functions.                                                                                                                                                                          |

| 9, 10, 11, 13,<br>14, 15, 16, 17 | 23, 22, 21, 20<br>17, 16, 15, 19 | A0 to A7    | Input            | Address Inputs: For the DRAM operation, these inputs are multiplexed and clocked by RAS and CAS to select 4 bits out of the 64K available. During TRANSFER operations, A0 to A7 indicate the DRAM row being accessed (when RAS goes LOW) and the SAM start address (when CAS goes LOW).                 |

| 18                               | 24                               | CAS         | Input            | Column Address Strobe: CAS is used to clock in the 8 column-address bits and enable the DRAM output buffers (TR/OE must also be LOW).                                                                                                                                                                   |

| 21                               | 3                                | SE          | Input            | Serial Port Enable: SE enables the serial I/O buffers and allows a serial READ or WRITE operation to occur, otherwise the output buffers are in a High-Z state.SE is also used during a TRANSFER operation to indicate whether a SAM-TO-DRAM TRANSFER or a SERIAL-INPUT-MODE ENABLE cycle is performed. |

| 5, 6, 19, 20                     | 11,12,1,2                        | DQ1 - DQ4   | Input/<br>Output | DRAM Data I/O: Inputs, Outputs, or High-Z, and/or Mask Data Inputs: For MASKED WRITE cycle only.                                                                                                                                                                                                        |

| 2, 3, 22, 23                     | 8,9,4,5                          | SDQ1 - SDQ4 | Input/<br>Output | Serial Data I/O: Input, Output, or High-Z.                                                                                                                                                                                                                                                              |

| 12                               | 18                               | Vcc         | Supply           | Power Supply: +5V ±10%                                                                                                                                                                                                                                                                                  |

| 24                               | 6                                | Vss         | Supply           | Ground                                                                                                                                                                                                                                                                                                  |

#### **FUNCTIONAL DESCRIPTION**

The VRAM can be divided into three functional blocks (see Figure 1); the DRAM, the transfer control circuitry, and the serial access memory (SAM). All of the operations described below are also shown in the ACT iming Diagrams section of this data sheet, and are summarized in the Truth Table.

Note:

For dual function pins, the function that is not being discussed will be surrounded by parentheses. For example, when discussing transfer operations the  $\overline{TR}/\overline{OE}$  pin will be shown as  $\overline{TR}/(\overline{OE})$ .

#### DRAM OPERATION

The DRAM portion of the VRAM is functionally identical to standard 64K x 4 DRAMs. However, because several of the DRAM control pins are used for additional functions on this part, several conditions that were undefined or "don't care" states for the DRAM are specified for the VRAM. These conditions are highlighted in the following discussion.

#### READ/WRITE Cycles

The 16 address bits that are used to select a 4-bit word from the 65,536 available are latched into the chip using the A0-A7, RAS, and CAS inputs. First, the 8 row-address bits are set up on the address inputs and clocked into the part when RAS transitions from HIGH to LOW. Next, the 8 column-address bits are set up on the address inputs and clocked-in when CAS goes from HIGH to LOW.

For single port DRAMs the OE pin is a "don't care" when RAS goes LOW. For the VRAM, (TR)/OE is used, when RAS goes LOW, to select between an internal transfer operation and a DRAM operation. (TR)/OE must be HIGH at the RASHIGH to LOW transition for a DRAM port READ or WRITE operation.

If (ME)/WE is HIGH when CAS goes LOW, a DRAM READ operation is performed and the data from the memory cells selected will appear at the DQ1 - DQ4 port. The (TR)/ OE input must be LOW to enable the DRAM output port.

For single port DRAMs, WE is a "don't care" when RAS goes LOW. For the VRAM, (ME)/WE is used, when RAS goes LOW, to select between a MASKED WRITE cycle and anormal WRITE cycle. If (ME)/WE is LOW at the RASHIGH to LOW transition, a MASKED WRITE operation is selected. For a normal DRAM WRITE operation, (ME)/WE must be HIGH at the RAS HIGH to LOW transition. (ME)/ WE is a "don't care" at the RAS HIGH to LOW transition for a DRAM READ cycle.

If (ME)/WE is LOW when CAS goes LOW, a DRAM WRITE operation is performed and the data present on the DQ1 - DQ4 port will be written into the selected memory cells. If ME/(WE) is LOW when RAS goes LOW, the input data will be "masked" before being stored in the DRAM.

The VRAM can perform all the normal DRAM cycles including EARLY-WRITE, LATE-WRITE, READ-WRITE, READ-MODIFY-WRITE, PAGE-MODE READ, PAGE-MODEWRITE, and PAGE-MODEREAD-MODIFY-WRITE. Refer to the AC timing parameters and diagrams in this data sheet for more details on these operations.

#### REFRESH

The MT42C4064 supports RAS ONLY, CAS-BEFORE-RAS, and HIDDEN types of refresh cycles. All 256 rowaddress combinations must be accessed within 4ms. For the CAS-BEFORE-RAS refresh mode, the row addresses are generated internally and the user need not supply them as he must in RASONLY refresh. TR/(OE) must be HIGH when RAS goes LOW for the RAS ONLY and CAS-BEFORE-RAS types of refresh cycles. Any READ, WRITE, or TRANS-FER operation also refreshes the DRAM row that is being accessed.

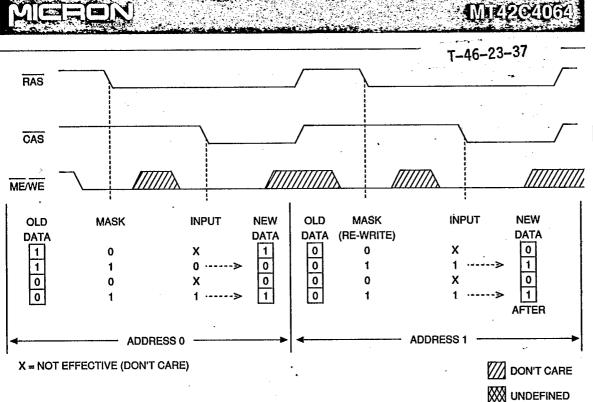

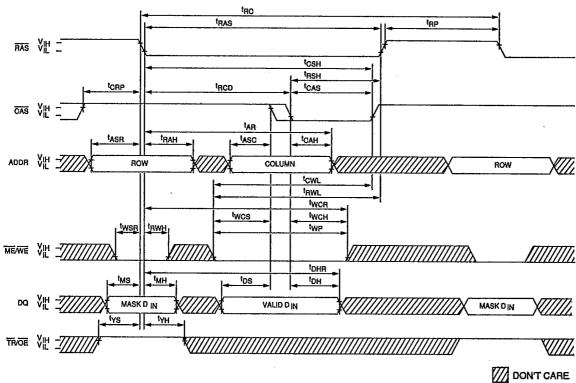

Figure 2 MT42C4064 MASKED WRITE

#### MASKED WRITE

If ME/(WE) is LOW at the RAS HIGH to LOW transition, the data (mask data) present on the DQ1 - DQ4 inputs will be written into the bit mask data register. The mask data acts as an individual write enable for each of the four DQ1 - DQ4 pins. If a LOW (logic 0) is written to a mask data register bit, the input port for that bit is disabled during the subsequent WRITE operation and no new data will be written to that DRAM cell location. A HIGH (logic 1) on a mask data register bit enables the input port and allows normal WRITE operations to proceed. Note that CAS is still HIGH. When

CAS goes LOW, the bits present on the DQ1 - DQ4 inputs will be written to the DRAM (if the mask data bit was HIGH) or ignored (if the mask data bit was LOW). The DRAM contents that correspond to the masked bits will not be changed during the WRITE cycle. Since the mask data register is reset (to all 1's) at the end of every MASKED WRITE cycle, new mask data must be supplied at the beginning of each MASKED WRITE cycle. An example of a typical MASKED WRITE cycle is shown in Figure 2.

#### TRANSFER OPERATION DRAM-TO-SAM TRANSFER (READ TRANSFER)

A TRANSFER operation is initiated when  $\overline{TR}/(\overline{OE})$  is LOW at RAS (HIGH to LOW) time. (ME)/WE indicates the direction of the transfer and must be HIGH as RAS goes LOW for a DRAM-TO-SAM TRANSFER. In this case, the row address bits indicate the four 256-bit DRAM rows that are to be transferred to the four SAM data registers, and the column address bits indicate the start address, or Tap, of the next SERIAL OUTPUT cycle from the SAM data registers. RAS and CAS are used to strobe the address bits into the part. To complete the TRANSFER, TR/(OE) is taken HIGH while  $\overline{RAS}$  and  $\overline{CAS}$  are still LOW. The 1024 bits of DRAM data are then written into the SAM data registers and the serial shift start address is stored in an internal 8-bit register. There must be no rising edges on the serial clock (SC) input while a normal READ TRANSFER is taking place (refer to the AC timing diagrams for READ TRANSFER). A REAL-TIME READ-TRANSFER cycle is the only time when SC must be synchronized with the DRAM RAS and CAS timing (by using  $\overline{TR}/(\overline{OE})$  is to fire the TRANSFER, LOW to HIGH transition). See the REAL-TIME READ-TRANSFER AC timing waveforms. If SE is LOW, the first bits of the new row data will appear at the serial outputs with the first SC clock pulse. SE enables the serial outputs and may be either HIGH or LOW during this operation.

#### SAM-TO-DRAM TRANSFER (WRITE TRANSFER)

The SAM-TO-DRAM TRANSFER operation is identical to the DRAM-TO-SAM TRANSFER described above except that  $(\overline{\text{ME}})/\overline{\text{WE}}$  and  $\overline{\text{SE}}$  must be LOW when  $\overline{\text{RAS}}$  goes LOW. The row address indicates the DRAM row that the SAM data registers will be written to and the column address indicates the Tap address of the next SERIAL INPUT cycle for the SAM data registers. If SE is HIGH when RAS goes LOW, a SERIAL-INPUT-MODE ENABLE cycle is performed.

### SAM OPERATION SERIAL INPUT/OUTPUT MODE CONTROL

The SAM port is automatically placed in the serial output mode after a DRAM-TO-SAM TRANSFER operation. Conversely, after a SAM-TO-DRAM TRANSFER, the SAM port will be in the serial input mode.

#### SERIAL-INPUT-MODE ENABLE (PSEUDO WRITE TRANSFER)

It is possible to change the direction of the SAM port from output to input without performing a SAM-TO-DRAM TRÂNSFER. This operation, called a SERIAL-INPUT-MODE ENABLE cycle, is simply a SAM-TO-DRAM TRANSFER cycle with SE held HIGH instead of LOW. The DRAM data will not be disturbed and the data registers will be ready to accept input data.

The only way to put the SAM port in the serial output mode is to do a DRAM-TO-SAM TRANSFER.

#### SERIAL INPUT and SERIAL OUTPUT

The control inputs for SERIAL INPUT and SERIAL OUTPUT are SC and SE. The rising edge of SC increments the serial address counter and provides access to the next SAM location. SE enables or disables the serial input/output

Serial output of the SAM data register contents will start at the tap start address that was loaded during the DRAM-TO-SAM TRANSFER cycle. The SC input increments the address counter and presents the contents of the next SAM location to the 4-bit port. SE is used as an output enable during the SAM output operation. The serial address is automatically incremented with every SC LOW to HIGH transition, regardless of whether SE is HIGH or LOW, and will wrap around to location 0 after reaching its maximum count of 255.

SC is also used to clock-in data when the device is in the serial input mode. As in the serial output operation, the serial address register contents, which was loaded when the serial input mode were enabled, will determine the serial address to which the first bit will be written. SE acts as an enable for serial data input and must be LOW for normal serial input. If  $\overline{\text{SE}}$  is HIGH, the data inputs are disabled and the SAM contents will not be modified. The serial address register is incremented with every  $L \rightarrow H$  transition of SC, regardless of the logic level on the SE input.

38E D

#### **TRUTH TABLE**

DRAM Operations (SC, SE, and SDQ1 - SDQ4 are "don't care")

|                            | <b>B</b> 18 | 242             | ME  | WE  | TF                  | /OE | Addre | sses | DQ1<br>to                        | Notes |

|----------------------------|-------------|-----------------|-----|-----|---------------------|-----|-------|------|----------------------------------|-------|

| Function                   | RAS         | CAS             | tR* | tC* | tR* tC* tR* tC* DQ4 |     | Notes |      |                                  |       |

| Standby                    | Н           | Н               | X   | Х   | Х                   | Х   | Х     | Х    | High-Z                           |       |

| READ                       | L           | L               | Х   | Н   | н                   | H→L | ROW   | COL  | Data Out                         |       |

| WRITE<br>(EARLY-WRITE)     | L           | L               | Н   | L   | Н                   | Х   | ROW   | COL  | Data In                          | 1     |

| MASKED WRITE               | H⊶L         | L               | L   | L   | Н                   | Х   | ROW   | COL  | Mask Data In,<br>Valid Data In   |       |

| READ-WRITE                 | L           | L               | Н   | H→L | Н                   | L→H | ROW   | COL  | Valid Data Out                   | 1     |

| PAGE-MODE<br>READ          | L           | H→L→H,<br>H→L→H | Н   | Н   | Н                   | H→L | ROW   | COL  | Valid Data Out                   |       |

| PAGE-MODE<br>WRITE         | L           | H→L→H,<br>H→L→H | Н   | L   | Н                   | Х   | ROW   | COL  | Valid Data In                    |       |

| PAGE-MODE<br>READ-WRITE    | L           | H→L→H,<br>H→L→H | Н   | H→L | Н                   | L→H | ROW   | COL  | Valid Data Out,<br>Valid Data In | 1     |

| RAS-ONLY<br>REFRESH        | L           | н               | X   | n/a | Н                   | n/a | ROW   | n/a  | High-Z                           |       |

| HIDDEN<br>REFRESH          | L→H→L       | L               | X   | Н   | х                   | L   | ROW   | COL  | Valid Data Out                   |       |

| CAS-BEFORE-<br>RAS REFRESH | H→L         | L               | X   | Х   | X                   | Х   | Х     | Х    | High-Z                           |       |

#### TRANSFER Operations (DQ1 — DQ4 are "don't care")

| Ermatia m                    | Function | 510 |     | ME  | WE  | TR  | OE  | Addr  | esses | SC | SE   | SDQ1 | Notes |

|------------------------------|----------|-----|-----|-----|-----|-----|-----|-------|-------|----|------|------|-------|

| runction                     | RAS      | CAS | tR* | tC* | tR* | tC* | tR* | tC*   |       |    | sDQ4 |      |       |

| DRAM-TO-SAM<br>TRANSFER      | L        | L   | Н   | Х   | L   | L   | ROW | TAP** | Х     | Х  | Х    | 2    |       |

| SAM-TO-DRAM<br>TRANSFER      | L,       | L,  | L   | Х   | L   | Х   | ROW | TAP** | X     | L  | X    | 3    |       |

| SERIAL-INPUT-<br>MODE ENABLE | L        | L   | L   | Х   | L   | Х   | ROW | TAP** | Х     | Н  | X    | 4    |       |

- \* tR = when RAS goes from HIGH to LOW

tC = when CAS goes from HIGH to LOW

\*\* TAP = Tap Address, the serial address to which the next serial input or output cycle will start.

- Notes: 1. Any type of WRITE cycle may also be a MASKED WRITE cycle.

- 2. The SAM will be in a SERIAL OUTPUT mode after a DRAM-TO- SAM TRANSFER.

- The SAM will be in a SERIAL INPUT mode after a SAM-TO-DRAM TRANSFER.

- The SAM will be put in the SERIAL INPUT mode but the SAM-TO-DRAM TRANSFER will not occur.

3-7

#### **TRUTH TABLE**

Serial I/O Operations (RAS, CAS, ME/WE, TR/OE, and DQ1 - DQ4 are "don't care")

| Function      | SC  | SE SDQ1 — SDQ4  |                | Notes |

|---------------|-----|-----------------|----------------|-------|

| SERIAL OUTPUT | L→H | L               | Valid Data Out | 5     |

| SERIAL INPUT  | L→H | L Valid Data In |                | 6     |

Notes: 5. The SAM must be in the SERIAL OUTPUT mode.

6. The SAM must be in the SERIAL INPUT mode.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc supply relative to Vss | 1.0V to +7.0V  |

|---------------------------------------|----------------|

| Operating Temperature, Ta(Ambient)    |                |

| Storage Temperature (Plastic)         | 55°C to +150°C |

| Power Dissipation                     |                |

| Short Circuit Output Current          |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS** (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C)

| PARAMETER/CONDITION                      | SYMBOL | MIN  | MAX   | UNITS | NOTES |

|------------------------------------------|--------|------|-------|-------|-------|

| Supply Voltage                           | Vcc    | 4.5  | 5.5   | ٧     | 1     |

| Input High (Logic 1) Voltage, All Inputs | ViH    | 2.4  | Vcc+1 | ٧     | 1     |

| Input Low (Logic 0) Voltage, All Inputs  | ViL    | -1.0 | 0.8   | ٧     | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_{A} \le 70^{\circ}C; Vcc = 5.0V \pm 10\%)$

| PARAMETER/CONDITION -                                                               | SYMBOL | MIN | MAX | UNITS | NOTES |

|-------------------------------------------------------------------------------------|--------|-----|-----|-------|-------|

| INPUT LEAKAGE CURRENT (any input (0V≤Vιν≤Vcc), all other pins not under test = 0V). | lı.    | -10 | 10  | μА    |       |

| OUTPUT LEAKAGE CURRENT<br>(DQ, SDQ disabled, 0V≤Vouт≤Vcc).                          | loz    | -10 | 10  | μА    |       |

| OUTPUT LEVELS Output High Voltage (lout = -5mA)                                     | Vон    | 2.4 |     | ٧     |       |

| Output Low Voltage (Ιουτ = 5mA)                                                     | Vol    |     | 0.4 | V     | 1     |

#### **CAPACITANCE**

| PARAMETER                                   | SYMBOL | MIN | MAX | UNITS | NOTES |

|---------------------------------------------|--------|-----|-----|-------|-------|

| Input Capacitance: Ao-A7                    | Ci1    |     | - 5 | рF    | 18    |

| Input Capacitance: RAS, CAS, WE, OE, SC, SE | Ci2    |     | 7   | pF    | 18    |

| Output Capacitance: DQ, SDQ                 | Co     |     | 7   | рF    | 18    |

CURRENT DRAIN, SAM IN STANDBY (Notes 2, 3) (0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, Vcc = 5.0V  $\pm$  10%)

| PARAMETER/CONDITION OF DRAM                                                                                                                                  | SYMBOL | MIN | MAX | UNITS | NOTES |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-------|-------|

| OPERATING CURRENT (RAS and CAS = Cycling; tRC = tRC (MIN)).                                                                                                  | lcc1   |     | 40  | mA    |       |

| OPERATING CURRENT: PAGE MODE (RAS = VIL, CAS = Cycling; <sup>1</sup> PC = <sup>1</sup> PC (MIN)).                                                            | lcc2   |     | 40  | mA    |       |

| STANDBY CURRENT: TTL INPUT LEVELS Power supply standby current (RAS = CAS = VIH after 8 RAS cycles MIN).                                                     | tccs   |     | 10  | mA    |       |

| STANDBY CURRENT; CMOS INPUT LEVELS  Power supply standby current (RAS = CAS = Vcc-0.2V  after 8 RAS cycles MIN. All other inputs at Vcc-0.2V or Vss + 0.2V). | `lcc4  |     | 4   | mA    |       |

| REFRESH CURRENT: RAS-ONLY (RAS = Cycling; CAS = Vih).                                                                                                        | lcc5   |     | 30  | mA    |       |

| REFRESH CURRENT: CAS-BEFORE-RAS (RAS and CAS = Cycling).                                                                                                     | lcc6   |     | 30  | mA    | 22    |

| SAM/DRAM DATA TRANSFER                                                                                                                                       | lcc7   |     | 60  | mA    | ļ     |

CURRENT DRAIN, SAM ACTIVE ( $^tSC = MIN$ ) (Notes 2, 3) (0°C  $\leq T_A \leq 70$ °C; Vcc = 5.0V  $\pm$  10%)

| PARAMETER/CONDITION OF DRAM                                                                                                                                  | SYMBOL | MIN | MAX | UNITS | NOTES |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-------|-------|

| OPERATING CURRENT (RAS and CAS = Cycling; tRC = tRC (MIN)).                                                                                                  | lcc8   |     | 60  | mA    |       |

| OPERATING CURRENT: PAGE MODE (RAS = VIL, CAS = Cycling; <sup>1</sup> PC = <sup>1</sup> PC (MIN)).                                                            | lcc9   |     | 60  | mA    |       |

| STANDBY CURRENT: TTL INPUT LEVELS  Power supply standby current (RAS = CAS = VIH after 8 RAS cycles MIN).                                                    | Icc10  |     | 30  | .mA   |       |

| STANDBY CURRENT: CMOS INPUT LEVELS  Power supply standby current (RAS = CAS = Vcc-0.2V  after 8 RAS cycles MIN. All other inputs at Vcc-0.2V or Vss + 0.2V). | lcc11  |     | 25  | mA    |       |

| REFRESH CURRENT: RAS-ONLY (RAS = Cycling; CAS = ViH).                                                                                                        | lcc12  |     | 50  | mA    |       |

| REFRESH CURRENT: CAS-BEFORE-RAS (RAS and CAS = Cycling).                                                                                                     | lcc13  |     | 50  | mA    | 22    |

| SAM/DRAM DATA TRANSFER                                                                                                                                       | lcc14  |     | 90  | mA    |       |

T-46-23-37

#### **DRAM TIMING PARAMETERS**

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Notes 3, 4, 5, 6, 10, 11, 17) (0°C  $\leq$  T<sub>A</sub>  $\leq$  + 70°C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                         |                   | -10 |         | -12 |         | -15 |         |       |        |

|----------------------------------------------|-------------------|-----|---------|-----|---------|-----|---------|-------|--------|

| PARAMETER                                    | SYM               | MIN | MAX     | MIN | MAX     | MIN | MAX     | UNITS | NOTES  |

| Random READ or WRITE cycle time              | t <sub>RC</sub>   | 190 |         | 220 |         | 260 |         | ns    |        |

| READ-MODIFY-WRITE cycle time                 | <sup>t</sup> RWC  | 250 |         | 295 |         | 345 |         | ns    | 20, 21 |

| PAGE-MODE READ or WRITE                      | t <sub>PC</sub>   | 75  |         | 90  |         | 110 |         | ns    | 6      |

| cycle time                                   |                   |     | L       |     |         |     |         |       |        |

| PAGE-MODE READ-MODIFY-WRITE                  | <sup>t</sup> PRWC | 125 |         | 150 |         | 175 |         | ns    | 20, 21 |

| cycle time                                   |                   |     |         |     |         |     |         |       |        |

| Access time from RAS                         | <sup>t</sup> RAC  |     | 100     |     | 120     |     | 150     | ns    | 7, 8   |

| Access time from CAS                         | <sup>t</sup> CAC  |     | 50      |     | 60      |     | 75      | ns    | 7, 9   |

| RAS pulse width                              | RAS               | 100 | 10,000  | 120 | 10,000  | 150 | 10,000  | ns    |        |

| RAS pulse width (PAGE MODE)                  | <sup>t</sup> RASP | 100 | 100,000 | 120 | 100,000 | 150 | 100,000 | ns    |        |

| RAS hold time                                | <sup>t</sup> RSH  | 50  |         | 60  |         | 75  |         | ns    |        |

| RAS precharge time                           | t <sub>RP</sub>   | 80  |         | 90  |         | 100 |         | ns    |        |

| CAS pulse width                              | tCAS              | 50  | 10,000  | 60  | 10,000  | 75  | 10,000  | ns    |        |

| CAS hold time                                | t <sub>CSH</sub>  | 100 |         | 120 |         | 150 |         | ns    |        |

| CAS precharge time                           | <sup>t</sup> CPN  | 15  |         | 20  |         | 25  |         | ns    |        |

| CAS precharge time (PAGE MODE)               | <sup>t</sup> CP   | 15  |         | 20  |         | 25  |         | ns    | 19     |

| RAS to CAS delay                             | <sup>t</sup> RCD  | 15  | 50      | 15  | 60      | 15  | 75      | ns    | 13     |

| CAS to RAS precharge time                    | tCRP              | 10  |         | 10  |         | 10  |         | ns    |        |

| Row address setup time                       | t <sub>ASR</sub>  | 0   |         | 0   |         | 0   |         | ns    |        |

| Row address hold time                        | <sup>†</sup> RAH  | 15  |         | 15  |         | 15  |         | ns    |        |

| Column address setup time                    | t <sub>ASC</sub>  | 0   |         | 0   |         | 0   |         | ns    |        |

| Column address hold time                     | t <sub>CAH</sub>  | 20  |         | 20  |         | 25  |         | ns    |        |

| Column address hold time (referenced to RAS) | <sup>t</sup> AR   | 45  |         | 70  |         | 80  |         | пѕ    |        |

| READ command setup time                      | <sup>t</sup> RCS  | 0   |         | 0   |         | 0   |         | ns    |        |

| READ command hold time (referenced to CAS)   | <sup>t</sup> RCH  | 0   |         | 0   |         | 0   |         | ns    | 14     |

| READ command hold time (referenced to RAS)   | t <sub>RRH</sub>  | 0   |         | 0   |         | 0   |         | ris   |        |

| WE command setup time                        | twcs              | 0   |         | 0   |         | 0   |         | ns    | 16     |

| WRITE command hold time                      | tWCH              | 20  |         | 25  |         | 30  |         | ns    |        |

| WRITE command hold time (referenced to RAS)  | <sup>t</sup> WCR  | 70  |         | 80  |         | 90  |         | ns    |        |

| WRITE command pulse width                    | t <sub>WP</sub>   | 20  |         | 25  |         | 30  |         | ns    |        |

| WRITE command to RAS lead time               | <sup>t</sup> RWL  | 25  |         | 30  |         | 35  |         | ns    |        |

| WRITE command to CAS lead time               | tCWL              | 25  |         | 30  |         | 35  |         | ns    |        |

| Data-in setup time                           | t <sub>DS</sub>   | 0   |         | 0   |         | 0   |         | ns    | 15     |

| Data-in hold time                            | t <sub>DH</sub>   | 15  |         | 20  |         | 25  |         | ns    | 15     |

| Data-in hold time (referenced to RAS)        | t <sub>DHR</sub>  | 70  |         | 80  |         | 90  |         | ns    |        |

| CAS to WE delay                              | tCWD              | 65  |         | 80  |         | 95  |         | ns    | 16, 20 |

| RAS to WE delay                              | t <sub>RWD</sub>  | 120 |         | 150 |         | 185 |         | ns    | 16, 20 |

| ME/WE to RAS setup time                      | twsr.             | 0   |         | 0   |         | 0   |         | ns    |        |

DRAM TIMING PARAMETERS (Continued) ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Notes 3, 4, 5, 6, 10, 11, 17) (0°C  $\leq$  T<sub>A</sub>  $\leq$  + 70°C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                         | T                |     | 10   |     | 12  | -1  | 5   | T     | T .      |

|----------------------------------------------|------------------|-----|------|-----|-----|-----|-----|-------|----------|

| PARAMETER                                    | SYM              | MIN | MAX  | MIN | MAX | MIN | MAX | UNITS | NOTES    |

| ME/WE to RAS Hold Time                       | <sup>t</sup> RWH | 10  |      | 10  |     | 15  | ns  |       |          |

| Mask Data (DQ_) to RAS setup time            | t <sub>MS</sub>  | 0   |      | 0   |     | 0   |     | ns    |          |

| Mask Data (DQ ) to RAS hold time             | t <sub>MH</sub>  | 20  |      | 20  |     | 25  |     | ns    |          |

| Transition time (rise or fall)               | l t <sub>T</sub> | 3   | - 50 | 3   | 50  | 3   | 50  | ns    |          |

| Refresh period (256 cycles)                  | <sup>t</sup> REF |     | 4    |     | 4   |     | 4   | ms    | <u> </u> |

| RAS to CAS precharge time                    | <sup>t</sup> RPC |     | 0    | L   | 0   |     | 0   | ns    |          |

| CAS setup time<br>(CAS-BEFORE-RAS REFRESH)   | <sup>t</sup> CSR | 10  |      | 10  |     | 10  |     | ns    |          |

| CAS hold time<br>(CAS-BEFORE-RAS REFRESH)    | tCHR             | 20  |      | 25  |     | 30  |     | ns    | 22       |

| CAS to output in Low-Z                       | CLZ              | 5   |      | 5   |     | 5   |     | ns    |          |

| Output buffer turn-off delay                 | t <sub>OFF</sub> | 0   | 25   | 0   | 25  | 0   | 30  | ns    | 7, 12    |

| Access time from (TR)/OE                     | t <sub>OE</sub>  |     | 25   |     | 25  |     | 30  | ns    |          |

| Output Disable                               | t <sub>OD</sub>  | 0   | 25   | 0   | 25  | 0   | 30  | ns    |          |

| Output Disable hold time from start of WRITE | <sup>t</sup> OEH |     | 25   |     | 25  |     | 30  | ns    |          |

| Output Enable to RAS delay                   | tord             |     | 0    |     | 0   |     | 0   | ns    |          |

ĭ.

T-46-23-37

#### TRANSFER AND MODE CONTROL TIMING PARAMETERS

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Notes 3, 4, 5, 6, 17) (0° C  $\leq$  T<sub>A</sub>  $\leq$  + 70°C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                                  | -10              |     |     | -12  |     | -15 |                                       |       |       |

|-------------------------------------------------------|------------------|-----|-----|------|-----|-----|---------------------------------------|-------|-------|

| PARAMETER                                             | SYM              | MIN | MAX | MIN  | MAX | MIN | MAX                                   | UNITS | NOTES |

| TRANSFER command to RAS setup time                    | trs              | 0   |     | 0    |     | 0   |                                       | ns    | 23    |

| TRANSFER command to RAS hold time                     | <sup>t</sup> RTH | 80  |     | 90   |     | 100 |                                       | ns    | 23    |

| TRANSFER command to CAS hold time                     | <sup>t</sup> CTH | 30  |     | 30   |     | 35  |                                       | ns    | 23    |

| TRANSFER command to SC lead time                      | <sup>t</sup> TSL | 5   |     | 5    |     | 10  |                                       | ns    | 23    |

| TRANSFER command to RAS lead time                     | <sup>t</sup> TRL | 10  |     | 10   |     | 10  |                                       | ns    | 23    |

| TRANSFER command to RAS delay time                    | <sup>t</sup> TRD | 15  |     | 15   |     | 20  |                                       | ns    | 23    |

| TRANSFER command to CAS time                          | t <sub>TCL</sub> | 10  |     | 10   |     | 10  |                                       | ns    | 23    |

| TRANSFER command to CAS delay time                    | t <sub>TCD</sub> | 15  |     | 15   |     | 20  |                                       | ns    | 23    |

| First SC edge to TRANSFER command delay time          | <sup>t</sup> TSD | 10  |     | 10   |     | 20  |                                       | пѕ    | 23    |

| CAS to first SC delay                                 | <sup>t</sup> RSD |     | 95  |      | 105 |     | 115                                   | ns    |       |

| RAS to first SC delay                                 | tcsp             |     | 25  |      | 35  |     | 45                                    | ns    |       |

| SAM-TO-DRAM (WRITE) transfer command to RAS hold time | †RTHW            | 15  |     | 15   |     | 15  |                                       | ns    |       |

| Serial output buffer turn-off delay from RAS          | tsdz             | 10  | 40  | ` 10 | 50  | 10  | 60                                    | пѕ    |       |

| SC to RAS setup time                                  | tsrs             | 35  |     | 40   |     | 45  |                                       | ns    |       |

| RAS to SC delay time                                  | <sup>t</sup> SRD | 25  |     | 30   |     | 35  |                                       | ns    |       |

| Serial data input to SE delay time                    | <sup>t</sup> SZE | 0   |     | 0    |     | 0   |                                       | ns    |       |

| RAS to SD buffer turn-on time                         | <sup>t</sup> SRO | 0   |     | 0    |     | 0   |                                       | ns    |       |

| Serial data input delay from RAS                      | t <sub>SDD</sub> | 50  |     | 55   |     | 60  |                                       | ns    |       |

| Serial data input to RAS delay time                   | tszs             | 0   |     | 0    |     | 0   |                                       | ns    |       |

| SERIAL INPUT MODE ENABLE (SE) to RAS setup time       | t <sub>ESR</sub> | 0   |     | 0    |     | 0   |                                       | ns    |       |

| SERIAL INPUT MODE ENABLE<br>(SE) to RAS hold time     | <sup>t</sup> REH | 15  |     | 15   |     | 15  |                                       | ns    |       |

| NONTRANSFER command to RAS setup time                 | t <sub>YS</sub>  | 0   |     | 0    |     | 0   | , , , , , , , , , , , , , , , , , , , | ns    | 24    |

| NONTRANSFER command to RAS hold time                  | <sup>t</sup> YH  | 15  |     | 15   |     | 20  |                                       | ns    | 24    |

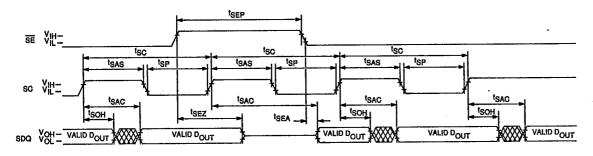

#### **SAM TIMING PARAMETERS**

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Notes 3, 4, 5, 17, 25) (0° C  $\leq$  T<sub>A</sub>  $\leq$  + 70°C, Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                        |                   | -10 |       | -12 |       | -15 |       |                 |       |

|---------------------------------------------|-------------------|-----|-------|-----|-------|-----|-------|-----------------|-------|

| PARAMETER                                   | SYM               | MIN | MAX   | MIN | MAX   | MIN | MAX   | UNITS           | NOTES |

| Serial clock cycle time                     | t <sub>sc</sub>   | 33  | 50000 | 40  | 50000 | 60  | 50000 | ns              |       |

| Access time from SC                         | t <sub>SAC</sub>  |     | 33    |     | 40    |     | 60    | ns              | 25    |

| SC precharge time                           | t <sub>SP</sub>   | 10  |       | 10  |       | 20  |       | ns              |       |

| SC pulse width                              | t <sub>SAS</sub>  | 10  |       | 10  |       | 20  |       | ns              |       |

| Access time from SE                         | †SEA              |     | 25    |     | 30    |     | 40    | ns              | 25    |

| SE precharge time                           | t <sub>SEP</sub>  | 10  |       | 15  | [.    | 20  |       | ns              |       |

| SE pulse width                              | t <sub>SE</sub>   | 15  |       | 15  |       | 20  |       | ns              |       |

| Serial data out hold time after SC high     | tsон              | 10  |       | 10  |       | 10  |       | ns              | 25    |

| Serial output buffer turn off delay from SE | <sup>t</sup> SEZ  | 0   | 15    | 0   | 25    | 0   | 30    | ns              | 25    |

| Serial data in setup time                   | tsds              | 0   |       | 0   |       | 0   |       | ns              |       |

| Serial data in hold time                    | t <sub>SDH</sub>  | 15  |       | 20  |       | 25  |       | :               |       |

| SERIAL INPUT (Write) Enable setup time      | tsws              | 0.  |       | 0   |       | 0   |       | ns              |       |

| SERIAL INPUT (Write) Enable hold time       | tswH              | 20  |       | 35  |       | 45  |       | ns              | ,     |

| SERIAL INPUT (Write) Disable setup time     | <sup>t</sup> swis | 0   |       | 0   |       | 0   |       | ns <sup>-</sup> |       |

| SERIAL INPUT (Write) Disable hold time      | <sup>t</sup> swiH | 20  |       | 35  |       | 45  |       | ns              |       |

#### **NOTES**

**MULTIPORT DRAM**

- 1. All voltages referenced to Vss.

- Icc is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time and the output open.

- An initial pause of 100µs is required after power-up followed by any eight RAS cycles and 1 SC cycle, before proper device operation is assured. The RAS cycle wake-up should be repeated any time the 4ms static refresh require-ment is exceeded.

- 4. AC characteristics assume <sup>t</sup>T = 5ns.

- VIH (MIN) and VIL (MAX) are reference levels for measuring timing of input signals. Transition times are measured between VIH and VIL.

- The minimum specifications are used only to indicate cycle time at which proper operation over the full temperature range (0°C ≤ T<sub>A</sub> ≤ 70°C) is assured.

- Measured with a load equivalent to 2 TTL gates and 100pF.

- Assumes that <sup>t</sup>RCD < <sup>t</sup>RCD (MAX). If <sup>t</sup>RCD is greater than the maximum recommended value shown in this table, <sup>t</sup>RAC will increase by the amount that <sup>t</sup>RCD exceeds the value shown.

- Assumes that <sup>t</sup>RCD ≥ <sup>t</sup>RCD (MAX).

- 10. If CAS = VIH, DRAM data output is high impedance.

- 11. If CAS = VII, DRAM data output may contain data from the last valid READ cycle.

- tOFF (MAX) defines the time at which the output achieves the open circuit condition and is not referenced to VoH or VoL.

- 13. Operation within the <sup>t</sup>RCD (MAX) limit ensures that <sup>t</sup>RAC (MAX) can be met. <sup>t</sup>RCD (MAX) is specified as a reference point only; if <sup>t</sup>RCD is greater than the specified <sup>t</sup>RCD (MAX) limit, then access time is controlled exclusively by <sup>t</sup>CAC.

- tRCH is referenced to the first rising edge of RAS or CAS.

- 15. These parameters are referenced to CAS leading edge

- in EARLY WRITE cycles and to  $\overline{WE}$  leading edge in LATE WRITE or READ-MODIFY-WRITE cycles.

- 16. <sup>t</sup>WCS, <sup>t</sup>CWD and <sup>t</sup>RWD are restrictive operating parameters in READ-WRITE and READ-MODIFY-WRITE cycles only. If <sup>t</sup>WCS ≥ <sup>t</sup>WCS (MIN), the cycle is an EARLY-WRITE cycle and the data output will remain open circuit throughout the entire cycle. If <sup>t</sup>CWD ≥ <sup>t</sup>CWD (MIN) and <sup>t</sup>RWD ≥ <sup>t</sup>RWD (MIN), the cycle is a READ-WRITE and the data output will contain data read from the selected cell. If neither of the above conditions are met, the state of data out (at access time and until CAS goes back toVIH) is indeterminate. If <sup>t</sup>WCS ≤ <sup>t</sup>WCS, the cycle is a LATE WRITE [(ME)/WE falls after CAS] <sup>t</sup>WCS, <sup>t</sup>CWD and <sup>t</sup>RWD do not apply.

- 17. In addition to meeting the transition rate specification, all input signals must transit between VIH and VIL (or between VIL and VIH) in a monotonic manner.

- 18. Capacitance calculated from the equation  $C = I\Delta t$   $\Delta V$ with  $\Delta V = 3V$  and Vcc = 5V. This parameter is

- 19. If CAS is LOW at the falling edge of RAS, DQ will be maintained from the previous cycle. To initiate a new cycle and clear the data out buffer, CAS must be pulsed HIGH for <sup>t</sup>CP. Note 8 applies to determine valid data out.

- 20. Includes the  $\overline{OE}$  delay time (30ns for the -10, 40ns for the -12, and 50ns for the -15).

- During a READ cycle, if OE is LOW then taken HIGH (VIH) DQ goes open. If OE is tied permanently LOW a READ-MODIFY-WRITE operation is not possible.

- 22. Enables on-chip refresh and address counters.

- TRANSFER command means that TR/(OE) is LOW when RAS goes LOW.

- 24. NONTRANSFER command means that TR/(OE) is HIGH when RAS goes LOW.

- Measured with a load equivalent to 2 TTL gates and 50pF.

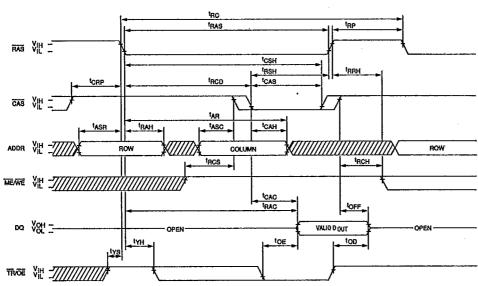

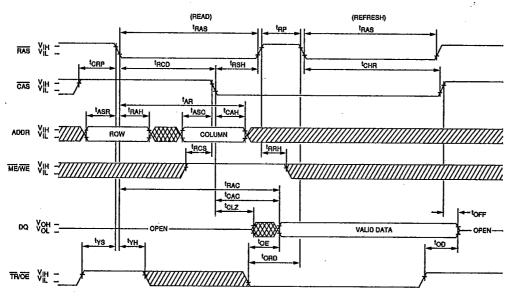

#### **DRAM READ CYCLE**

T-46-23-37

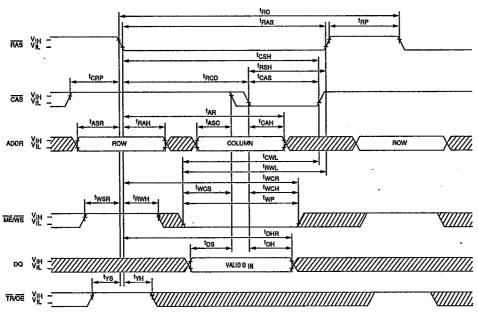

#### **DRAM EARLY-WRITE CYCLE**

DON'T CARE

W UNDEFINED

T-46-23-37

#### **DRAM MASKED WRITE CYCLE**

**W** UNDEFINED

## **DRAM READ-WRITE CYCLE** (READ-MODIFY-WRITE CYCLE and LATE-WRITE CYCLE)

T-46-23-37

**W** UNDEFINED

FAS VIL -<sup>t</sup>CSH <sup>t</sup>ASH <sup>1</sup>CAH trwL †RWD (CWD ME/WE VIL -RAC VALID D VALID D OUT VIOL -- OPEN-\_tOEH TR/OE VIL -////// DON'T CARE

NOTE: If ME/WE is LOW, a MASKED WRITE cycle will be performed.

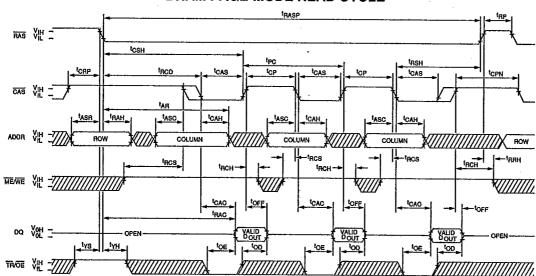

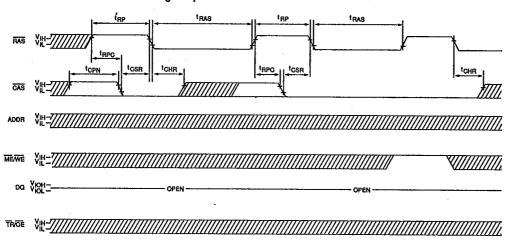

#### **DRAM PAGE-MODE READ CYCLE**

#### DRAM PAGE-MODE EARLY-WRITE CYCLE

DON'T CARE

**W** UNDEFINED

NOTE: If ME/WE is LOW, a MASKED WRITE cycle will be performed.

T-46-23-37

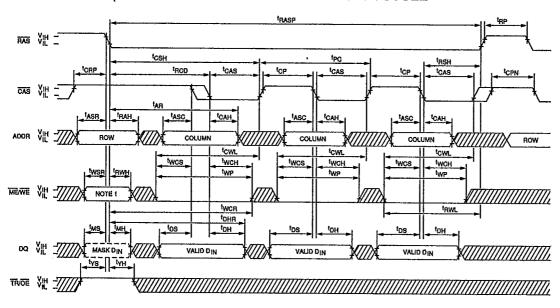

#### DRAM PAGE-MODE READ-WRITE CYCLE (READ-MODIFY-WRITE CYCLE)

NOTE: 1. If ME/WE is LOW, a MASKED WRITE cycle will be performed.

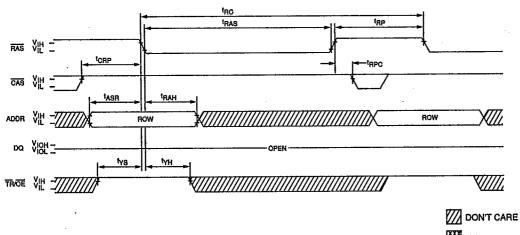

#### RAS-ONLY REFRESH CYCLE (ME/WE = Don't Care)

**W** UNDEFINED

## **CAS-BEFORE-RAS REFRESH CYCLE**

$(A_0 - A_7 \text{ and } \overline{ME}/\overline{WE} \text{ are Don't Care.})$

#### HIDDEN REFRESH CYCLE

DON'T CARE W UNDEFINED

NOTE: A HIDDEN REFRESH may also be performed after a WRITE cycle. In this case ME/WE = LOW (when CAS goes LOW) and TR/OE = HIGH.

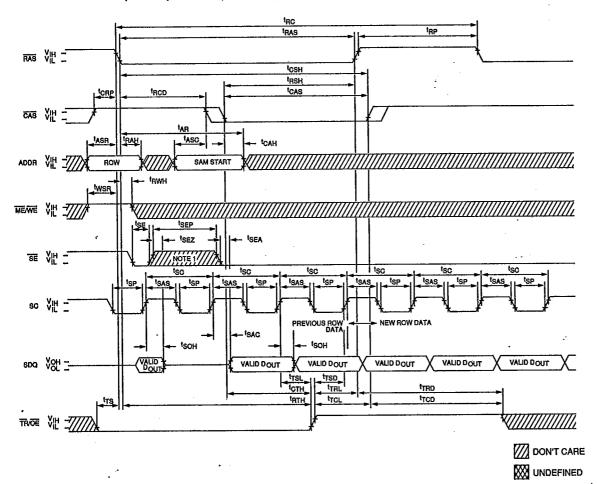

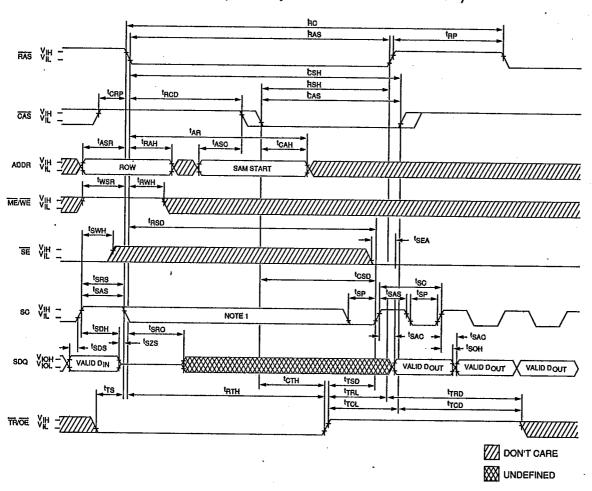

#### **DRAM-TO-SAM TRANSFER** (READ TRANSFER)

(When part was previously in the SERIAL OUTPUT mode.)

NOTE: This SE pulse is shown to illustrate the SERIAL OUTPUT ENABLE and DISABLE timing. It is not required.

T-46-23-37

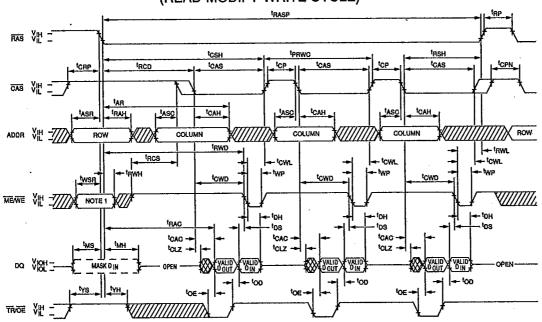

## **DRAM-TO-SAM TRANSFER** (READ TRANSFER)

(When part was previously in the SERIAL INPUT mode.)

NOTE: There must be no rising edges on the SC input during this time.

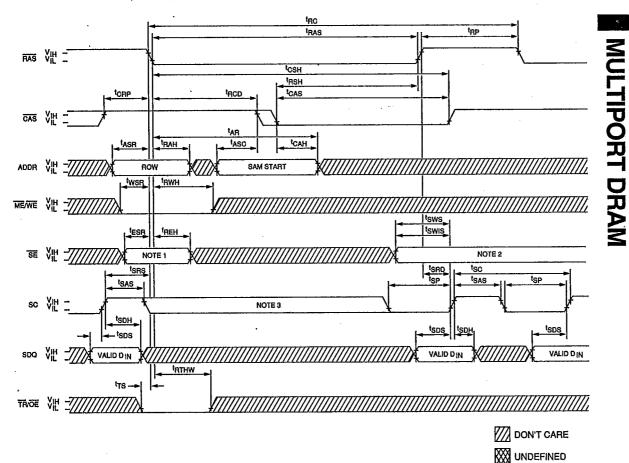

#### **SAM-TO-DRAM TRANSFER** (WRITE TRANSFER)

(When part was previously in the SERIAL INPUT mode.)

- NOTE: 1. If SE is LOW, the SAM data will be transferred to the DRAM. If SE is HIGH, the SAM data will not be transferred to the DRAM (SERIAL INPUT MODE ENABLE cycle).

- 2. SE must be LOW to input new serial data, but the serial address register is incremented by SC regardless of SE.

- 3. There must be no rising edges on the SC input during this time.

T-46-23-37

**W** UNDEFINED

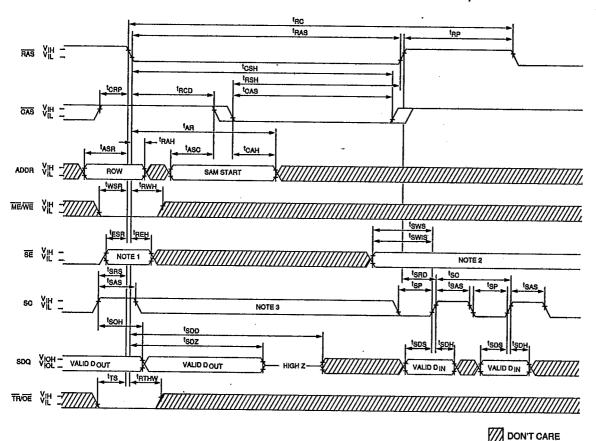

## **SAM-TO-DRAM TRANSFER** (WRITE TRANSFER or PSEUDO WRITE TRANSFER)

(When part was previously in the SERIAL OUTPUT mode.)

NOTE: 1. If SE is LOW, the SAM data will be transferred to the DRAM.

If SE is HIGH, the SAM data will not be transferred to the DRAM (SERIAL INPUT MODE ENABLE cycle).

- 2. SE must be LOW to input new serial data, but the serial address register is incremented by SC regardless of SE.

- 3. There must be no rising edges on the SC input during this time.

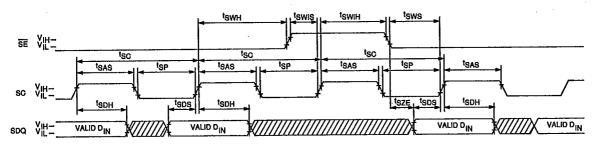

#### **SAM SERIAL INPUT**

T-46-23-37

#### **SAM SERIAL OUTPUT**

DON'T CARE

W UNDEFINED