# **DSP56004** DSP56004ROM

### SYMPHONY<sup>™</sup> AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS

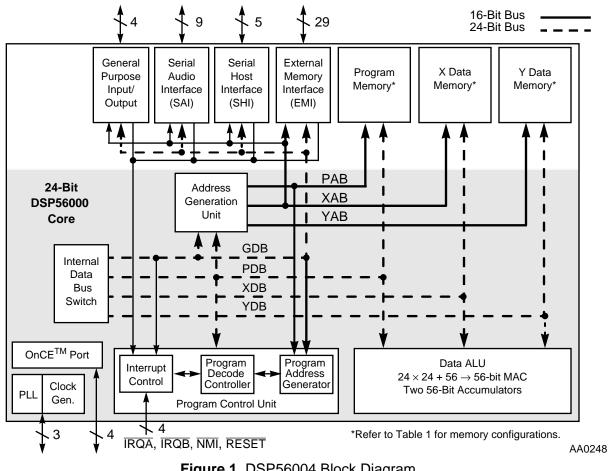

Motorola designed the Symphony<sup>™</sup> family of high-performance, programmable Digital Signal Processors (DSPs) to support a variety of digital audio applications, including Dolby ProLogic, ATRAC, and Lucasfilm Home THX processing. Software for these applications is licensed by Motorola for integration into products like audio/video receivers, televisions, and automotive sound systems with such user-developed features as digital equalization and sound field processing. The DSP56004 is an MPU-style general purpose DSP, composed of an efficient 24-bit Digital Signal Processor core, program and data memories, various peripherals optimized for audio, and support circuitry. As illustrated in Figure 1, the DSP56000 core family compatible DSP is fed by program memory, two independent data RAMs and two data ROMs, a Serial Audio Interface (SAI), Serial Host Interface (SHI), External Memory Interface (EMI), dedicated I/O lines, on-chip Phase Lock Loop (PLL), and On-Chip Emulation ( $OnCE^{TM}$ ) port.

Figure 1 DSP56004 Block Diagram

#### TABLE OF CONTENTS

| SECTION 1 | SIGNAL/CONNECTION DESCRIPTIONS |

|-----------|--------------------------------|

| SECTION 2 | SPECIFICATIONS 2-1             |

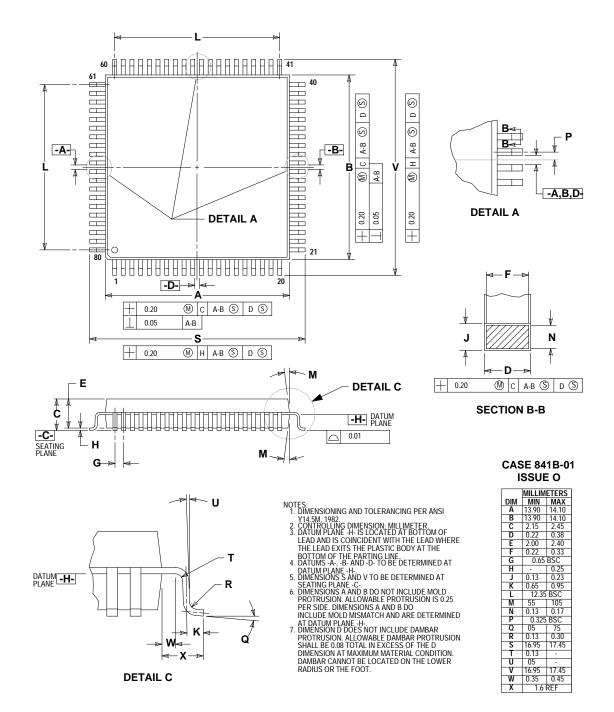

| SECTION 3 | PACKAGING                      |

| SECTION 4 | DESIGN CONSIDERATIONS 4-1      |

| SECTION 5 | ORDERING INFORMATION           |

| FOR TECHNICAL ASSISTANCE: |                             |  |  |

|---------------------------|-----------------------------|--|--|

| Telephone:                | 1-800-521-6274              |  |  |

| Email:                    | dsphelp@dsp.sps.mot.com     |  |  |

| Internet:                 | http://www.motorola-dsp.com |  |  |

|                           |                             |  |  |

## **Data Sheet Conventions**

This data sheet uses the following conventions:

| OVERBAR      | Used to indicate a signal that is active when pulled low (For example, the $\overline{\text{RESET}}$ pin is active when low.) |             |              |                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------------|

| "asserted"   | Means that a high true (active high) signal is high or that a low true (active low) signal is low                             |             |              |                 |

| "deasserted" | Means that a high true (active high) signal is low or that a low true (active low) signal is high                             |             |              |                 |

| Examples:    | Signal/Symbol                                                                                                                 | Logic State | Signal State | Voltage         |

|              | PIN                                                                                                                           | True        | Asserted     | $V_{IL}/V_{OL}$ |

|              | PIN                                                                                                                           | False       | Deasserted   | $V_{IH}/V_{OH}$ |

|              | PIN                                                                                                                           | True        | Asserted     | $V_{IH}/V_{OH}$ |

|              | PIN                                                                                                                           | False       | Deasserted   | $V_{IL}/V_{OL}$ |

Note: Values for  $V_{IL}, V_{OL}, V_{IH},$  and  $V_{OH}$  are defined by individual product specifications.

## **FEATURES**

## **Digital Signal Processing Core**

- Efficient, object code compatible with the 24-bit DSP56000 core engine

- Up to 40.5 Million Instructions Per Second (MIPS)—24.7 ns instruction cycle at 81 MHz; up to 324 Million Operations Per Second (MOPS) at 81 MHz

- Highly parallel instruction set with unique DSP addressing modes

- Two 56-bit accumulators including extension byte

- Parallel 24 × 24-bit multiply-accumulate in 1 instruction cycle (2 clock cycles)

- Double precision  $48 \times 48$ -bit multiply with 96-bit result in 6 instruction cycles

- 56-bit addition/subtraction in 1 instruction cycle

- Fractional and integer arithmetic with support for multiprecision arithmetic

- Hardware support for block floating-point Fast Fourier Transforms (FFT)

- Hardware nested DO loops

- Zero-overhead fast interrupts (2 instruction cycles)

- Four 24-bit internal data buses and three 16-bit internal address buses for simultaneous accesses to one program and two data memories

- Fabricated in high-density CMOS

### Memory

- On-chip modified Harvard architecture which permits simultaneous accesses to program and two data memories

- Bootstrap loading from Serial Host Interface or External Memory Interface

| Part Type                                                                                                                                                                                                                            | Program |     | X Data |     | Y Data |     | Boot-strap |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|-----|--------|-----|------------|--|

| TartType                                                                                                                                                                                                                             | ROM     | RAM | ROM    | RAM | ROM    | RAM | ROM        |  |

| DSP56004 <sup>1</sup>                                                                                                                                                                                                                | None    | 512 | 256    | 256 | 256    | 256 | 64         |  |

| DSP56004ROM <sup>2</sup>                                                                                                                                                                                                             | 2560    | 256 | 256    | 256 | 256    | 256 | 64         |  |

| Note: 1. X data ROM is programmed with log <sub>2</sub> x and 2 <sup>x</sup> tables; Y data ROM is programmed with a sine table.<br>2. These ROMs may be factory programmed with data/program provided by the application developer. |         |     |        |     |        |     |            |  |

**Table 1**Memory Configuration (Word width is 24 bits)

## **Peripheral and Support Circuits**

- Serial Audio Interface (SAI) includes two receivers and three transmitters, master or slave capability, implementation of I<sup>2</sup>S, Sony, and Matsushita audio protocols; and two sets of SAI interrupt vectors

- Serial Host Interface (SHI) features single master capability, 10-word receive FIFO, and support for 8-, 16-, and 24-bit words

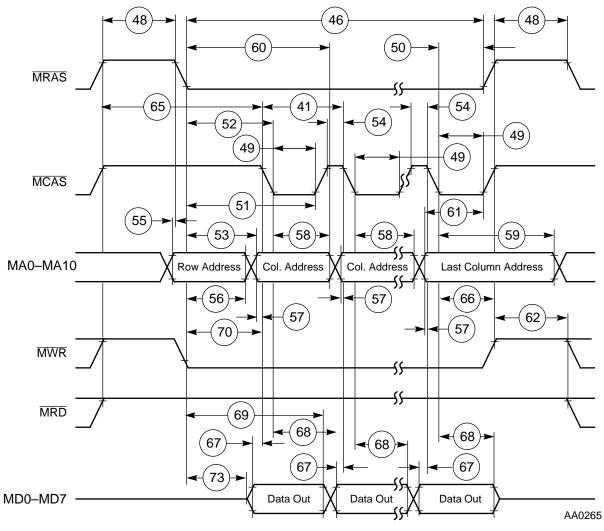

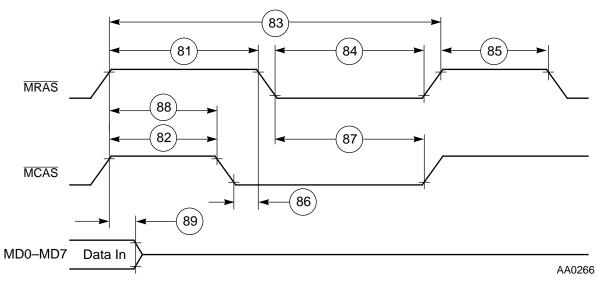

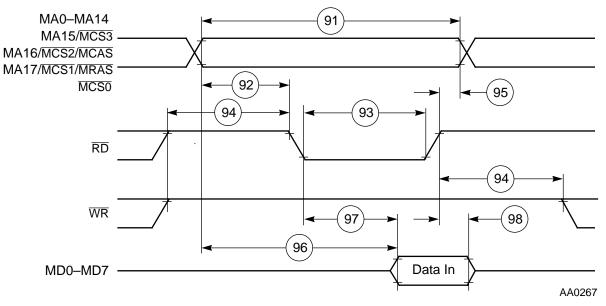

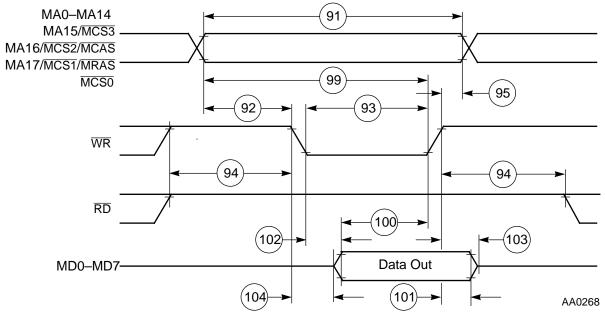

- External Memory Interface (EMI), implemented as a peripheral supporting:

- Page-mode DRAMs (one or two chips): 64 K  $\times$  4, 256 K  $\times$  4, and 4 M  $\times$  4 bits

- SRAMs (one to four): 256 K × 8 bits

- Data bus may be 4 or 8 bits wide

- Data words may be 8, 12, 16, 20, or 24 bits wide

- Four dedicated, independent, programmable General Purpose Input/Output (GPIO) lines

- On-chip peripheral registers memory mapped in data memory space

- Three external interrupt request pins

- On-Chip Emulation (OnCE) port for unobtrusive, processor speedindependent debugging

- Software-programmable, Phase Lock Loop-based (PLL) frequency synthesizer for the core clock

- Power-saving Wait and Stop modes

- Fully static, HCMOS design for operating frequencies down to dc

- 80-pin plastic Quad Flat Pack surface-mount package;  $14 \times 14 \times 2.20$  mm (2.15–2.45 mm range); 0.65 mm lead pitch

- Complete pinout compatibility between DSP56004, DSP56004ROM, DSP56007, and DSP56009 for easy upgrades

- 5 V power supply

## **PRODUCT DOCUMENTATION**

**Table 2** lists the documents that provide a complete description of the DSP56004 and are required to design properly with the part. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola DSP home page on the Internet (the source for the latest information).

| Document Name              | <b>Description of Content</b>                                                          | Order Number   |

|----------------------------|----------------------------------------------------------------------------------------|----------------|

| DSP56000 Family<br>Manual  | DSP56000 core family architecture and the 24-bit<br>core processor and instruction set | DSP56KFAMUM/AD |

| DSP56004 User's<br>Manual  | Memory, peripherals, and interfaces                                                    | DSP56004UM/AD  |

| DSP56004 Technical<br>Data | Electrical and timing specifications,<br>and pin and package descriptions              | DSP56004/D     |

| Table 2         DSP56004         Documentat |

|---------------------------------------------|

|---------------------------------------------|

<del>dsp</del>

Product Documentation

# SECTION 1

# SIGNAL/CONNECTION DESCRIPTIONS

## SIGNAL GROUPINGS

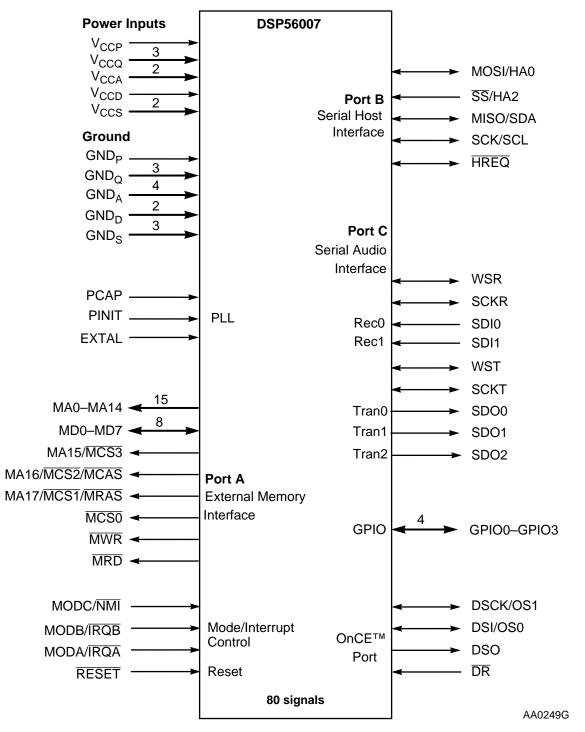

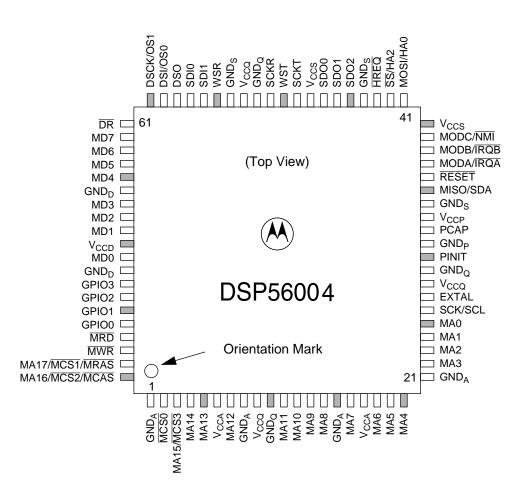

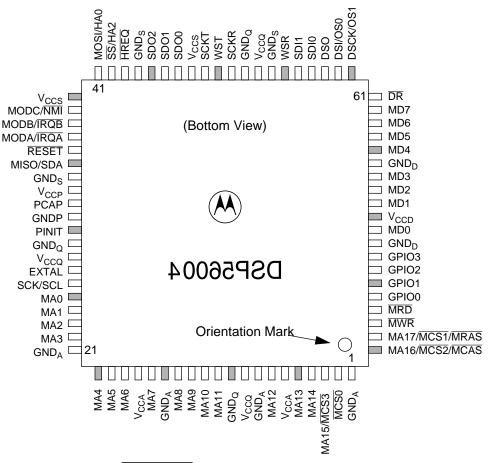

The DSP56004 input and output signals are organized into the nine functional groups, as shown in **Table 1-1**. The individual signals are illustrated in **Figure 1-1**.

| Functional Group                    | Number of Signals | Detailed Description    |

|-------------------------------------|-------------------|-------------------------|

| Power (V <sub>CC</sub> )            | 9                 | Table 1-2               |

| Ground (GND)                        | 13                | Table 1-3               |

| Phase Lock Loop (PLL)               | 3                 | Table 1-4               |

| External Memory Interface (EMI)     | 29                | Table 1-5 andTable 1-6  |

| Interrupt and Mode Control          | 4                 | Table 1-7               |

| Serial Host Interface (SHI)         | 5                 | Table 1-8               |

| Serial Audio Interface (SAI)        | 9                 | Table 1-9 andTable 1-10 |

| General Purpose Input/Output (GPIO) | 4                 | Table 1-11              |

| On-Chip Emulation (OnCE) port       | 4                 | Table 1-12              |

| Total                               | 80                |                         |

#### **Table 1-1** DSP56004 Functional Group Signal Allocations

#### Signal Groupings

Figure 1-1 DSP56004 SIgnals

Power

## POWER

| Power Name       | Description                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCP</sub> | <b>PLL Power</b> — $V_{CCP}$ provides isolated power for the Phase Lock Loop (PLL). The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail.                                                                         |

| V <sub>CCQ</sub> | <b>Quiet Power</b> — $V_{CCQ}$ provides isolated power for the internal processing logic. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors.                                                                        |

| V <sub>CCA</sub> | $\begin{array}{c} \textbf{Address Bus Power} \\ -V_{CCA} \text{ provides isolated power for sections of the address bus} \\ I/O \text{ drivers. This input must be tied externally to all other chip power inputs. The} \\ user must provide adequate external decoupling capacitors. \end{array}$ |

| V <sub>CCD</sub> | <b>Data Bus Power</b> — $V_{CCD}$ provides isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors.                                                              |

| V <sub>CCS</sub> | Serial Interface Power— $V_{CCS}$ provides isolated power for the SHI and SAI. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors.                                                                                   |

## GROUND

| Ground Name      | Description                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>P</sub> | <b>PLL Ground</b> —GND <sub>P</sub> is ground dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground. $V_{CCP}$ should be bypassed to GND <sub>P</sub> by a 0.47 $\mu$ F capacitor located as close as possible to the chip package. |

| GND <sub>Q</sub> | <b>Quiet Ground</b> — $GND_Q$ provides isolated ground for the internal processing logic.<br>This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                             |

| GND <sub>A</sub> | Address Bus Ground— $GND_A$ provides isolated ground for sections of the address bus I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                        |

| GND <sub>D</sub> | <b>Data Bus Ground</b> —GND <sub>D</sub> provides isolated ground for sections of the data bus I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                              |

| GND <sub>S</sub> | <b>Serial Interface Ground</b> —GND <sub>S</sub> provides isolated ground for the SHI and SAI. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                           |

Table 1-3

Grounds

## **CLOCK AND PLL SIGNALS**

**Note:** While the PLL on this DSP is identical to the PLL described in the *DSP56000 Family Manual*, two of the signals have not been implemented externally. Specifically, there is no PLOCK signal or CKOUT signal available. Therefore, the internal clock is not directly accessible and there is no external indication that the PLL is locked. These signals were omitted to reduce the number of pins and allow this DSP to be put in a smaller, less expensive package.

| Signal<br>Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

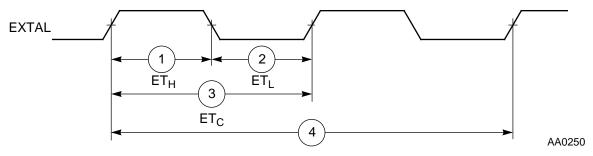

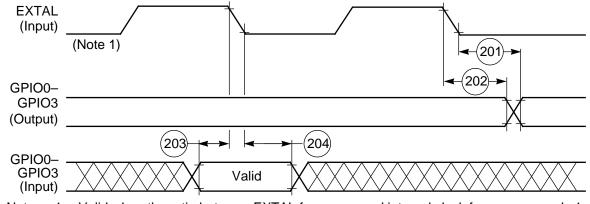

| EXTAL          | Input          | Input                    | <b>External Clock/Crystal</b> —This input should be connected to an external clock source. If the PLL is enabled, this signal is internally connected to the on-chip PLL. The PLL can multiply the frequency on the EXTAL pin to generate the internal DSP clock. The PLL output is divided by two to produce a four-phase instruction cycle clock, with the minimum instruction time being two PLL output clock periods. If the PLL is disabled, EXTAL is divided by two to produce the four-phase instruction cycle clock.                                |

| РСАР           | Input          | Input                    | <ul> <li>PLL Filter Capacitor—This input is used to connect a high-quality (high "Q" factor) external capacitor needed for the PLL filter. The capacitor should be as close as possible to the DSP with heavy, short traces connecting one terminal of the capacitor to PCAP and the other terminal to V<sub>CCP</sub>. The required capacitor value is specified in Table 2-6 on page 2-6.</li> <li>Note: When short lock time is critical, low dielectric absorption capacitors such as polystyrene, polypropylene, or teflon are recommended.</li> </ul> |

|                |                |                          | If the PLL is not used (i.e., it remains disabled at all times), there is no need to connect a capacitor to the PCAP pin. It may remain unconnected, or be tied to either $V_{cc}$ or GND.                                                                                                                                                                                                                                                                                                                                                                  |

| PINIT          | Input          | Input                    | <b>PLL Initialization (PINIT)</b> —During the assertion of hardware reset, the value on the PINIT line is written into the PEN bit of the PCTL register. When set, the PEN bit enables the PLL by causing it to derive the internal clocks from the PLL voltage controlled oscillator output. When the bit is cleared, the PLL is disabled and the DSP's internal clocks are derived from the clock connected to the EXTAL signal. After hardware RESET is deasserted, the PINIT signal is ignored.                                                         |

Table 1-4

Clock and PLL Signals

## **EXTERNAL MEMORY INTERFACE (EMI)**

| Signal Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                             |

|-------------|----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA0-MA14    | Output         | Table 1-6             | <b>Memory Address Lines 0–14</b> —The MA0–MA10 lines provide<br>the multiplexed row/column addresses for DRAM accesses.<br>Lines MA0–MA14 provide the non-multiplexed address lines<br>0–14 for SRAM accesses. |

| MA15        | Output         | Table 1-6             | <b>Memory Address Line 15 (MA15)</b> —This line functions as the non-multiplexed address line 15.                                                                                                              |

| MCS3        |                |                       | <b>Memory Chip Select 3 (</b> MCS3)—For SRAM accesses, this line functions as memory chip select 3.                                                                                                            |

| MA16        | Output         | Table 1-6             | <b>Memory Address Line 16 (MA16)</b> —This line functions as the non-multiplexed address line 16 or as memory chip select 2 for SRAM accesses.                                                                 |

| MCS2        |                |                       | <b>Memory Chip Select 2</b> (MCS2)—For SRAM access, this line functions as memory chip select 2.                                                                                                               |

| MCAS        |                |                       | <b>Memory Column Address Strobe (MCAS)</b> —This line<br>functions as the Memory Column Address Strobe (MCAS)<br>during DRAM accesses.                                                                         |

| MA17        | Output         | Table 1-6             | <b>Memory Address Line 17 (MA17)</b> —This line functions as the non-multiplexed address line 17.                                                                                                              |

| MCS1        |                |                       | <b>Memory Chip Select 1 (MCS1)</b> —This line functions as chip select 1 for SRAM accesses.                                                                                                                    |

| MRAS        |                |                       | <b>Memory Row Address Strobe (MRAS)</b> —This line also functions as the Memory Row Address Strobe during DRAM accesses.                                                                                       |

| MCS0        | Output         | Table 1-6             | <b>Memory Chip Select 0</b> —This line functions as memory chip select 0 for SRAM accesses.                                                                                                                    |

| MWR         | Output         | Table 1-6             | <b>Memory Write Strobe</b> —This line is asserted when writing to external memory.                                                                                                                             |

| MRD         | Output         | Table 1-6             | <b>Memory Read Strobe</b> —This line is asserted when reading external memory.                                                                                                                                 |

### External Memory Interface (EMI)

| Signal Name | Signal<br>Type     | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD0-MD7     | Bidi-<br>rectional | Tri-stated            | <b>Data Bus</b> —These signals provide the bidirectional data bus for<br>EMI accesses. They are inputs during reads from external<br>memory, outputs during writes to external memory, and tri-<br>stated if no external access is taking place. If the data bus width<br>is defined as four bits wide, only signals MD0–MD3 are active,<br>while signals MD4–MD7 remain tri-stated. While tri-stated,<br>MD0–MD7 are disconnected from the pins and do not require<br>external pull-ups. |

| Table 1-5 | External Memory      | Interface (EMI)   | Signals | (Continued) |

|-----------|----------------------|-------------------|---------|-------------|

| Table 1-5 | LATER MALE MILLION Y | Internace (Livii) | Signais | (Continueu) |

#### Table 1-6 EMI States during Reset and Stop States

| Signal                                                 | Operating Mode             |                            |                           |                            |  |  |

|--------------------------------------------------------|----------------------------|----------------------------|---------------------------|----------------------------|--|--|

| Signal                                                 | Hardware Reset             | Software Reset             | Individual Reset          | Stop Mode                  |  |  |

| MA0-MA14                                               | Driven High                | Previous State             | Previous State            | Previous State             |  |  |

| MA15                                                   | Driven High                | Driven High                | Previous State            | Previous State             |  |  |

| MCS3                                                   | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

| MA16                                                   | Driven High                | Driven High                | Previous State            | Previous State             |  |  |

| MCS2                                                   | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

| MCAS:<br>DRAM refresh disabled<br>DRAM refresh enabled | Driven High<br>Driven High | Driven High<br>Driven High | Driven High<br>Driven Low | Driven High<br>Driven High |  |  |

| MA17                                                   | Driven High                | Driven High                | Previous State            | Previous State             |  |  |

| MCS1                                                   | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

| MRAS:<br>DRAM refresh disabled<br>DRAM refresh enabled | Driven High<br>Driven High | Driven High<br>Driven High | Driven High<br>Driven Low | Driven High<br>Driven High |  |  |

| MCS0                                                   | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

| MWR                                                    | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

| MRD                                                    | Driven High                | Driven High                | Driven High               | Driven High                |  |  |

## INTERRUPT AND MODE CONTROL

The interrupt and mode control signals select the DSP's operating mode as it comes out of hardware reset and receives interrupt requests from external sources after reset.

| Signal Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA        | Input          | Input (MODA)          | Mode Select A—This input signal has three functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                |                       | <ul> <li>to work with the MODB and MODC signals to select<br/>the DSP's initial operating mode,</li> <li>to allow an external device to request a DSP<br/>interrupt after internal synchronization, and</li> <li>to turn on the internal clock generator when the DSP<br/>is in the Stop processing state, causing the DSP to<br/>resume processing.</li> </ul>                                                                                                                                         |

|             |                |                       | MODA is read and internally latched in the DSP when the processor exits the Reset state. The logic state present on the MODA, MODB, and MODC pins selects the initial DSP operating mode. Several clock cycles after leaving the Reset state, the MODA signal changes to the external interrupt request IRQA. The DSP operating mode can be changed by software after reset.                                                                                                                            |

| ĪRQĀ        |                |                       | <b>External Interrupt Request A</b> ( <b>IRQA</b> )—The <b>I</b> RQA input is a synchronized external interrupt request. It may be programmed to be level-sensitive or negative-edge-triggered. When the signal is edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal. However, as the fall time of the interrupt signal increases, the probability that noise on <b>I</b> RQA will generate multiple interrupts also increases. |

|             |                |                       | While the DSP is in the Stop mode, asserting $\overline{IRQA}$ gates on the oscillator and, after a clock stabilization delay, enables clocks to the processor and peripherals. Hardware reset causes this input to function as MODA.                                                                                                                                                                                                                                                                   |

Table 1-7

Interrupt and Mode Control Signals

#### Interrupt and Mode Control

| Signal Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODB        | Input          | Input (MODB)          | Mode Select B—This input signal has two functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                |                       | <ul> <li>to work with the MODA and MODC signals to select<br/>the DSP's initial operating mode, and</li> <li>to allow an external device to request a DSP<br/>interrupt after internal synchronization.</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

|             |                |                       | MODB is read and internally latched in the DSP when the processor exits the Reset state. The logic state present on the MODA, MODB, and MODC pins selects the initial DSP operating mode. Several clock cycles after leaving the Reset state, the MODB signal changes to the external interrupt request IRQB. The DSP operating mode can be changed by software after reset.                                                                                                                                                                                |

| ĪRQB        |                |                       | <b>External Interrupt Request B</b> ( <b>IRQB</b> )—The <b>IRQB</b> input is a synchronized external interrupt request. It may be programmed to be level-sensitive or negative-edge-triggered. When the signal is edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal. However, as the fall time of the interrupt signal increases, the probability that noise on <b>IRQB</b> will generate multiple interrupts also increases. Hardware reset causes this input to function as MODB. |

**Table 1-7** Interrupt and Mode Control Signals (Continued)

Interrupt and Mode Control

| Signal Name | Signal<br>Type               | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODC        | Input,<br>edge-<br>triggered | Input (MODC)          | <ul> <li>to work with the MODA and MODB signals to select<br/>the DSP's initial operating mode, and</li> <li>to allow an external device to request a DSP<br/>interrupt after internal synchronization.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                              |                       | MODC is read and internally latched in the DSP when the<br>processor exits the Reset state. The logic state present on the<br>MODA, MODB, and MODC pins selects the initial DSP<br>operating mode. Several clock cycles after leaving the Reset<br>state, the MODC signal changes to the Non-Maskable<br>Interrupt request, NMI. The DSP operating mode can be<br>changed by software after reset.                                                                                                                                                                                                                                                                                                                                        |

| NMI         |                              |                       | <b>Non-Maskable Interrupt Request</b> —The NMI input is a negative-edge-triggered external interrupt request. This is a level 3 interrupt that can not be masked out. Triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal. However, as the fall time of the interrupt signal increases, the probability that noise on NMI will generate multiple interrupts also increases. Hardware reset causes this input to function as MODC.                                                                                                                                                                                                                                                   |

| RESET       | input                        | active                | <b>RESET</b> —This input causes a direct hardware reset of the processor. When <b>RESET</b> is asserted, the DSP is initialized and placed in the Reset state. A Schmitt-trigger input is used for noise immunity. When the reset signal is deasserted, the initial DSP operating mode is latched from the MODA, MODB, and MODC signals. The DSP also samples the PINIT signal and writes its status into the PEN bit of the PLL Control Register. When the DSP comes out of the Reset state, deassertion occurs at a voltage level and is not directly related to the rise time of the RESET signal. However, the probability that noise on RESET will generate multiple resets increases with increasing rise time of the RESET signal. |

|             |                              |                       | For proper hardware reset to occur, the clock must be active,<br>since a number of clock ticks are required for proper<br>propagation of the hardware Reset state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1-7

Interrupt and Mode Control Signals (Continued)

#### Serial Host Interface (SHI)

## SERIAL HOST INTERFACE (SHI)

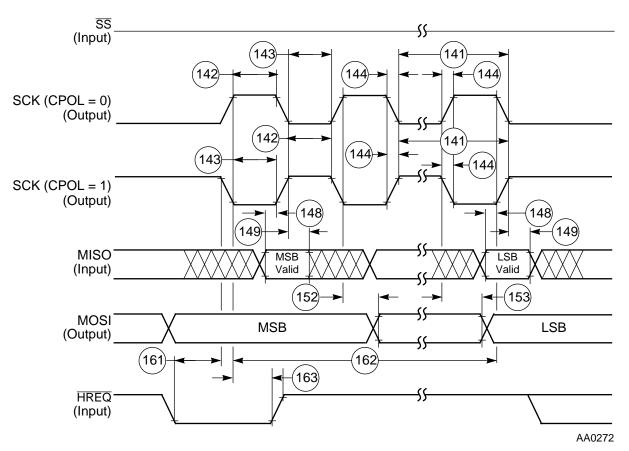

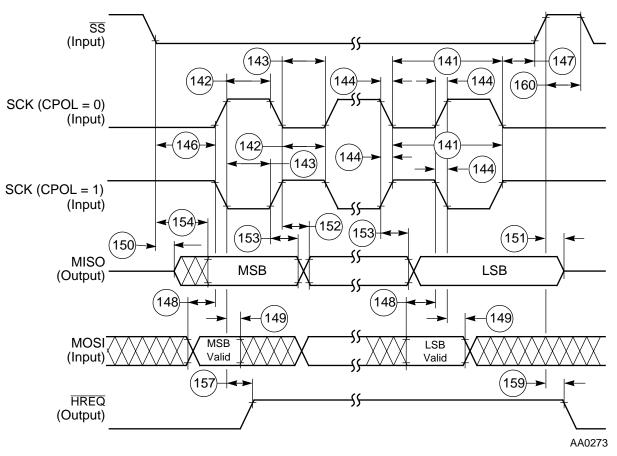

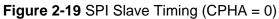

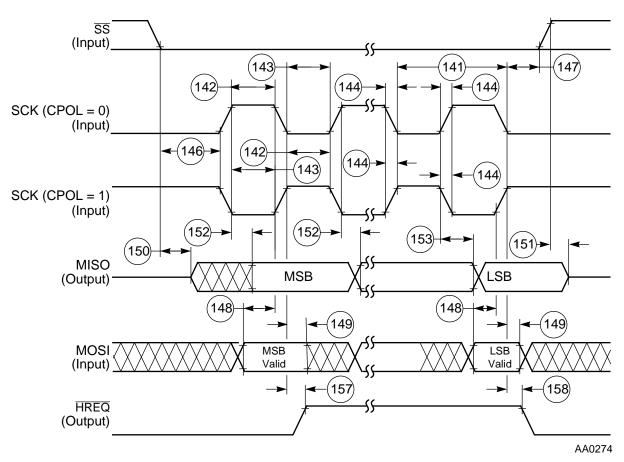

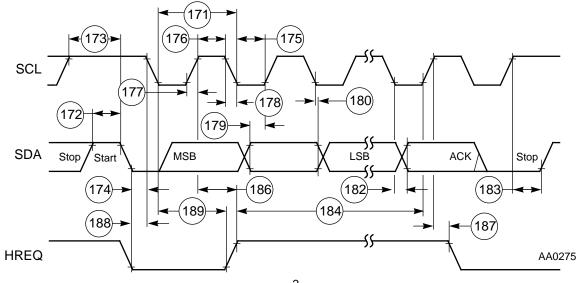

The Serial Host Interface (SHI) has five I/O signals, which may be configured to operate in either SPI or  $I^2C$  mode. **Table 1-8** lists the SHI signals.

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

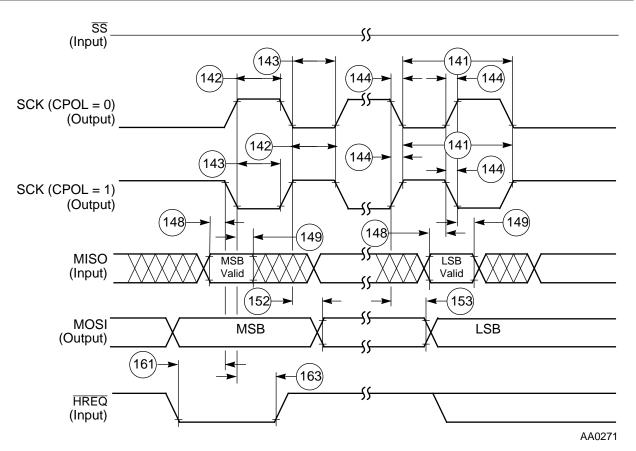

| SCK         | Input or<br>Output | Tri-stated               | <b>SPI Serial Clock (SCK)</b> —The SCK signal is an output<br>when the SPI is configured as a master, and a Schmitt-<br>trigger input when the SPI is configured as a slave. When<br>the SPI is configured as a master, the SCK signal is<br>derived from the internal SHI clock generator. When the<br>SPI is configured as a slave, the SCK signal is an input,<br>and the clock signal from the external master<br>synchronizes the data transfer. The SCK signal is ignored<br>by the SPI if it is defined as a slave and the Slave Select<br>(SS) signal is not asserted. In both the master and slave<br>SPI devices, data is shifted on one edge of the SCK signal<br>and is sampled on the opposite edge where data is stable.<br>Edge polarity is determined by the SPI transfer protocol. |

| SCL         | Input or<br>Output |                          | I <sup>2</sup> C Serial Clock (SCL)—SCL carries the clock for bus transactions in the I <sup>2</sup> C mode. SCL is a Schmitt-trigger input when configured as a slave, and an open-drain output when configured as a master. SCL should be connected to $V_{CC}$ through a pull-up resistor. The maximum allowed internally generated bit clock frequency is $^{Fosc}/_4$ for the SPI mode and $^{Fosc}/_6$ for the I <sup>2</sup> C mode where $F_{osc}$ is the clock on EXTAL. The maximum allowed externally generated bit clock frequency is $^{Fosc}/_3$ for the SPI mode and $^{Fosc}/_5$ for the I <sup>2</sup> C mode. This signal is tri-stated during hardware reset, software reset, or individual reset (no need for external pull-up in this state).                                  |

Table 1-8

Serial Host Interface (SHI) signals

Serial Host Interface (SHI)

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MISO        | Input or<br>Output | Tri-stated               | <b>SPI Master-In-Slave-Out (MISO)</b> —When the SPI is<br>configured as a master, MISO is the master data input<br>line. The MISO signal is used in conjunction with the<br>MOSI signal for transmitting and receiving serial data.<br>This signal is a Schmitt-trigger input when configured<br>for the SPI Master mode, an output when configured for<br>the SPI Slave mode, and tri-stated if configured for the<br>SPI Slave mode when $\overline{SS}$ is deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDA         | Input or<br>Output |                          | <b>I</b> <sup>2</sup> <b>C Serial Data and Acknowledge (SDA)</b> —In I <sup>2</sup> C mode,<br>SDA is a Schmitt-trigger input when receiving and an<br>open-drain output when transmitting. SDA should be<br>connected to $V_{CC}$ through a pull-up resistor. SDA carries<br>the data for I <sup>2</sup> C transactions. The data in SDA must be<br>stable during the high period of SCL. The data in SDA is<br>only allowed to change when SCL is low. When the bus<br>is free, SDA is high. The SDA line is only allowed to<br>change during the time SCL is high in the case of Start<br>and Stop events. A high-to-low transition of the SDA line<br>while SCL is high is an unique situation, and is defined<br>as the Start event. A low-to-high transition of SDA while<br>SCL is high is an unique situation, and is defined as the<br>Stop event.<br><b>Note:</b> This line is tri-stated during hardware reset, software |

|             |                    |                          | reset, or individual reset (no need for external pull-up in this state).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MOSI        | Input or<br>Output | Tri-stated               | <b>SPI Master-Out-Slave-In (MOSI)</b> —When the SPI is<br>configured as a master, MOSI is the master data output<br>line. The MOSI signal is used in conjunction with the<br>MISO signal for transmitting and receiving serial data.<br>MOSI is the slave data input line when the SPI is<br>configured as a slave. This signal is a Schmitt-trigger<br>input when configured for the SPI Slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HA0         | Input              |                          | <b>I<sup>2</sup>C Slave Address 0 (HA0)</b> —This signal uses a Schmitt-<br>trigger input when configured for the I <sup>2</sup> C mode. When<br>configured for I <sup>2</sup> C Slave mode, the HA0 signal is used to<br>form the slave device address. HA0 is ignored when the<br>SHI is configured for the I <sup>2</sup> C Master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                    |                          | <b>Note:</b> This signal is tri-stated during hardware reset, software reset, or individual reset (no need for external pull-up in this state).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 1-8

Serial Host Interface (SHI) signals (Continued)

#### Serial Host Interface (SHI)

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55          | Input              | Tri-stated               | <b>SPI Slave Select (SS)</b> —This signal is an active low<br>Schmitt-trigger input when configured for the SPI<br>mode. When configured for the SPI Slave mode, this<br>signal is used to enable the SPI slave for transfer.<br>When configured for the SPI Master mode, this<br>signal should be kept deasserted. If it is asserted<br>while configured as SPI master, a bus error<br>condition will be flagged.                                                                                                                                                                                                                                                                                           |

| HA2         | Input              |                          | <b>I<sup>2</sup>C Slave Address 2 (HA2)</b> —This signal uses a<br>Schmitt-trigger input when configured for the $I^2C$<br>mode. When configured for the $I^2C$ Slave mode, the<br>HA2 signal is used to form the slave device address.<br>HA2 is ignored in the $I^2C$ Master mode. If $\overline{SS}$ is<br>deasserted, the SHI ignores SCK clocks and keeps<br>the MISO output signal in the high-impedance<br>state.                                                                                                                                                                                                                                                                                     |

|             |                    |                          | software reset, or individual reset (no need for<br>external pull-up in this state).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HREQ        | Input or<br>Output | Tri-stated               | <b>Host Request</b> —This signal is an active low Schmitt-<br>trigger input when configured for the Master mode, but<br>an active low output when configured for the Slave<br>mode. When configured for the Slave mode, HREQ is<br>asserted to indicate that the SHI is ready for the next data<br>word transfer and deasserted at the first clock pulse of<br>the new data word transfer. When configured for the<br>Master mode, HREQ is an input and when asserted by<br>the external slave device, it will trigger the start of the<br>data word transfer by the master. After finishing the data<br>word transfer, the master will await the next assertion of<br>HREQ to proceed to the next transfer. |

|             |                    |                          | <b>Note:</b> This signal is tri-stated during hardware, software, individual reset, or when the HREQ[1:0] bits (in the HCSR) are cleared (no need for external pull-up in this state).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 1-8

Serial Host Interface (SHI) signals (Continued)

Serial Audio Interface (SAI)

## SERIAL AUDIO INTERFACE (SAI)

The SAI is composed of separate receiver and transmitter sections.

## **SAI Receiver Section**

| Signal<br>Type     | State during<br>Reset           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input              | Tri-stated                      | <ul> <li>Serial Data Input 0—While in the high impedance state, the internal input buffer is disconnected from the pin and no external pull-up is necessary. SDI0 is the serial data input for receiver 0.</li> <li>Note: This signal is high impedance during hardware or software reset, while receiver 0 is disabled (R0EN = 0), or while the DSP is in the Stop state.</li> </ul>                                                                                    |

| Input              | Tri-stated                      | <ul> <li>Serial Data Input 1—While in the high impedance state, the internal input buffer is disconnected from the pin and no external pull-up is necessary. SDI1 is the serial data input for receiver 1.</li> <li>Note: This signal is high impedance during hardware or software reset, while receiver 1 is disabled (R1EN = 0), or while the DSP is in the Stop state.</li> </ul>                                                                                    |

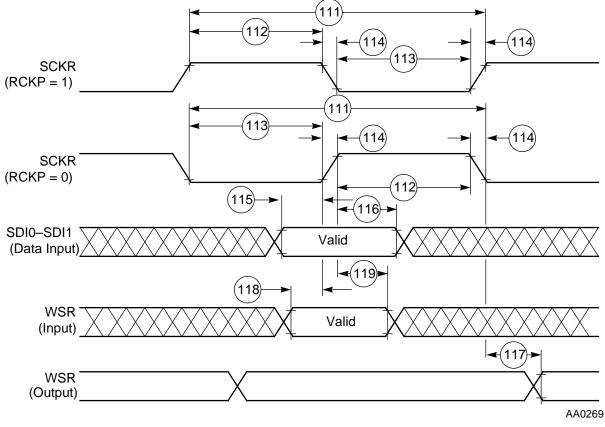

| Input or<br>Output | Tri-stated                      | <ul> <li>Receive Serial Clock—SCKR is an output if the receiver section is programmed as a master, and a Schmitt-trigger input if programmed as a slave. While in the high impedance state, the internal input buffer is disconnected from the pin and no external pull-up is necessary.</li> <li>Note: SCKR is high impedance if all receivers are disabled (individual reset) and during hardware or software reset, or while the DSP is in the Stop state.</li> </ul> |

|                    | Type<br>Input<br>Input<br>Input | Type     Reset       Input     Tri-stated       Input     Tri-stated       Input     Tri-stated       Input or     Tri-stated                                                                                                                                                                                                                                                                                                                                            |

**Table 1-9** Serial Audio Interface (SAI) Receiver signals

#### Serial Audio Interface (SAI)

| Signal | Signal             | State during | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | Type               | Reset        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WSR    | Input or<br>Output | Tri-stated   | <ul> <li>Word Select Receive (WSR)—WSR is an output if the receiver section is configured as a master, and a Schmitt-trigger input if configured as a slave. WSR is used to synchronize the data word and to select the left/right portion of the data sample.</li> <li>Note: WSR is high impedance if all receivers are disabled (individual reset), during hardware reset, during software reset, or while the DSP is in the Stop state. While in the high impedance state, the internal input buffer is disconnected from the signal and no external pull-up is necessary.</li> </ul> |

**Table 1-9** Serial Audio Interface (SAI) Receiver signals (Continued)

## **SAI Transmitter Section**

| Signal<br>Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDO0           | Output             | Driven<br>High           | <b>Serial Data Output 0 (SDO0)</b> —SDO0 is the serial output for transmitter 0. SDO0 is driven high if transmitter 0 is disabled, during individual reset, hardware reset, and software reset, or when the DSP is in the Stop state.                                                                                                                                                                                                  |

| SDO1           | Output             | Driven<br>High           | <b>Serial Data Output 1 (SDO1)</b> —SDO1 is the serial output for transmitter 1. SDO1 is driven high if transmitter 1 is disabled, during individual reset, hardware reset and software reset, or when the DSP is in the Stop state.                                                                                                                                                                                                   |

| SDO2           | Output             | Driven<br>High           | <b>Serial Data Output 2 (SDO2)</b> —SDO2 is the serial output for transmitter 2. SDO2 is driven high if transmitter 2 is disabled, during individual reset, hardware reset and software reset, or when the DSP is in the Stop state.                                                                                                                                                                                                   |

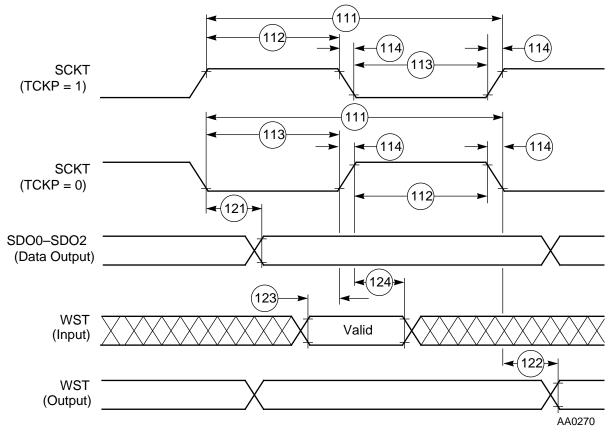

| SCKT           | Input or<br>Output | Tri-stated               | <b>Serial Clock Transmit (SCKT)</b> —This signal provides the clock for the SAI. SCKT can be an output if the transmit section is configured as a master, or a Schmitt-trigger input if the transmit section is configured as a slave. When the SCKT is an output, it provides an internally generated SAI transmit clock to external circuitry. When the SCKT is an input, it allows external circuitry to clock data out of the SAI. |

|                |                    |                          | <b>Note:</b> SCKT is high impedance if all transmitters are disabled (individual reset), during hardware reset, software reset, or while the DSP is in the Stop state. While in the high impedance state, the internal input buffer is disconnected from the pin and no external pull-up is necessary.                                                                                                                                 |

| WST            | Input or<br>Output | Tri-stated               | <b>Word Select Transmit (WST)</b> —WST is an output if the transmit section is programmed as a master, and a Schmitt-trigger input if it is programmed as a slave. WST is used to synchronize the data word and select the left/right portion of the data sample.                                                                                                                                                                      |

|                |                    |                          | <b>Note:</b> WST is high impedance if all transmitters are disabled (individual reset), during hardware or software reset, or while the DSP is in the Stop state. While in the high impedance state, the internal input buffer is disconnected from the pin and no external pull-up is necessary.                                                                                                                                      |

General Purpose I/O

## **GENERAL PURPOSE I/O**

| Signal          | Signal                                                   | State during | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|----------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | Type                                                     | Reset        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPIO0-<br>GPIO3 | Standard<br>Output,<br>Open-drain<br>Output, or<br>Input | Disconnected | <ul> <li>GPIO lines can be used for control and handshake functions between the DSP and external circuitry. Each GPIO line can be configured individually as disconnected, open-drain output, standard output, or an input.</li> <li>Note: Hardware reset or software reset configures all the GPIO lines as disconnected (external circuitry connected to these pins may need pull-ups until the pins are configured for operation).</li> </ul> |

Table 1-11

General Purpose I/O (GPIO) Signals

## **ON-CHIP EMULATION (OnCE™) PORT**

There are four signals associated with the OnCE port controller and its serial interface.

| Signal<br>Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

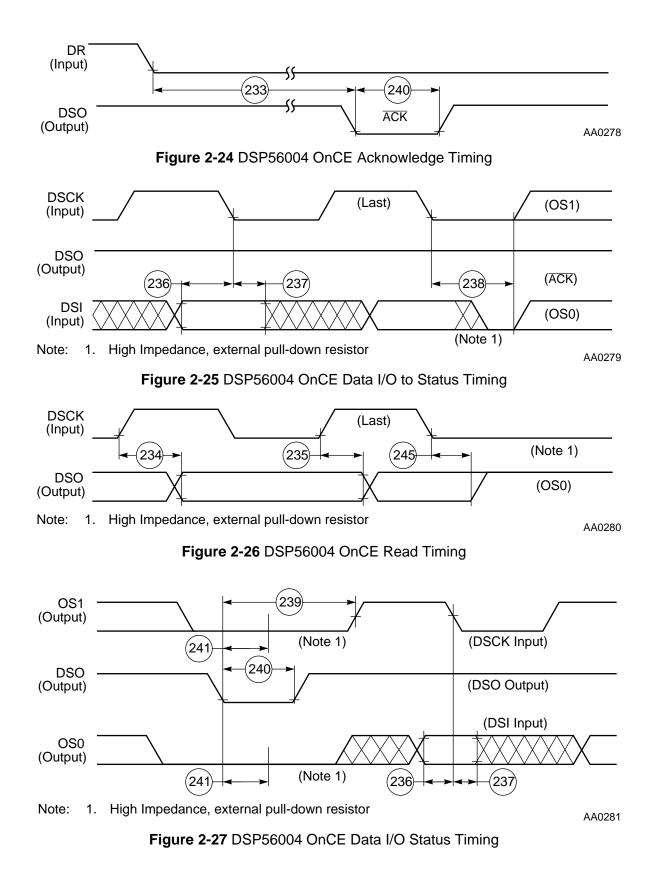

| DSI            | Input          | Output,<br>Driven Low | <b>Debug Serial Input (DSI)</b> —The DSI signal is the signal<br>through which serial data or commands are provided to the<br>OnCE port controller. The data received on the DSI signal<br>will be recognized only when the DSP has entered the<br>Debug mode of operation. Data must have valid TTL logic<br>levels before the serial clock falling edge. Data is always<br>shifted into the OnCE port Most Significant Bit (MSB) first. |

| OS0            | Output         |                       | <b>Operating Status 0 (OS0)</b> —When the DSP is not in the Debug mode, the OS0 signal provides information about the DSP status if it is an output and used in conjunction with the OS1 signal. When switching from output to input, the signal is tri-stated.                                                                                                                                                                           |

|                |                |                       | <b>Note:</b> If the OnCE port is in use, an external pull-down resistor should be attached to the DSI/OS0 signal. If the OnCE port is not in use, the resistor is not required.                                                                                                                                                                                                                                                           |

Table 1-12

On-Chip Emulation Port Signals

| Signal<br>Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

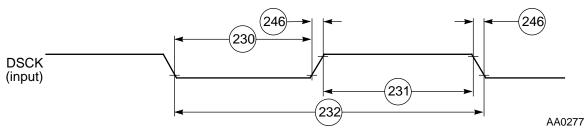

| DSCK           | Input          | Output,<br>Driven Low | <b>Debug Serial Clock (DSCK)</b> —The DSCK/OS1 signal,<br>when an input, is the signal through which the serial clock<br>is supplied to the OnCE port. The serial clock provides<br>pulses required to shift data into and out of the OnCE port.<br>Data is clocked into the OnCE port on the falling edge and<br>is clocked out of the OnCE port on the rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OS1            | Output         |                       | <ul> <li>Operating Status 1 (OS1)—If the OS1 signal is an output and used in conjunction with the OS0 signal, it provides information about the DSP status when the DSP is not in the Debug mode. The debug serial clock frequency must be no greater than 1/8 of the processor clock frequency. The signal is tri-stated when it is changing from input to output.</li> <li>Note: If the OnCE port is in use, an external pull-down resistor should be attached to the DSCK/OS1 pin. If the OnCE port is not in use, the resistor is not required.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

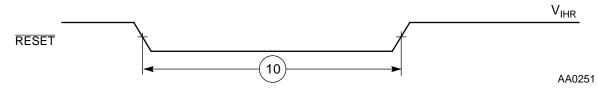

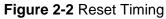

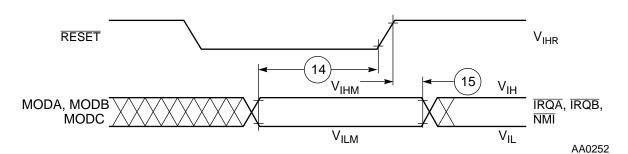

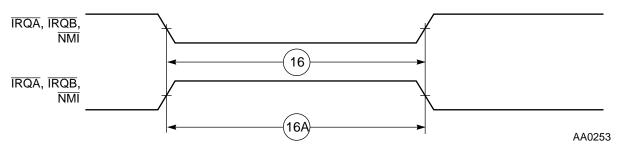

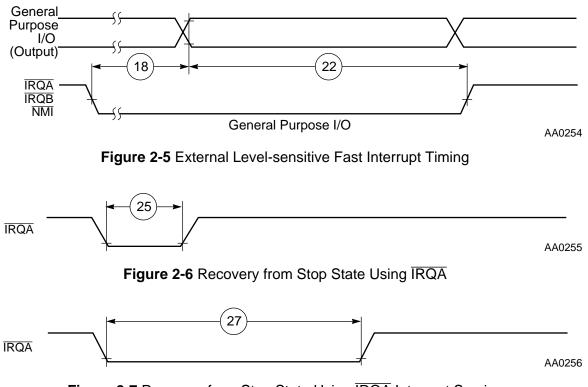

| DSO            | Output         | Driven High           | <ul> <li>Debug Serial Output (DSO)—The DSO line provides the data contained in one of the OnCE port controller registers as specified by the last command received from the command controller. The Most Significant Bit (MSB) of the data word is always shifted out of the OnCE port first. Data is clocked out of the OnCE port on the rising edge of DSCK.</li> <li>The DSO line also provides acknowledge pulses to the external command controller. When the DSP enters the Debug mode, the DSO line will be pulsed low to indicate that the OnCE port is waiting for commands. After receiving a read command, the DSO line will be pulsed low to indicate that the requested data is available and the OnCE port is ready to receive clock pulses in order to deliver the data. After receiving a write command, the DSO line will be pulsed low to indicate that the OnCE port is ready to receive the data to be written; after the data is written, another acknowledge pulse will be provided.</li> </ul> |