# XCR3032C: 32 Macrocell CPLD with Enhanced Clocking

DS040 (v1.3) October 9, 2000

### **FEATURES**

- Industry's first TotalCMOS<sup>™</sup> PLD both CMOS design and process technologies

- Fast Zero Power (FZP<sup>™</sup> design technique provides ultra-low power and very high speed

- High speed pin-to-pin delays of 8 ns

- Ultra-low static power of less than 35 μA

- 100% routable with 100% utilization while all pins and all macrocells are fixed

- Deterministic timing model that is extremely simple to use

- Up to six clocks available

- · Programmable clock polarity at every macrocell

- 3.3\/, In-System Programmable (ISP) using a JTAG interface

- On-chip supervoltage generation

- ISP commands include: Enable, Erase, Program, Verify

- Supported by multiple ISP programming platforms

- Four pin JTAG interface (TCK, TMS, TDI, TDO)

- JTAG commands include: Bypass, Idcode

- Support for complex asynchronous clocking

- Innovative XPLA<sup>™</sup> architecture combines high speed with extreme flexibility

- 1000 erase/program cycles guaranteed

- 20 years data retention guaranteed

- Logic expandable to 37 product terms

- PCI compliant

- Advanced 0.5µ E<sup>2</sup>CMOS process

- · Security bit prevents unauthorized access

- Design entry and verification using industry standard and Xilinx CAE tools

- Reprogrammable using industry standard device programmers

- Innovative Control Term structure provides either sum terms or product terms in each logic block for:

- Programmable 3-state buffer

- Asynchronous macrocell register preset/reset

- Up to two asynchronous clocks

- Programmable global 3-state pin facilitates `bed of nails' testing without using logic resources

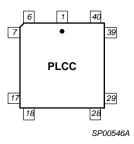

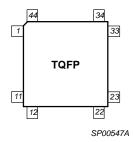

- Available in both PLCC and VQFP packages

### **Description**

**Product Specification**

The XCR3032C CPLD (Complex Programmable Logic Device) is a member of the CoolRunner® family of CPLDs from Xilinx. These devices combine high speed and zero power in a 32 macrocell CPLD. With the FZP design technique, the XCR3032C offers true pin-to-pin speeds of 8 ns, while simultaneously delivering power that is less than 35  $\mu A$  at standby without the need for "turbo bits" or other power down schemes. By replacing conventional sense amplifier methods for implementing product terms (a technique that has been used in PLDs since the bipolar era) with a cascaded chain of pure CMOS gates, the dynamic power is also substantially lower than any competing CPLD. These devices are the first TotalCMOS PLDs, as they use both a CMOS process technology and the patented full CMOS FZP design technique. For 5V applications, Xilinx also offers the high speed XCR5032C CPLD that offers pin-to-pin speeds of 6 ns.

The Xilinx FZP CPLDs utilize the patented XPLA (extended Programmable Logic Array) architecture. The XPLA architecture combines the best features of both PLA and PAL type structures to deliver high speed and flexible logic allocation that results in superior ability to make design changes with fixed pinouts. The XPLA structure in each logic block provides a fast 8 ns PAL path with five dedicated product terms per output. This PAL path is joined by an additional PLA structure that deploys a pool of 32 product terms to a fully programmable OR array that can allocate the PLA product terms to any output in the logic block. This combination allows logic to be allocated efficiently throughout the logic block and supports as many as 37 product terms on an output. The speed with which logic is allocated from the PLA array to an output is only 2.5 ns, regardless of the number of PLA product terms used, which results in worst case t<sub>PD</sub>'s of only 10.5 ns from any pin to any other pin. In addition, logic that is common to multiple outputs can be placed on a single PLA product term and shared across multiple outputs via the OR array, effectively increasing design density.

The XCR3032C CPLDs are supported by industry standard CAE tools (Cadence/OrCAD, Exemplar Logic, Mentor, Synopsys, Synario, Viewlogic, and Synplicity), using text (ABEL, VHDL, Verilog) and/or schematic entry. Design verification uses industry standard simulators for functional and timing simulation. Development is supported on personal computer, Sparc, and HP platforms. Device fitting uses a Xilinx developed tool, XPLA Professional (available on the Xilinx web site).

The XCR3032C CPLD is reprogrammable using industry standard device programmers from vendors such as Data I/O, BP Microsystems, SMS, and others. The XCR3032C also includes an industry-standard, IEEE 1149.1, JTAG interface through which In-System Programming (ISP) and reprogramming of the device are supported.

### **XPLA Architecture**

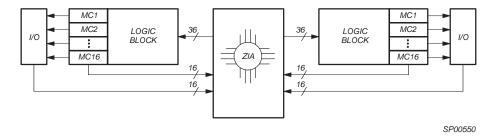

Figure 1 shows a high level block diagram of a 32 macrocell device implementing the XPLA architecture. The XPLA architecture consists of logic blocks that are interconnected by a Zero-power Interconnect Array (ZIA). The ZIA is a virtual crosspoint switch. Each logic block is essentially a 36V16 device with 36 inputs from the ZIA and 16 macrocells. Each logic block also provides 32 ZIA feedback paths from the macrocells and I/O pins.

From this point of view, this architecture looks like many other CPLD architectures. What makes the CoolRunner<sup>™</sup> family unique is what is inside each logic block and the design technique used to implement these logic blocks. The contents of the logic block will be described next.

#### Logic Block Architecture

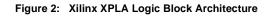

Figure 2 illustrates the logic block architecture. Each logic block contains control terms, a PAL array, a PLA array, and 16 macrocells. The six control terms can individually be configured as either SUM or PRODUCT terms, and are used to control the preset/reset and output enables of the 16 macrocells' flip-flops. In addition, two of the control terms can be used as clock signals (see Macrocell Architecture section for details). The PAL array consists of a programmable AND array with a fixed OR array, while the PLA array consists of a programmable OR array. The PAL array provides a high speed path through the array, while the PLA array provides increased product term density.

Each macrocell has five dedicated product terms from the PAL array. The pin-to-pin  $t_{PD}$  of the XCR3032C device through the PAL array is 8 ns. If a macrocell needs more than five product terms, it simply gets the additional product terms from the PLA array. The PLA array consists of 32 product terms, which are available for use by all 16 macrocells. The additional propagation delay incurred by a macrocell using one or all 32 PLA product terms is just 2.5 ns. So the total pin-to-pin  $t_{PD}$  for the XCR3032C using six to 37 product terms is 10.5 ns (8 ns for the PAL + 2.5 ns for the PLA).

Figure 1: Xilinx XPLA CPLD Architecture

6 CONTROL TO 16 MACROCELLS PAL ARRAY PLA ARRAY : • (32) SP00435A

36 ZIA INPUTS

**XILINX**<sup>®</sup>

#### Macrocell Architecture

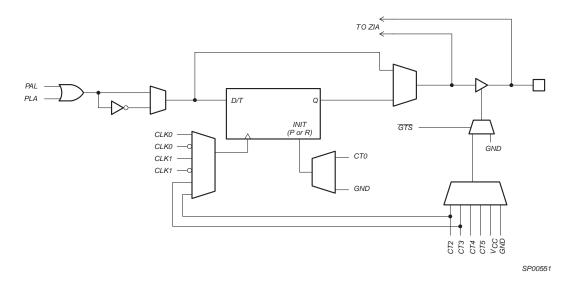

Figure 3 shows the architecture of the macrocell used in the CoolRunner XCR3032C. The macrocell can be configured as either a D- or T-type flip-flop or a combinatorial logic function. A D-type flip-flop is generally more useful for implementing state machines and data buffering while a T-type flip-flop is generally more useful in implementing counters. Each of these flip-flops can be clocked from any one of four sources. Two of the clock sources (CLK0 and CLK1) are connected to low-skew, device-wide clock networks designed to preserve the integrity of the clock signal by reducing skew between rising and falling edges. Clock 0 (CLK0) is designated as a "synchronous" clock and must be driven by an external source. Clock 1 (CLK1) can be used as a "synchronous" clock that is driven by an external source, or as an "asynchronous" clock that is driven by a macrocell equation. Both CLK0 and CLK1 can clock the macrocell flip-flops on either the rising edge or the falling edge of the clock signal. The other clock sources are two of the six control terms (CT2 and CT3) provided in each logic block. These clocks can be individually configured as either a PRODUCT term or SUM term equation created from the 36 signals available inside the logic block. The timing for asynchronous and control term clocks is different in that the Tco time is extended by the amount of time that it takes for the signal to propagate through the array and reach the clock network, and the Tsu time is reduced.

The six control terms of each logic block are used to control the asynchronous Preset/Reset of the flip-flops and the enable/disable of the output buffers in each macrocell. Control terms CT0 and CT1 are used to control the asynchronous Preset/Reset of the macrocell's flip-flop. Note that the Power-on Reset leaves all macrocells in the "zero" state when power is properly applied, and that the Preset/Reset feature for each macrocell can also be disabled. Control terms CT2 and CT3 can be used as a clock signal to the flip-flops of the macrocells, and as the Output Enable of the macrocell's output buffer. Control terms CT4 and CT5 can be used to control the Output Enable of the macrocell's output buffer. Having four dedicated Output Enable control terms ensures that the CoolRunner<sup>™</sup> devices are PCI compliant. The output buffers can also be always enabled or always disabled. All CoolRunner<sup>™</sup> devices also provide a Global 3-state (GTS) pin, which, when enabled and pulled Low, will 3-state all the outputs of the device. This pin is provided to support "In-Circuit Testing" or "Bed-of-Nails" testing.

There are two feedback paths to the ZIA: one from the macrocell, and one from the I/O pin. The ZIA feedback path before the output buffer is the macrocell feedback path, while the ZIA feedback path after the output buffer is the I/O pin feedback path. When the macrocell is used as an output, the output buffer is enabled, and the macrocell feedback path can be used to feedback the logic implemented in the macrocell. When the I/O pin is used as an input, the output buffer will be 3-stated and the input signal will be fed into the ZIA via the I/O feedback path, and the logic implemented in the buried macrocell can be fed back to the ZIA via the macrocell feedback path. It should be noted that unused inputs or I/Os should be properly terminated (See the section on "Terminations" on page 8 in this data sheet and the app note Terminating Unused I/O Pins in Xilinx CoolRunner XPLA1 and XPLA2 CPLDs.).

Figure 3: XCR3032C Macrocell Architecture

### **Simple Timing Model**

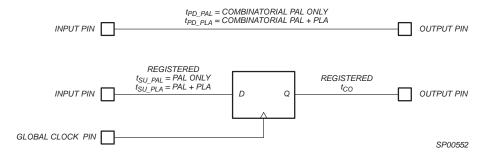

Figure 4 shows the CoolRunner Timing Model. The Cool-Runner timing model looks very much like a 22V10 timing model in that there are three main timing parameters, including  $t_{PD}$ ,  $t_{SU}$ , and  $t_{CO}$ . In other architectures, the user may be able to fit the design into the CPLD, but is not sure whether system timing requirements can be met until after the design has been fit into the device. This is because the timing models of competing architectures are very complex and include such things as timing dependencies on the number of parallel expanders borrowed, sharable expanders, varying number of X and Y routing channels used, etc. In the XPLA architecture, the user knows up front whether the design will meet system timing requirements. This is due to the simplicity of the timing model. For example, in the XCR3032C device, the user knows up front that if a given output uses five product terms or less, the  $t_{PD} = 8$  ns, the  $t_{SU} = 6.5$  ns, and the  $t_{CO} = 7.5$  ns. If an output is using six to 37 product terms, an additional 2.5 ns must be added to the  $t_{PD}$  and  $t_{SU}$  timing parameters to account for the time to propagate through the PLA array.

#### Figure 4: CoolRunner Timing Model

#### TotalCMOS Design Technique for Fast Zero Power

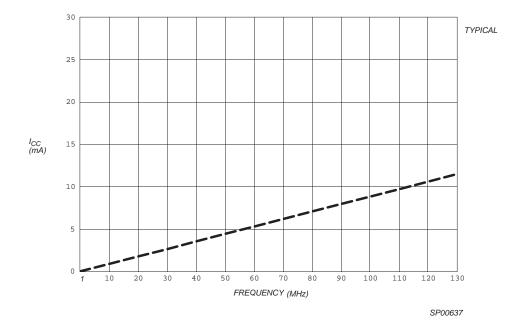

Xilinx is the first to offer a TotalCMOS CPLD, both in process technology and design technique. Xilinx employs a cascade of CMOS gates to implement its Sum of Products instead of the traditional sense amp approach. This CMOS gate implementation allows Xilinx to offer CPLDs which are both high performance and low power, breaking the paradigm that to have low power, you must have low performance. Refer to Figure 5 and Table 1 showing the I<sub>CC</sub> vs. Frequency of Xilinx' XCR3032C TotalCMOS CPLD.

#### **JTAG Testing Capability**

JTAG is the commonly-used acronym for the Boundary Scan Test (BST) feature defined for integrated circuits by IEEE Standard 1149.1. This standard defines input/output pins, logic control functions, and commands which facilitate both board and device level testing without the use of specialized test equipment. Xilinx XCR3032C devices use the JTAG interface for In-System Programming/Reprogramming. Although only a subset of the full JTAG command set is implemented (see Table 2), the devices are fully capable of sitting in a JTAG scan chain.

The Xilinx XCR3032C's JTAG interface includes a TAP Port defined by the IEEE 1149.1 JTAG Specification. As implemented in the Xilinx XCR3032C, the TAP Port includes four of the five pins (refer to Table 3) described in the JTAG

specification: TCK, TMS, TDI, and TDO. The fifth signal defined by the JTAG specification is TRST\* (Test Reset). TRST\* is considered an optional signal, since it is not actually required to perform BST or ISP. The Xilinx XCR3032C saves an I/O pin for general purpose use by not implementing the optional TRST\* signal in the JTAG interface. Instead, the Xilinx XCR3032C supports the test reset functionality through the use of its power up reset circuit, which is included in all Xilinx CPLDs. The pins associated with the TAP Port should connect to an external pull-up resistor to keep the JTAG pins from floating when they are not being used (See "Terminations" on page 8.).

In the Xilinx XCR3032C, the four mandatory JTAG pins each require a unique, dedicated pin on the device. The devices come from the factory with these I/O pins set to perform JTAG functions, but through the software, the final function of these pins can be controlled. If the end application will require the device to be reprogrammed at some future time with ISP, then the pins can be left as dedicated JTAG functions, which means they are not available for use as general purpose I/O pins. However, unlike some CPLDs, the Xilinx XCR3032C allow the macrocells associated with these pins to be used as buried logic when the JTAG/ISP function is enabled. This is the default state for the software, and no action is required to leave these pins enabled for the JTAG/ISP functions. If, however, JTAG/ISP is not required to leave these pins enabled for the JTAG/ISP functions. If, however, JTAG/ISP is not required in the end application, the software can specify that this function be turned off and that these pins be used as general purpose I/O. Because the devices initially have the JTAG/ISP functions enabled, the JEDEC file can be downloaded into the device once, after which the JTAG/ISP pins will become general purpose I/O. This feature is good for manufacturing because the devices can be programmed during test and assembly of the end product and yet still use all of the I/O pins after the programming is done. It eliminates the need for a costly, separate programming

step in the manufacturing process. Of course, if the JTAG/ISP function is never required, this feature can be turned off in the software and the device can be programmed with an industry-standard programmer, leaving the pins available for I/O functions. Table 4 defines the dedicated pins used by the four mandatory JTAG signals for each of the XCR3032C package types.

Figure 5: I<sub>CC</sub> vs. Frequency at V<sub>CC</sub> = 3.3V, 25°C

Table 1:  $I_{CC}$  vs Frequency (V<sub>CC</sub> = 3.3V, 25°C)

| Frequency (MHz)              | 0    | 1    | 10   | 20   | 30   | 40   | 50   | 60  | 70   | 80   | 90   | 100  | 110 | 120  | 130  |

|------------------------------|------|------|------|------|------|------|------|-----|------|------|------|------|-----|------|------|

| Typical I <sub>CC</sub> (mA) | 0.01 | 0.10 | 0.89 | 1.77 | 2.63 | 3.55 | 4.44 | 5.3 | 6.19 | 7.08 | 7.96 | 8.83 | 9.7 | 10.6 | 11.5 |

#### Table 2: XCR3032C Low-Level JTAG Boundary-Scan Commands

| Instruction<br>(Instruction Code)<br>Register Used | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bypass<br>(1111)<br>Bypass Register                | Places the 1 bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through the selected device to adjacent devices during normal device operation. The Bypass instruction can be entered by holding TDI at a constant high value and completing an Instruction-Scan cycle.                                             |

| ldcode<br>(0001)<br>Boundary-Scan Register         | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO. The IDCODE instruction permits blind interrogation of the components assembled onto a printed circuit board. Thus, in circumstances where the component population may vary, it is possible to determine what components exist in a product. |

#### Table 3: JTAG Pin Description

| Pin | Name              | Description                                                                                                                                                              |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК | Test Clock Output | Clock pin to shift the serial data and instructions in and out of the TDI and TDO pins, re-<br>spectively.                                                               |

| TMS | Test Mode Select  | Serial input pin selects the JTAG instruction mode. TMS should be driven high during user mode operation.                                                                |

| TDI | Test Data Input   | Serial input pin for instructions and test data. Data is shifted in on the rising edge of TCK.                                                                           |

| TDO | Test Data Output  | Serial output pin for instructions and test data. Data is shifted out on the falling edge of TCK. The signal is 3-stated if data is not being shifted out of the device. |

#### Table 4: XCR3032C JTAG Pinout by Package Type

| Device      | (Pin Number / Macrocell #) |       |      |       |  |  |  |  |

|-------------|----------------------------|-------|------|-------|--|--|--|--|

| XCR3032C    | тск                        | TMS   | TDI  | TDO   |  |  |  |  |

| 44-pin PLCC | 32/B8                      | 13/A8 | 7/A3 | 38/B3 |  |  |  |  |

| 44-pin VQFP | 26/B8                      | 7/A8  | 1/A3 | 32/B3 |  |  |  |  |

### 3.3V, In-System Programming (ISP)

ISP is the ability to reconfigure the logic and functionality of a device, printed circuit board, or complete electronic system before, during, and after its manufacture and shipment to the end customer. ISP provides substantial benefits in each of the following areas:

- Design

- Faster time-to-market

- Debug partitioning and simplified prototyping

- Printed circuit board reconfiguration during debug

- Better device and board level testing

- Manufacturing

- Multi-Functional hardware

- Reconfigurability for test

- Eliminates handling of "fine lead-pitch" components for programming

- Reduced Inventory and manufacturing costs

- Improved quality and reliability

- Field Support

- Easy remote upgrades and repair

- Support for field configuration, re-configuration, and customization

The Xilinx XCR3032C allows for 3.3V in-system programming/reprogramming of its EEPROM cells via its JTAG interface. An on-chip charge pump eliminates the need for externally-provided supervoltages, so that the XCR3032C may be easily programmed on the circuit board using only the 3.3V supply required by the device for normal operation. A set of low-level ISP basic commands implemented in the XCR3032C enable this feature. The ISP commands implemented in the Xilinx XCR3032C are specified in Table 5. Please note that an ENABLE command must precede all ISP commands **unless** an ENABLE command.

#### Table 5: Low Level ISP Commands

| Instruction<br>(Register Used)  | Instruction Code | Description                                                                                                                                                                                                    |

|---------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable<br>(ISP Shift Register)  | 1001             | Enables the Erase, Program, and Verify commands.                                                                                                                                                               |

| Erase<br>(ISP Shift Register)   | 1010             | Erases the entire EEPROM array.                                                                                                                                                                                |

| Program<br>(ISP Shift Register) | 1011             | Programs the data in the ISP Shift Register into the addressed EEPROM row.                                                                                                                                     |

| Verify<br>(ISP Shift Register)  |                  | Transfers the data from the addressed row to the ISP Shift Register. The data<br>can then be shifted out and compared with the JEDEC file. The outputs during<br>this operation can be<br>defined by the user. |

#### Terminations

The CoolRunner XCR3032C CPLDs are TotalCMOS devices. As with other CMOS devices, it is important to consider how to properly terminate unused inputs and I/O pins when fabricating a PC board. The XCR3032C devices do not have on-chip termination circuits, so it is recommended that unused inputs and I/O pins be properly terminated. Allowing unused inputs and I/O pins to float can cause the voltage to be in the linear region of the CMOS input structures, which can increase the power consumption of the device. Xilinx recommends the use of  $10K\Omega$ pull-up resistors for the termination. Using pull-up resistors allows the flexibility of using these pins should late design changes require additional I/O. These unused pins may also be tied directly to V<sub>CC</sub>, but this will make it more difficult to reclaim the use of the pin, should this be needed by a subsequent design revision.

When using the JTAG/ISP functions, it is also recommended that  $10K\Omega$  pull-up resistors be used on each of the four mandatory signals. Letting these signals float can cause the voltage on TMS to come close to ground, which could cause the device to enter JTAG/ISP mode at unspecified times. See the application notes *JTAG and ISP Overview for Xilinx XPLA1 and XPLA2 CPLDs* and *Terminating Unused I/O Pins in Xilinx XPLA1 and XPLA2 CoolRunner CPLDs* for more information.

### JTAG and ISP Interfacing

A number of industry-established methods exist for JTAG/ISP interfacing with CPLDs and other integrated circuits. The Xilinx XCR3032C supports the following methods:

- PC parallel port

- Workstation or PC serial port

- · Embedded processor

- · Automated test equipment

#### XCR3032C: 32 Macrocell CPLD with Enhanced Clocking

### **Programming Specifications**

| Symbol              | Parameter                             | Min.  | Max. | Unit |

|---------------------|---------------------------------------|-------|------|------|

| DC Param            | eters                                 | · · · | •    |      |

| V <sub>CCP</sub>    | V <sub>CC</sub> supply program/verify | 3.0   | 3.6  | V    |

| I <sub>CCP</sub>    | I <sub>CC</sub> limit program/verify  |       | 200  | mA   |

| V <sub>IH</sub>     | Input voltage (High)                  | 2.0   |      | V    |

| V <sub>IL</sub>     | Input voltage (Low)                   |       | 0.8  | V    |

| V <sub>SOL</sub>    | Output voltage (Low)                  |       | 0.5  | V    |

| V <sub>SOH</sub>    | Output voltage (High)                 | 2.4   |      | V    |

| TDO_I <sub>OL</sub> | Output current (Low)                  | 8     |      | mA   |

| TDO_I <sub>OH</sub> | Output current (High)                 | 8     |      | mA   |

| AC Param            | eters                                 | •     |      |      |

| f <sub>MAX</sub>    | TCK maximum frequency                 | 10    |      | MHz  |

| PWE                 | Pulse width erase                     | 100   |      | ms   |

| PWP                 | Pulse width program                   | 10    |      | ms   |

| PWV                 | Pulse width verify                    | 10    |      | μs   |

| INIT                | Initialization time                   | 100   |      | μs   |

| TMS_SU              | TMS setup time before TCK ↑           | 10    |      | ns   |

| TDI_SU              | TDI setup time before TCK ↑           | 10    |      | ns   |

| TMS_H               | TMS hold time after TCK ↑             | 25    |      | ns   |

| TDI_H               | TDI hold time after TCK ↑             | 25    |      | ns   |

| TDO_CO              | TDO valid after TCK $\downarrow$      |       | 40   | ns   |

### Absolute Maximum Ratings<sup>1</sup>

| Symbol           | Parameter                    | Min. | Max.                  | Unit |

|------------------|------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>2</sup>  | -0.5 | 7.0                   | V    |

| VI               | Input voltage                | -1.2 | V <sub>CC</sub> + 0.5 | V    |

| V <sub>OUT</sub> | Output voltage               | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>IN</sub>  | Input current                | -30  | 30                    | mA   |

| I <sub>OUT</sub> | Output current               | -100 | 100                   | mA   |

| TJ               | Maximum junction temperature | -40  | 150                   | °C   |

| T <sub>str</sub> | Storage temperature          | -65  | 150                   | °C   |

Notes:

1. Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification is not implied.

2. The chip supply voltage must rise monotonically.

### **Operating Range**

| Product Grade | Temperature  | Voltage       |

|---------------|--------------|---------------|

| Commercial    | 0 to +705C   | $3.3V\pm10\%$ |

| Industrial    | -40 to +855C | $3.3V\pm10\%$ |

### **DC Electrical Characteristics For Commercial Grade Devices**

Commercial:  $0^{\circ}C \le T_{AMB} \le +70^{\circ}C$ ;  $3.0V \le V_{CC} \le 3.6V$

| Symbol                           | Parameter                                 | Test Conditions                                                 | Min. | Max. | Unit |

|----------------------------------|-------------------------------------------|-----------------------------------------------------------------|------|------|------|

| V <sub>IL</sub>                  | Input voltage low                         | $V_{CC} = 3.0V$                                                 |      | 0.8  | V    |

| V <sub>IH</sub>                  | Input voltage high                        | $V_{CC} = 3.6V$                                                 | 2.0  |      | V    |

| VI                               | Input clamp voltage <sup>3</sup>          | V <sub>CC</sub> = 3.0V, I <sub>IN</sub> = -18 mA                |      | -1.2 | V    |

| V <sub>OL</sub>                  | Output voltage low                        | V <sub>CC</sub> = 3.0V, I <sub>OL</sub> = 8 mA                  |      | 0.5  | V    |

| V <sub>OH</sub>                  | Output voltage high                       | V <sub>CC</sub> = 3.0V, I <sub>OH</sub> = -8 mA                 | 2.4  |      | V    |

| IIL                              | Input leakage current low                 | V <sub>CC</sub> = 3.6V (except CKO), V <sub>IN</sub> = 0V       | -10  | 10   | μΑ   |

| I <sub>IH</sub>                  | Input leakage current high                | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 3.0V                  | -10  | 10   | μΑ   |

| IIL                              | Clock input leakage current               | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 0.4V                  | -10  | 10   | μΑ   |

| I <sub>OZL</sub>                 | 3-stated output leakage current low       | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 0.4V                  | -10  | 10   | μΑ   |

| I <sub>OZH</sub>                 | 3-stated output leakage current high      | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 3.0V                  | -10  | 10   | μΑ   |

| I <sub>CCQ</sub> <sup>1</sup>    | Standby current                           | $V_{CC} = 3.6V, T_{AMB} = 0^{\circ}C$                           |      | 35   | μΑ   |

| I <sub>CCD</sub> <sup>1, 2</sup> | Dynamic current                           | $V_{CC} = 3.6V, T_{AMB} = 0^{\circ}C \text{ at } 1 \text{ MHz}$ |      | 0.3  | mA   |

|                                  |                                           | V <sub>CC</sub> = 3.6V, T <sub>AMB</sub> = 0°C at 50 MHz        |      | 10   | mA   |

| l <sub>os</sub>                  | Short circuit output current <sup>3</sup> | One pin at a time for no longer than 1                          | -5   | -100 | mA   |

|                                  |                                           | second                                                          |      |      |      |

| CIN                              | Input pin capacitance <sup>3</sup>        | T <sub>AMB</sub> = 25°C, f = 1 MHz                              |      | 8    | pF   |

| C <sub>CLK</sub>                 | Clock input capacitance <sup>3</sup>      | T <sub>AMB</sub> = 25°C, f = 1 MHz                              | 5    | 12   | pF   |

| C <sub>I/O</sub>                 | I/O pin capacitance <sup>3</sup>          | T <sub>AMB</sub> = 25°C, f = 1 MHz                              |      | 10   | pF   |

Notes:

1. See Table 1 on page 6 for typical values.

2. This parameter measured with a 16-bit, loadable up/down counter loaded into every logic block, with all outputs disabled and unloaded. Inputs are tied to  $V_{CC}$  or ground. This parameter guaranteed by design and characterization, not testing. 3. This parameter guaranteed by design and characterization, not by test.

# AC Electrical Characteristics<sup>1</sup> For Commercial Grade Devices

Commercial:  $0^{\circ}C \le T_{AMB} \le +70^{\circ}C$ ;  $3.0V \le V_{CC} \le 3.6V$

| 0                    | Denemeter                                                                         | ;    | 8    | 1    | 0    | 1    | 2    | Unit |

|----------------------|-----------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Symbol               | Parameter                                                                         | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| t <sub>PD_PAL</sub>  | Propagation delay time, input (or feedback node) to output through PAL            | 2    | 8    | 2    | 10   | 2    | 12   | ns   |

| t <sub>PD_PLA</sub>  | Propagation delay time, input (or feedback node) to output through PAL + PLA      | 3    | 10   | 3    | 13   | 3    | 15   | ns   |

| t <sub>co</sub>      | Clock to out (global synchronous clock from pin)                                  | 2    | 6    | 2    | 9    | 2    | 11   | ns   |

| t <sub>SU PAL</sub>  | Setup time (from input or feedback node) through PAL                              | 5    |      | 8.5  |      | 10.5 |      | ns   |

| t <sub>SU_PLA</sub>  | Setup time (from input or feedback node) through PAL + PLA                        | 7    |      | 11.5 |      | 13.5 |      | ns   |

| t <sub>H</sub>       | Hold time                                                                         |      | 0    |      | 0    |      | 0    | ns   |

| t <sub>CH</sub>      | Clock High time                                                                   | 3    |      | 4    |      | 5    |      | ns   |

| t <sub>CL</sub>      | Clock Low time                                                                    | 3    |      | 4    |      | 5    |      | ns   |

| t <sub>R</sub>       | Input rise time                                                                   |      | 20   |      | 20   |      | 20   | ns   |

| t <sub>F</sub>       | Input fall time                                                                   |      | 20   |      | 20   |      | 20   | ns   |

| f <sub>MAX1</sub>    | Maximum FF toggle rate <sup>2</sup> (1/t <sub>CH</sub> + t <sub>CL</sub> )        | 167  |      | 125  |      | 100  |      | MHz  |

| f <sub>MAX2</sub>    | Maximum internal frequency <sup>2</sup> (1/t <sub>SUPAL</sub> + t <sub>CF</sub> ) | 95   |      | 63   |      | 50   |      | MHz  |

| f <sub>MAX3</sub>    | Maximum external frequency <sup>2</sup> (1/t <sub>SUPAL</sub> + t <sub>CO</sub> ) | 91   |      | 57   |      | 47   |      | MHz  |

| t <sub>BUF</sub>     | Output buffer delay time                                                          |      | 1.5  |      | 1.5  |      | 1.5  | ns   |

| t <sub>PDF_PAL</sub> | Input (or feedback node) to internal feedback node delay time through PAL         |      | 6.5  |      | 8.5  |      | 10.5 | ns   |

| t <sub>PDF_PLA</sub> | Input (or feedback node) to internal feedback node delay time through PAL + PLA   |      | 9    |      | 11.5 |      | 13.5 | ns   |

| t <sub>CF</sub>      | Clock to internal feedback node delay time                                        |      | 5.5  |      | 7.5  |      | 9.5  | ns   |

| t <sub>INIT</sub>    | Delay from valid V <sub>CC</sub> to valid reset                                   |      | 50   |      | 50   |      | 50   | μs   |

| t <sub>ER</sub>      | Input to output disable <sup>2, 3</sup>                                           |      | 11   |      | 17   |      | 19   | ns   |

| t <sub>EA</sub>      | Input to output valid <sup>2</sup>                                                |      | 11   |      | 17   |      | 19   | ns   |

| t <sub>RP</sub>      | Input to register preset <sup>2</sup>                                             |      | 14   |      | 18   |      | 20   | ns   |

| t <sub>RR</sub>      | Input to register reset <sup>2</sup>                                              |      | 14   |      | 21   |      | 23   | ns   |

Notes:

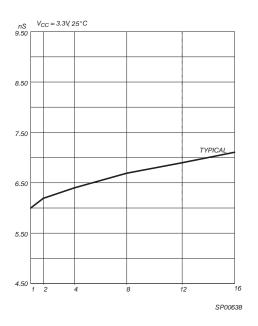

1. Specifications measured with one output switching. See Figure 6 and Table 6 for derating.

2. This parameter guaranteed by design and characterization, not by test. 3. Output  $C_L = 5 \text{ pF}$ .

### **DC Electrical Characteristics For Industrial Grade Devices**

Industrial: -40°C  $\leq$  T<sub>AMB</sub>  $\leq$  +85°C; 3.0V  $\leq$  V<sub>CC</sub>  $\leq$  3.6V

| Symbol                        | Parameter                                 | Test Conditions                                                   | Min. | Max. | Unit |

|-------------------------------|-------------------------------------------|-------------------------------------------------------------------|------|------|------|

| V <sub>IL</sub>               | Input voltage Low                         | $V_{CC} = 3.0V$                                                   |      | 0.8  | V    |

| V <sub>IH</sub>               | Input voltage High                        | V <sub>CC</sub> = 3.6V                                            | 2.0  |      | V    |

| VI                            | Input clamp voltage <sup>1</sup>          | V <sub>CC</sub> = 3.0V, I <sub>IN</sub> = -18 mA                  |      | -1.2 | V    |

| V <sub>OL</sub>               | Output voltage Low                        | V <sub>CC</sub> = 3.0V, I <sub>OL</sub> = 8 mA                    |      | 0.5  | V    |

| V <sub>OH</sub>               | Output voltage High                       | V <sub>CC</sub> = 3.0V, I <sub>OH</sub> = -8 mA                   | 2.4  |      | V    |

| IIL                           | Input leakage current Low                 | $V_{CC} = 3.6V$ (except CKO), $V_{IN} = 0.4V$                     | -10  | 10   | μΑ   |

| I <sub>IH</sub>               | Input leakage current High                | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 3.0V                    | -10  | 10   | μΑ   |

| IIL                           | Clock input leakage current               | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 0.4V                    | -10  | 10   | μΑ   |

| I <sub>OZL</sub>              | 3-stated output leakage current Low       | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 0.4V                    | -10  | 10   | μΑ   |

| I <sub>OZH</sub>              | 3-stated output leakage current           | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 3.0V                    | -10  | 10   | μΑ   |

|                               | High                                      |                                                                   |      |      |      |

| I <sub>CCQ</sub>              | Standby current                           | V <sub>CC</sub> = 3.6V, T <sub>AMB</sub> = -40°C                  |      | 45   | μA   |

| I <sub>CCD</sub> <sup>2</sup> | Dynamic current                           | $V_{CC} = 3.6V, T_{AMB} = -40^{\circ}C \text{ at } 1 \text{ MHz}$ |      | 0.5  | mA   |

|                               |                                           | $V_{CC} = 3.6V$ , $T_{AMB} = -40^{\circ}C$ at 50 MHz              |      | 18   | mA   |

| I <sub>OS</sub>               | Short circuit output current <sup>1</sup> | One pin at a time for no longer than                              | -5   | -120 | mA   |

|                               |                                           | 1 second                                                          |      |      |      |

| CIN                           | Input pin capacitance                     | T <sub>AMB</sub> = 25°C, f = 1 MHz                                |      | 8    | pF   |

| C <sub>CLK</sub>              | Clock input capacitance                   | T <sub>AMB</sub> = 25°C, f = 1 MHz                                | 5    | 12   | pF   |

| C <sub>I/O</sub>              | I/O pin capacitance                       | T <sub>AMB</sub> = 25°C, f = 1 MHz                                |      | 10   | pF   |

Notes:

1. This parameter guaranteed by design and characterization, not by test.

This parameter measured with a 16-bit, loadable up/down counter loaded into every logic block, with all outputs disabled and unloaded. Inputs are tied to V<sub>CC</sub> or ground. This parameter guaranteed by design and characterization, not testing.

# AC Electrical Characteristics<sup>1</sup> For Industrial Grade Devices

Industrial: -40°C  $\leq$   $T_{AMB}$   $\leq$  +85°C; 3.0V  $\leq$   $V_{CC}$   $\leq$  3.6V

| Cumb al              | Baramatar                                                                          | 1    | 0    | 1    | 2                                                                               | 11   |

|----------------------|------------------------------------------------------------------------------------|------|------|------|---------------------------------------------------------------------------------|------|

| Symbol               | Parameter                                                                          | Min. | Max. | Min. | Max.   12   15   11   0   20   20   20   1.5   10.5   13.5   9.5   50   19   20 | Unit |

| t <sub>PD PAL</sub>  | Propagation delay time, input (or feedback node) to output through PAL             | 2    | 10   | 2    | 12                                                                              | ns   |

| t <sub>PD_PLA</sub>  | Propagation delay time, input (or feedback node) to output through<br>PAL + PLA    | 3    | 12.5 | 3    | 15                                                                              | ns   |

| t <sub>CO</sub>      | Clock to out delay time                                                            | 2    | 9    | 2    | 11                                                                              | ns   |

| t <sub>SU_PAL</sub>  | Setup time (from input or feedback node) through PAL                               | 8    |      | 10.5 |                                                                                 | ns   |

| t <sub>SU_PLA</sub>  | Setup time (from input or feedback node) through PAL + PLA                         | 10.5 |      | 13.5 |                                                                                 | ns   |

| t <sub>H</sub>       | Hold time                                                                          |      | 0    |      | 0                                                                               | ns   |

| t <sub>CH</sub>      | Clock High time                                                                    | 4    |      | 5    |                                                                                 | ns   |

| t <sub>CL</sub>      | Clock Low time                                                                     | 4    |      | 5    |                                                                                 | ns   |

| t <sub>R</sub>       | Input rise time                                                                    |      | 20   |      | 20                                                                              | ns   |

| t <sub>F</sub>       | Input fall time                                                                    |      | 20   |      | 20                                                                              | ns   |

| f <sub>MAX1</sub>    | Maximum FF toggle rate <sup>2</sup> (1/t <sub>CH</sub> + t <sub>CL</sub> )         | 125  |      | 100  |                                                                                 | MHz  |

| f <sub>MAX2</sub>    | Maximum internal frequency <sup>2</sup> (1/t <sub>SUPAL</sub> + t <sub>CF</sub> )  | 64.5 |      | 50   |                                                                                 | MHz  |

| f <sub>MAX3</sub>    | Maximum external frequency <sup>2</sup> (1/t <sub>SUPAL</sub> + t <sub>CO</sub> )  | 58.8 |      | 47   |                                                                                 | MHz  |

| t <sub>BUF</sub>     | Output buffer delay time                                                           |      | 1.5  |      | 1.5                                                                             | ns   |

| t <sub>PDF_PAL</sub> | Input (or feedback node) to internal feedback node delay time through PAL          |      | 8    |      | 10.5                                                                            | ns   |

| t <sub>PDF_PLA</sub> | Input (or feedback node) to internal feedback node delay time through<br>PAL + PLA |      | 10.5 |      | 13.5                                                                            | ns   |

| t <sub>CF</sub>      | Clock to internal feedback delay time                                              |      | 7.5  |      | 9.5                                                                             | ns   |

| t <sub>INIT</sub>    | Delay from valid V <sub>CC</sub> to valid reset                                    |      | 50   |      | 50                                                                              | μs   |

| t <sub>ER</sub>      | Input to output disable <sup>2, 3</sup>                                            |      | 16   |      | 19                                                                              | ns   |

| t <sub>EA</sub>      | Input to output valid <sup>2</sup>                                                 |      | 16   |      | 19                                                                              | ns   |

| t <sub>RP</sub>      | Input to register preset <sup>2</sup>                                              |      | 17   |      | 20                                                                              | ns   |

| t <sub>RR</sub>      | Input to register reset <sup>2</sup>                                               |      | 20   |      | 23                                                                              | ns   |

Notes:

1. Specifications measured with one output switching. See Figure 6 and Table 6 for derating.

2. This parameter guaranteed by design and characterization, not by test.

3. Output  $C_L = 5 \text{ pF}$ .

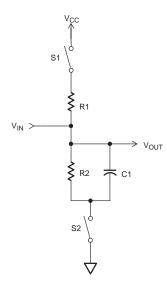

### **Switching Characteristics**

The test load circuit and load values for the AC Electrical Characteristics are illustrated below.

| COMPONENT | VALUES |

|-----------|--------|

| R1        | 390Ω   |

| R2        | 390Ω   |

| C1        | 35 pF  |

| MEASUREMENT      | S1     | S2     |

|------------------|--------|--------|

| t <sub>PZH</sub> | Open   | Closed |

| t <sub>PZL</sub> | Closed | Closed |

| tp               | Closed | Closed |

**Note:** For  $t_{PHZ}$  and  $t_{PLZ}$  C = 5 pF, and 3-state levels are measured 0.5V from steady-state active level.

SP00477

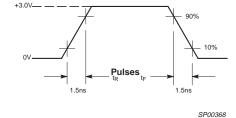

MEASUREMENTS: All circuit delays are measured at the +1.5V level of inputs and outputs, unless otherwise specified.

Input

Table 6:  $t_{PD\_PAL}$  vs # of Outputs Switching (V<sub>CC</sub> = 3.3 V, T = 25°C)

| # of Outputs | 1   | 2   | 4   | 8   | 12  | 16  |

|--------------|-----|-----|-----|-----|-----|-----|

| Typical (ns) | 6.0 | 6.2 | 6.4 | 6.7 | 6.9 | 7.1 |

### **Pin Function and Layout**

### XCR3032C I/O Pins

| Function<br>Block | Macrocell | PC44 | VQ44 | Notes |

|-------------------|-----------|------|------|-------|

| 1                 | 1         | 4    | 42   |       |

| 1                 | 2         | 5    | 43   |       |

| 1                 | 3         | 6    | 44   |       |

| 1                 | 4         | 7    | 1    | (1)   |

| 1                 | 5         | 8    | 2    |       |

| 1                 | 6         | 9    | 3    |       |

| 1                 | 7         | 11   | 5    |       |

| 1                 | 8         | 12   | 6    |       |

| 1                 | 9         | 13   | 7    | (1)   |

| 1                 | 10        | 14   | 8    |       |

| 1                 | 11        | 16   | 10   |       |

| 1                 | 12        | 17   | 11   |       |

| 1                 | 13        | 18   | 12   |       |

| 1                 | 14        | 19   | 13   |       |

| 1                 | 15        | 20   | 14   |       |

| 1                 | 16        | 21   | 15   |       |

| 2                 | 1         | 41   | 35   |       |

| 2                 | 2         | 40   | 34   |       |

| 2                 | 3         | 39   | 33   |       |

| 2                 | 4         | 38   | 32   | (1)   |

| 2                 | 5         | 37   | 31   |       |

| 2                 | 6         | 36   | 30   |       |

| 2                 | 7         | 34   | 28   |       |

| 2                 | 8         | 33   | 27   |       |

| 2                 | 9         | 32   | 26   | (1)   |

| 2                 | 10        | 31   | 25   |       |

| 2                 | 11        | 29   | 23   |       |

| 2                 | 12        | 28   | 22   |       |

| 2                 | 13        | 27   | 21   |       |

| 2                 | 14        | 26   | 20   |       |

| 2                 | 15        | 25   | 19   |       |

| 2                 | 16        | 24   | 18   |       |

(1) JTAG pins

# XCR3032C Global, JTAG, Power, and Ground Pins

| Pin Type | PC44              | VQ44          | Notes |

|----------|-------------------|---------------|-------|

| IN0      | 43                | 37            |       |

| IN1      | 1                 | 39            |       |

| IN2      | 44                | 38            |       |

| IN3      | 2                 | 40            |       |

| gtsn     | 44                | 38            | (1)   |

| CLK0     | 43                | 37            |       |

| CLK1     | 4                 | 42            |       |

| TCK      | 32                | 26            |       |

| TDI      | 7                 | 1             |       |

| TDO      | 38                | 32            |       |

| TMS      | 13                | 7             |       |

| Vcc      | 3, 15, 23, 35     | 9, 17, 29, 41 |       |

| GND      | 10, 22, 30,<br>42 | 4, 16, 24, 36 |       |

(1) Global 3-State pin facilitates bed of nails testing without using logic resources.

### XCR3032C - 44-pin PLCC

### XCR3032C - 44-pin VQFP

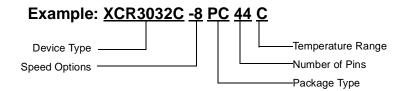

### **Ordering Information**

#### **Speed Options**

-12: 12 ns pin-to-pin delay -10: 10 ns pin-to-pin delay -8: 8 ns pin-to-pin delay

#### **Temperature Range**

C = Commercial,  $T_A = 0^{\circ}C$  to +70°C I = Industrial,  $T_A = -40^{\circ}C$  to +85°C

**Packaging Options**

VQ44: 44-pin VQFP PC44: 44-pin PLCC

### **Component Availability**

| Pins     |     |              | 44           |

|----------|-----|--------------|--------------|

| Туре     |     | Plastic VQFP | Plastic PLCC |

| Code     |     | VQ44         | PC44         |

| XCR3032C | -12 | C, I         | C, I         |

|          | -10 | C, I         | C, I         |

|          | -8  | С            | С            |

### **Revision History**

| Date     | Version # | Revision                                |  |

|----------|-----------|-----------------------------------------|--|

| 8/3/99   | 1.0       | Initial Xilinx release.                 |  |

| 2/10/00  | 1.1       | Converted to Xilinx format and updated. |  |

| 8/10/00  | 1.2       | Updated features and pinout table.      |  |

| 10/09/00 | 1.3       | Added Discontinuation Notice.           |  |