# CX74017

## RF Transceiver for Single, Dual, or Tri-Band GSM/GPRS Applications

Conexant's CX74017 transceiver is a highly integrated device for use in multi-band, Global System for Mobile communications<sup>®</sup> (GSM<sup>®</sup>) applications or General Packet Radio Service (GPRS) applications. The device requires a minimal number of external components to complete a GSM radio subsystem.

The device's receiver uses a direct down-conversion architecture that eliminates the need for Intermediate Frequency (IF) components. The receiver consists of integrated Low Noise Amplifiers (LNAs), a quadrature demodulator, tunable receiver baseband filters, and a DC offset correction sequencer.

In the transmit path, the device consists of an In-phase and Quadrature (I/Q) modulator within a frequency translation loop designed to perform frequency upconversion with high output spectral purity. This loop also contains a phasefrequency detector, a charge pump, a mixer, and buffers for the required isolation between RF output, Local Oscillator (LO), and IF ports. The transmitter also includes the entire transmit Voltage Controlled Oscillator (VCO) structure with no external tank required.

The CX74017 also features an integrated, fully programmable, fractional-N synthesizer suitable for GPRS multi-slot operation. With the exception of the loop filter, the frequency synthesizer function is completely on-chip.

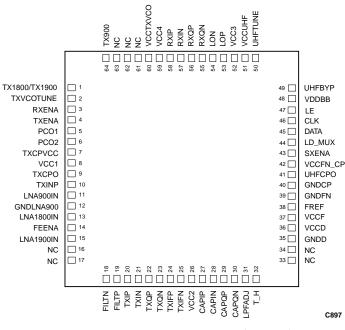

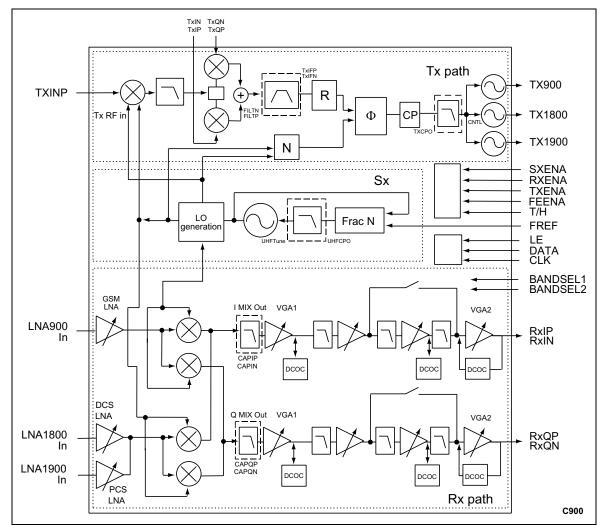

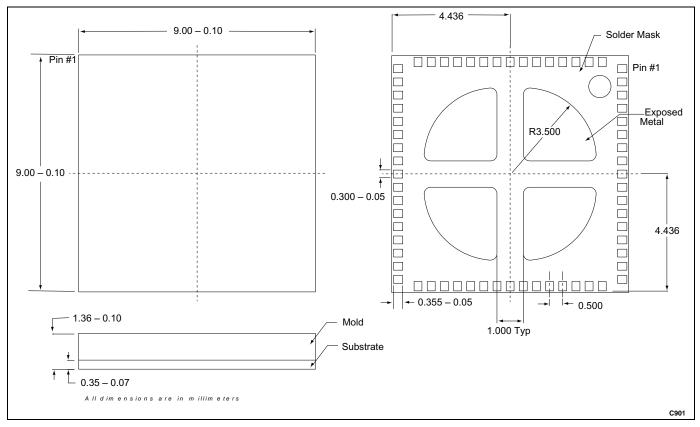

The CX74017 device package and pin configuration are shown in Figure 1. A functional block diagram is shown in Figure 2. The signal pin assignments and functional pin descriptions are provided in Table 1.

Figure 1. CX74017 Pinout – 64-Pin LGA (Top View)

#### Features

- Direct down-conversion receiver eliminates the external image reject/IF filters

- Integrated triple band LNAs with three separate inputs

- 18 dB of RF gain range and 100 dB of baseband gain range

- Gain selectable in 2 dB steps

- Integrated receive baseband filters with tunable bandwidth

- Integrated DC offset correction sequencer

- Reduced filtering requirements with translation loop transmit architecture

- Integrated transmit VCOs

- Wide RF range for dual/ triple band operation

- Single integrated, fully programmable fractional-N synthesizer suitable for multi-slot GPRS operation

- Fully integrated UHF VCO

- Separate enable lines for power management transmit, receive, and synthesizer modes

- Supply voltage down to 2.7 V

- Low external component count

- Optional bypass of baseband filtering for use with high dynamic range Analog/Digital Converters (ADCs) for current savings

- Interfaces to low dynamic range ADC

- No digital post-processing required

- 64-pin Land Grid Array (LGA) 9x9mm package

#### Applications

- GSM single, dual, or tri-band handsets with multislot capability

- · GPRS handsets and modules

Figure 2. CX74017 Transceiver Block Diagram

## **Technical Description**

The CX74017 transceiver contains a receive path, a transmit path, and a synthesizer section as shown in Figure 2. The receive path consists of a triple band integrated LNA, quadrature demodulator section that performs direct down conversion, and baseband amplifier circuitry with I/Q outputs and three stages of DC offset correction. The transmit path consists of a vector modulator within a translation loop for frequency up-conversion. The fully integrated on-chip oscillator locked in an integrated fractional-N synthesizer loop comprises the synthesizer section. Each section of the CX74017 is separately enabled via the enable signals TXENA, RXENA, and SXENA.

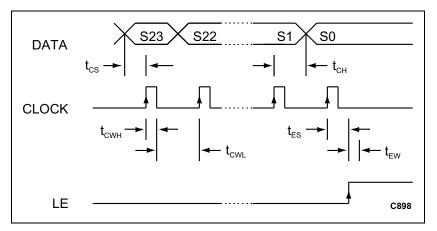

To control different modes of operation, a serial 24-bit word (bits S0 to S23) is written to the on-chip register. This 24-bit word is programmed using the 3-wire input signals CLK, DATA, and LE. To ensure that the data stays latched, the CX74017 must continue to be supplied with voltage although none of the

sections needs to be enabled. A separate power supply pin is provided for the digital sections that allow power supply operation compatible with modern digital baseband devices.

#### Receive Path

The receive path of the CX74017 consists of an RF section and a baseband section. The RF section includes a programmable gain LNA and quadrature demodulator for each band. The baseband I/Q paths are made up of cascaded amplifier and low pass filter sections. An off-chip capacitor and three fixed poles of on-chip filtering provide rejection of strong in- and out-of-band blockers. A tunable, four-pole filter provides rejection of the adjacent channel blockers. Incorporated within the fixed pole filters are two switchable gain stages of 18 dB and 12 dB gain steps, respectively. Incorporated into the four- pole tunable filter is another programmable gain amplifier with a gain range from -2 to +32 dB, selectable in 2 dB steps. The output of the final filter feeds a rail-to-rail amplifier with a gain range from 0 to 30 dB, selectable in 6 dB steps.

| Pin # | Name          | Description                                  | Pin # | Name     | Description                                    |

|-------|---------------|----------------------------------------------|-------|----------|------------------------------------------------|

| 1     | TX1800/TX1900 | DCS and PCS transmit VCO output (NC)         | 33    | NC       | No connect                                     |

| 2     | TXVCOTUNE     | Transmit VCO control input                   | 34    | NC       | No connect                                     |

| 3     | RXENA         | Receiver enable input                        | 35    | GNDD     | Synthesizer digital ground                     |

| 4     | TXENA         | Transmitter enable input                     | 36    | VCCD     | Synthesizer digital supply                     |

| 5     | PCO1          | Bi-directional control                       | 37    | VCCF     | Synthesizer analog supply                      |

| 6     | PCO2          | Bi-directional control                       | 38    | FREF     | Crystal reference input                        |

| 7     | TXCPVCC       | Transmit charge pump supply                  | 39    | GNDFN    | Synthesizer analog ground                      |

| 8     | VCC1          | LNA/transmit charge pump supply (LNA supply) | 40    | GNDCP    | Synthesizer charge pump ground                 |

| 9     | ТХСРО         | Translation loop charge pump output          | 41    | UHFCPO   | Synthesizer charge pump output                 |

| 10    | TXINP         | Translation loop feedback input              | 42    | VCCFN_CP | Synthesizer charge pump supply                 |

| 11    | LNA900IN      | EGSM LNA input                               | 43    | SXENA    | Synthesizer enable input                       |

| 12    | GNDLNA900     | EGSM LNA emitter ground                      | 44    | LD_MUX   | Synthesizer test output                        |

| 13    | LNA1800IN     | DCS LNA input                                | 45    | DATA     | Data                                           |

| 14    | FEENA         | Bi-directional front end enable input/output | 46    | CLK      | Clock                                          |

| 15    | LNA1900IN     | PCS LNA input                                | 47    | LE       | Latch enable                                   |

| 16    | NC            | No connect                                   | 48    | VDDBB    | Digital CMOS supply                            |

| 17    | NC            | No connect                                   | 49    | UHFBYP   | Bypass capacitor for UHF VCO (NC)              |

| 18    | FILTN         | TX IF output negative                        | 50    | UHFTUNE  | UHF VCO control input (NC)                     |

| 19    | FILTP         | TX IF output positive                        | 51    | VCCUHF   | UHF VCO supply                                 |

| 20    | TXIP          | TX I baseband input positive                 | 52    | VCC3     | LO chain supply                                |

| 21    | TXIN          | TX I baseband input negative                 | 53    | LOP      | External LO input/internal LO monitor positive |

| 22    | TXQP          | TX Q baseband input positive                 | 54    | LON      | External LO input/internal LO monitor negative |

| 23    | TXQN          | TX Q baseband input negative                 | 55    | RXQN     | Receiver output Q negative                     |

| 24    | TXIFP         | TX IF filter output positive                 | 56    | RXQP     | Receiver output Q positive                     |

| 25    | TXINN         | TX IF filter output negative                 | 57    | RXIN     | Receiver output I negative                     |

| 26    | VCC2          | Mixer/baseband supply                        | 58    | RXIP     | Receiver output I positive                     |

| 27    | CAPIP         | Capacitor filter I positive                  | 59    | VCC4     | Baseband supply                                |

| 28    | CAPIN         | Capacitor filter I negative                  | 60    | VCCTXVCO | Transmit VCO supply (NC)                       |

| 29    | CAPQP         | Capacitor filter Q positive                  | 61    | NC       | No connect                                     |

| 30    | CAPQN         | Capacitor filter Q negative                  | 62    | NC       | No connect                                     |

| 31    | LPFADJ        | LPF corner resistor                          | 63    | NC       | No connect                                     |

| 32    | T_H           | Track and hold initiate                      | 64    | TX900    | EGSM transmit VCO                              |

The receiver architecture intrinsically defeats DC offsets generated through LO and blocker self-mixing.

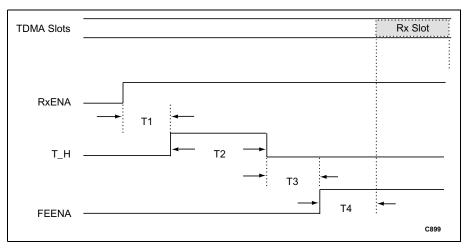

Random input referred offsets generated in the CX74017 must be calibrated out. Three calibration loops are required to ensure that DC offsets do not overload the baseband chain at any point. After compensation, the correction voltages are held in capacitors for the duration of the receive slot(s). Internal, onchip timing is provided to generate the track and hold signals for these calibration loops. The timing for these signals is relative to the T\_H signal.

The timing diagram for the calibration sequence for one DC offset correction in reference to the receive slot is shown in

Figure 3. First the CX74017 receiver is turned on (RXENA is set high). After time T1, the track and hold signal, T\_H, places the DC compensation circuitry in the track mode for time T2. Then, there is a settling time, T3, before the front end is turned on (FEENA is set high). The front end must be turned on for time T4 before the receive slot begins.

For more flexibility with baseband interfaces, the four-pole filter, its associated Variable Gain Amplifier (VGA), and DC offset correction can be bypassed and turned off for current savings.

To minimize the post-PA filtering requirements, and any additional post-PA losses, the transmit path consists of a vector modulator within a frequency translation loop. The translation

loop consists of a Phase Frequency Detector (PFD) and charge pump, a mixer (with an operating range of 800 MHz to 2 GHz), an in-loop modulator, and two transmit VCOs. As shown in Figure 2, the loop functions as a Phase-Locked Loop (PLL) with a mixer and modulator in the feedback path. The on-chip Low-Pass Filter (LPF) following the mixer attenuates the unwanted sideband as well as harmonics. The two on-chip transmit VCOs are designed to meet EGSM, DCS, and PCS requirements.

### Synthesizer Section\_

The CX74017 includes a fully integrated UHF VCO with an onchip LC tank.

A single fractional-N synthesizer can phase lock the local oscillator used in both the transmit and the receive path to a precision frequency reference source. Fractional-N operation offers low phase noise and fast settling times, allowing for multiple slot applications such as GPRS. The frequency stepping function of the CX74017, with a 1 Hz accuracy, allows triple band operation in both transmit and receive bands without the requirement of a large VCO tuning range using only a single integrated on-chip UHF VCO.

#### Control Interface \_\_\_\_

The transceiver and synthesizer are controlled by a three-wire interface. The receiver gain control, as well as the division ratios and charge pump currents in the synthesizer and transmitter,

can be programmed using 24-bit words. The transmitter, receiver, and synthesizer can be enabled separately.

### Electrical and Mechanical Specifications \_

The absolute maximum ratings of the CX74017 are provided in Table 2. The recommended operating conditions are specified in Table 3. Table 4 provides the power consumption of the CX74017 in various operational modes. Electrical specifications are provided in Tables 5, 6, 7 and 8. Table 9 contains the band selection truth table. Table 10 and Table 11 show the function settings of the control bits in the serial interface. Figure 4 depicts a summarized description of each programming word for quick reference. The three-wire serial interface timing diagram is shown in Figure 5. Figure 6 shows the 64-pin CX74017 LGA package dimensions.

## **Electrostatic Discharge**

The CX74017 contains Class 1 devices. The following Electrostatic Discharge (ESD) precautions are recommended:

- Protective outer garments

- Handle device in ESD safeguarded work area

- Transport device in ESD shielded containers

- Monitor and test all ESD protection equipment

- Treat the CX74017 as extremely sensitive to ESD

Figure 3. CX74017 Sample and Hold Timing Diagram

| Parameter                                                                                                                                                                                                                                                                  | Minimum | Maximum | Units |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|--|--|--|

| Supply voltage (VCC)                                                                                                                                                                                                                                                       |         | 3.6     | V     |  |  |  |

| Ambient operating temperature range                                                                                                                                                                                                                                        | -40     | +85     | °C    |  |  |  |

| Storage temperature range                                                                                                                                                                                                                                                  | -50     | +125    | °C    |  |  |  |

| Input voltage range                                                                                                                                                                                                                                                        | GND     | VCC     | V     |  |  |  |

| Maximum power dissipation                                                                                                                                                                                                                                                  |         | 600     | mW    |  |  |  |

| NOTE: stresses above these absolute maximum ratings may cause permanent damage.<br>These are stress ratings only and functional operation at these conditions is not implied.<br>Exposure to maximum rating conditions for extended periods may reduce device reliability. |         |         |       |  |  |  |

Table 2. CX74017 Absolute Maximum Ratings

#### Table 3. CX74017 Recommended Operating Conditions

| Parameter                      | Minimum | Typical | Maximum | Units |

|--------------------------------|---------|---------|---------|-------|

| Power supply                   | 2.7     | 3.0     | 3.6     | V     |

| Operating junction temperature | -40     |         | +100    | °C    |

| Operating ambient temperature  | -40     |         | +85     | °C    |

Table 4. Power Consumption Specifications (TA=25° C, VCC = 2.7 V unless otherwise noted)

| Parameter                                                          | Symbol | Test Condition                            | Minimum | Typical        | Maximum | Units          |

|--------------------------------------------------------------------|--------|-------------------------------------------|---------|----------------|---------|----------------|

| Total supply current:                                              | lcc    |                                           |         |                |         |                |

| Rx mode, GSM<br>Tx mode (no TIC VCO), GSM<br>Synthesizer mode, GSM |        | RXENA=SXENA=H<br>TXENA=SXENA=H<br>SXENA=H |         | 45<br>45<br>15 |         | mA<br>mA<br>mA |

| TIC VCO, GSM                                                       |        |                                           |         | 40             |         | mA             |

| Rx mode, DCS/PCS<br>Tx mode, DCS/PCS<br>Synthesizer mode, DCS/PCS  |        | RXENA=SXENA=H<br>TXENA=SXENA=H<br>SXENA=H |         | 55<br>50<br>20 |         | mA<br>mA<br>mA |

| TIC VCO, DCS/PCS                                                   |        |                                           |         | 40             |         | mA             |

| Sleep mode                                                         |        | @ VCC = 3.6 V<br>RXENA=TXENA=<br>SXENA=L  |         | 20             |         | μΑ             |

#### Table 5. CX74017 Electrical Specifications – Receiver (1 of 4) (T<sub>A</sub>=25° C, VCC = 2.7 V unless otherwise noted)

| Parameter                          | Symbol | Test Condition                                | Minimum | Typical     | Maximum | Units |

|------------------------------------|--------|-----------------------------------------------|---------|-------------|---------|-------|

|                                    |        | LNA: EGSM                                     |         |             |         |       |

| Input impedance                    | Zin    | With external match                           |         | 50          |         | Ω     |

| Input operating frequency          | Band 1 | EGSM Rx band                                  | 925     |             | 960     | MHz   |

| LNA Gain                           | Glna   | High Gain Mode                                |         | 15          |         | dB    |

|                                    |        | Lowest Gain Mode                              |         | -3          |         | dB    |

| Voltage variation versus frequency |        | Over band 1                                   |         | *** TBD *** |         | dB    |

| Noise Figure                       | NFmin  | High gain mode                                |         | 2           |         | dB    |

|                                    | NFмах  | Low gain mode                                 |         | 9           |         | dB    |

|                                    | NFbloc | With –25 dBm input<br>blocker @ 10 MHz offset |         | 3.5         |         | dB    |

| Input 1 dB compression point       | IP1dB  |                                               |         | -20         |         | dBm   |

| Parameter                             | Symbol   | Test Condition                                | Minimum | Typical     | Maximum | Units   |

|---------------------------------------|----------|-----------------------------------------------|---------|-------------|---------|---------|

|                                       | -        | Mixer/LPF: EGS                                | SM      | -           | -       |         |

| Input IP2                             | IIP2     | Referred to LNA input                         | 65      |             |         | dBm     |

| Mixer voltage gain                    | Gміх     | High Gain                                     |         | 40          |         | dB      |

|                                       |          | Low Gain                                      |         | 22          |         | dB      |

| Noise Figure                          | NF       | High Gain                                     |         | 13          |         | dB      |

|                                       |          | Low Gain                                      |         | 23          |         | dB      |

| Input 1 dB compression point          | IP1dB    | In-band (high gain)                           |         | -46         |         | dBV     |

|                                       |          | In-band (low gain)                            |         | -26         |         | dBV     |

|                                       |          | @ 3 MHz                                       |         | -15         |         | dBV     |

| Output 1 dB compression point         | OP1dB    |                                               |         | -6          |         | dBV     |

| Blocker rejection                     |          | @ 3 MHz offset                                |         | -40         |         | dB      |

|                                       |          | @ 1.6 MHz offset                              |         | -30         |         | dB      |

|                                       |          | @ 600 kHz offset                              |         | -16         |         | dB      |

|                                       |          | @ 400 kHz offset                              |         | -8          |         | dB      |

| I/Q amplitude imbalance               |          |                                               |         |             | 1       | dB      |

| I/Q phase imbalance                   |          |                                               | -3      |             | 3       | degrees |

| Combined LNA/mixer NF                 | NFmin    | High gain mode                                |         | 3           |         | dB      |

|                                       | NFмах    | Low gain mode                                 |         | 26          |         | dB      |

|                                       | NFbloc   | With –25 dBm input<br>blocker @ 10 MHz offset |         | 4.5         |         | dB      |

| Combined input 1 dB compression point | IP1dB    | In-band (high gain)                           |         |             | -45     | dBm     |

|                                       |          | In-band (low gain)                            |         |             | -22     | dBm     |

|                                       |          | @ 3 MHz                                       |         |             | -23     | dBm     |

|                                       |          | LNA: DCS                                      |         |             |         |         |

| Input impedance                       | Zin      | With external match                           |         | 50          |         | Ω       |

| Input operating frequency             | Band 2   | DCS/PCS Rx band                               | 1805    |             | 1990    | MHz     |

| LNA gain                              | Glna     | High gain mode                                |         | 15          |         | dB      |

|                                       |          | Lowest gain mode                              |         | -3          |         | dB      |

| Voltage variation versus frequency    |          | Over band 1                                   |         | *** TBD *** |         | dB      |

| Noise Figure                          | NFmin    | High gain mode                                |         | 3           |         | dB      |

| -                                     | NFмах    | Low gain mode                                 |         | 10          |         | dB      |

|                                       | NFbloc   | With –28 dBm input<br>blocker @ 10 MHz offset |         | 4.5         |         | dB      |

| Input 1 dB compression point          | IP1dB    |                                               |         | -22         |         | dBm     |

|                                       | _        | LNA: PCS                                      |         |             |         |         |

| Input impedance                       | Zin      | With external match                           |         | 50          |         | Ω       |

| Input operating frequency             | Band 2   | DCS/PCS Rx band                               | 1805    |             | 1990    | MHz     |

| LNA gain                              | GLNA     | High gain mode                                |         | 15          |         | dB      |

|                                       |          | Lowest gain mode                              |         | -3          |         | dB      |

| Voltage variation versus frequency    |          | Over band 1                                   |         | *** TBD *** |         | dB      |

| Noise Figure                          | NFmin    | High gain mode                                |         | 3           |         | dB      |

| Noise Figure                          |          | Low gain mode                                 |         | 5<br>10     |         | dB      |

|                                       | NFMAX    | With –28 dBm input                            |         | 4.5         |         | dB      |

|                                       | INI BLUC | blocker @ 10 MHz offset                       |         | 4.0         |         | UD      |

#### Table 5. CX74017 Electrical Specifications – Receiver (2 of 4) (Ta=25° C, VCC = 2.7 V unless otherwise noted)

| Table 5. CX74017 Electrical Specifications – Receiver (3 of 4) |

|----------------------------------------------------------------|

| (TA=25° C, VCC = 2.7 V unless otherwise noted)                 |

| Parameter                            | Symbol   | Test Condition                                | Minimum | Typical     | Maximum | Units   |

|--------------------------------------|----------|-----------------------------------------------|---------|-------------|---------|---------|

|                                      | <u>.</u> | LNA: PCS (contin                              | nued)   |             |         |         |

| Noise Figure                         | NFMIN    | High gain mode                                |         | 3           |         | dB      |

| -                                    | NFMAX    | Low gain mode                                 |         | 10          |         | dB      |

|                                      | NFbloc   | With –28 dBm input<br>blocker @ 10 MHz offset |         | 4.5         |         | dB      |

| Input 1 dB compression point         | IP1dB    |                                               |         | -22         |         | dBm     |

|                                      |          | Mixer/LPF: DCS/                               | PCS     |             |         |         |

| Input IP2                            | IIP2     | Referred to LNA input                         | 55      |             |         | dBm     |

| Mixer voltage gain                   | Gmix     | High gain                                     |         | 40          |         | dB      |

|                                      |          | Low gain                                      |         | 22          |         | dB      |

| Noise Figure                         | NF       | High gain                                     |         | 15          |         | dB      |

|                                      |          | Low gain                                      |         | 25          |         | dB      |

| Input 1 dB comp point                | IP1dB    | In-band (high gain)                           |         | -46         |         | dBV     |

|                                      |          | In-band (low gain)                            |         | -26         |         | dBV     |

|                                      |          | @ 3 MHz                                       |         | -15         |         | dBV     |

| Output 1 dB compression point        | OP1dB    |                                               |         | -6          |         | dBV     |

| Blocker rejection                    |          | @ 3 MHz offset                                |         | -40         |         | dB      |

| -                                    |          | @ 1.6 MHz offset                              |         | -30         |         | dB      |

|                                      |          | @ 600 kHz offset                              |         | -16         |         | dB      |

|                                      |          | @ 400 kHz offset                              |         | -8          |         | dB      |

| I/Q Amplitude imbalance              |          |                                               |         |             | 1       | dB      |

| I/Q Phase imbalance                  |          |                                               | -3      |             | 3       | degrees |

| Combined LNA/mixer NF                | NFmin    | Highest gain mode                             |         | 4.2         |         | dB      |

|                                      | NFMAX    | Lowest gain mode                              |         | 28          |         | dB      |

|                                      | NFbloc   | With –28 dBm input<br>blocker @ 10 MHz offset |         | 5.7         |         | dB      |

| Combined input 1dB compression point | IP1dB    | In-band (high gain)                           |         | -45         |         | dBm     |

|                                      |          | In-band (low gain)                            |         | -22         |         | dBm     |

|                                      |          | @ 3 MHz                                       |         | -23         |         | dBm     |

|                                      |          | First Active LF                               | PF      |             |         |         |

| Gain                                 | Av       | High gain                                     |         | 10          |         | dB      |

|                                      |          | Low gain                                      |         | -2          |         | dB      |

| Corner frequency                     | Fc       |                                               |         | 300         |         | kHz     |

| Output 1 dB compression point        | OP1dB    | High gain                                     |         | -6          |         | dBV     |

|                                      |          | Low gain                                      |         | 4           |         | dBV     |

| Rejection                            |          | @ 400 kHz                                     |         | -6          |         | dB      |

|                                      |          | @ 600 kHz                                     |         | -13         |         | dB      |

|                                      |          | @ 1.6 MHz                                     |         | -30         |         | dB      |

|                                      |          | @ 3 MHz                                       |         | -42         |         | dB      |

| Group delay                          |          | Combined with mixer                           |         | 2           |         | μs      |

| Group delay variation                |          | Combined with mixer                           |         | 50          |         | ns      |

| Voltage gain temperature coefficient |          |                                               |         | *** TBD *** |         | dB/°C   |

| Parameter                                                 | Symbol   | Test Condition                          | Minimum   | Typical           | Maximum    | Units          |

|-----------------------------------------------------------|----------|-----------------------------------------|-----------|-------------------|------------|----------------|

|                                                           | <u>-</u> | Second Active I                         | _PF       |                   | -          |                |

| Gain:<br>Highest gain<br>Lowest gain                      | Av       |                                         |           | 40<br>0           |            | dB<br>dB       |

| Gain step                                                 | dAv      |                                         |           | 2                 |            | dB             |

| Gain step accuracy                                        |          |                                         | -0.5      |                   | 0.5        | dB             |

| Input 1 dB compression point                              | IP1dB    |                                         |           | -6                |            | dBV            |

| Corner frequency (programmable)                           | Fc       |                                         | 50        |                   | 150        | kHz            |

| Corner frequency variation                                | dFc      | Without calibration<br>With calibration | -15<br>-7 |                   | +15<br>+7  | %<br>%         |

| Rejection (FC=105 kHz)                                    |          | @200 kHz<br>@400 kHz<br>@600 kHz        |           | -11<br>-34<br>-48 |            | dB<br>dB<br>dB |

| Group delay                                               |          | Fc=105 kHz, (DC to 100 kHz)             |           | 3                 |            | μs             |

| Group delay variation                                     |          | Fc=105 kHz, (DC to 100 kHz)             |           | 300               |            | ns             |

|                                                           |          | Second VGA                              |           |                   |            |                |

| Voltage gain:<br>Highest gain<br>Lowest gain<br>Gain step | Av       |                                         |           | 30<br>0<br>6      |            | dB<br>dB<br>dB |

| Differential output amplitude                             |          | Av = 30 dB<br>Av = 0 dB                 |           |                   | 2.5<br>0.1 | V<br>V         |

| Output common mode voltage                                |          |                                         |           | 1.35              |            | V              |

| Output offset voltage                                     |          | With DC offset correction               |           |                   | ±5         | mV             |

| Output impedance                                          | Ζουτ     |                                         |           | 200               |            | Ω              |

#### Table 5. CX74017 Electrical Specifications – Receiver (4 of 4) (TA=25° C, VCC = 2.7 V unless otherwise noted)

#### Table 6. CX74017 Electrical Specifications – Transmitter (1 of 2) (Ta=25° C, VCC = 2.7 V unless otherwise noted)

| Parameter                         | Symbol | Test Condition   | Minimum | Typical | Maximum   | Units  |

|-----------------------------------|--------|------------------|---------|---------|-----------|--------|

|                                   |        | I/Q Modulate     | or      | -       | -         |        |

| Differential input impedance      | ZIN    |                  |         | 20      |           | kΩ     |

| Input signal level                |        | Differential     |         | 1       |           | Vp-р   |

| Input common mode voltage range   | Vсм    |                  | 0.85    | 1.35    | VCC – 1.3 | V      |

| Input offset voltage              | Vos    |                  |         |         | 5         | mV     |

| Input frequency 3 dB bandwidth    |        |                  |         | 3       |           | MHz    |

| Input common mode rejection ratio |        | FIN = 100 kHz    |         | 75      |           | dB     |

|                                   |        | FIN = 1 MHz      |         | 55      |           |        |

| Output operating frequency        | Fout   |                  | 70      |         | 110       | MHz    |

| Output impedance                  | Ζουτ   | Per side         |         | 400     |           | Ω      |

| Output voltage                    | Vout   |                  | -20     | -15     |           | dBV    |

| Output noise power                | No     | @ 10 MHz offset  |         | -132    | -128      | dBc/Hz |

|                                   |        | @ 1.8 MHz offset |         | -130    | -126      | dBc/Hz |

| LO feedthrough                    |        |                  |         | -45     | -40       | dBc    |

| Sideband suppression              |        |                  | 38      | 45      |           | dB     |

| Table 6. CX74017 Electrical Specifications – Transmitter (2 of 2) |

|-------------------------------------------------------------------|

| (TA=25° C, VCC = 2.7 V unless otherwise noted)                    |

| Parameter                                                   | Symbol | Test Condition                        | Minimum    | Typical      | Maximum | Units     |

|-------------------------------------------------------------|--------|---------------------------------------|------------|--------------|---------|-----------|

|                                                             |        | I/Q Modulator (cor                    | ntinued)   |              |         |           |

| Spurious                                                    |        | Modulation 2 <sup>nd</sup> order      |            | -70          | -40     | dBc       |

|                                                             |        | Modulation 3 <sup>rd</sup> order      |            | -60          | -55     | dBc       |

|                                                             |        | Translational L                       | oop        |              |         |           |

| Transmit frequency (input from VCO)                         | fтx    |                                       | 800        |              | 2000    | MHz       |

| IF frequency                                                | fı⊧    |                                       | 70         |              | 110     | MHz       |

| Transmit input power                                        | Pin    | With external 50 $\Omega$ termination | -13        | -10          | -7      | dBm       |

| Transmit input impedance                                    | Zin    |                                       |            | 300//<br>0.3 |         | Ω//<br>pF |

| Transmitter output phase noise                              | No     | @ 400 kHz offset                      |            |              | -118    | dBc/Hz    |

|                                                             |        | @ 1.8 MHz offset                      |            |              | -124    | dBc/Hz    |

|                                                             |        | Translational Loop (                  | continued) |              |         |           |

| Charge pump output current: high                            | Ιουτ   | CP = state 4                          |            | ±2.0         |         | mA        |

| impedance source/sink                                       |        | CP = state 3                          |            | ±1.5         |         | mA        |

|                                                             |        | CP = state 2                          |            | ±.1.0        |         | mA        |

|                                                             |        | CP = state 1                          |            | ±0.5         |         | mA        |

| Device turn-on and lock time (with respect to enable input) |        |                                       |            | 30           | 100     | μs        |

| N divide ratio range                                        |        |                                       | 9          |              | 12      |           |

| R divide ratio                                              |        |                                       | 1          |              | 2       |           |

|                                                             | ·      | EGSM Translation L                    | oop VCO    |              |         |           |

| Frequency range                                             | Frng   |                                       | 880        |              | 915     | MHz       |

| Power output                                                | Роит   |                                       | 8          | 10           | 12      | dBm       |

| Phase noise                                                 | Nph    | At 10 MHz offset                      |            | -153         | -150    | dBc/Hz    |

|                                                             |        | At 20 MHz offset                      |            | -165         | -162    | dBc/Hz    |

|                                                             | ·      | DCS Translation Lo                    | oop VCO    |              |         |           |

| Frequency range                                             | Frng   |                                       | 1710       |              | 1785    | MHz       |

| Power output                                                | Роит   |                                       | 6          | 8            | 10      | dBm       |

| Phase noise                                                 | Nph    | At 20 MHz offset                      |            | -154         | -152    | dBc/Hz    |

|                                                             |        | PCS Translation Lo                    | oop VCO    |              |         |           |

| Frequency range                                             | Frng   |                                       | 1850       |              | 1910    | MHz       |

| Power output                                                | Роит   |                                       | 6          | 8            | 10      | dBm       |

| Phase noise                                                 | Nph    | At 20 MHz offset                      |            | -154         | -152    | dBc/Hz    |

| Parameter                                           | Symbol | Test Condition | Min | Typical | Мах | Units |

|-----------------------------------------------------|--------|----------------|-----|---------|-----|-------|

| Data to clock setup time (see Figure 5)             | tcs    |                | 50  |         |     | ns    |

| Data to clock hold time (see Figure 5)              | tcн    |                | 10  |         |     | ns    |

| Clock pulse width High (see Figure 5)               | tcwн   |                | 50  |         |     | ns    |

| Clock pulse width Low (see Figure 5)                | tcwL   |                | 50  |         |     | ns    |

| Clock to load enable setup time see<br>(Figure 5)   | tes    |                | 50  |         |     | ns    |

| Load enable pulse width (see Figure 5)              | tew    |                | 50  |         |     | ns    |

| LE falling edge to clock rising edge (see Figure 5) | tefc   |                | 50  |         |     | ns    |

| RXENA setup time                                    |        |                | 50  |         |     | ns    |

| TXENA setup time                                    |        |                | 50  |         |     | ns    |

| SXENA setup time                                    |        |                | 50  |         |     | ns    |

| FEENA setup time                                    |        |                | 50  |         |     | ns    |

| Power supply range                                  | VCC    |                | 2.7 |         | 3.6 | V     |

| Operating temperature range                         | Та     |                | -40 | 25      | 85  | °C    |

| Table 7. CX74017 Electrical Specifications – Three-Wire Interface |

|-------------------------------------------------------------------|

| (TA=25° C, VCC = 2.7 V unless otherwise noted)                    |

| Table 8. CX74017 Electrical Specifications – Synthesizer (1 of 2) |

|-------------------------------------------------------------------|

| (TA=25° C, VCCB = 2.7 V unless otherwise noted)                   |

| Parameter                                                    | Symbol | Test Condition                                                           | Minimum | Typical                  | Maximum   | Units                |

|--------------------------------------------------------------|--------|--------------------------------------------------------------------------|---------|--------------------------|-----------|----------------------|

| Operating input frequency                                    |        | RF                                                                       | 100     |                          | 100       | MHz                  |

| Reference input frequency                                    |        |                                                                          | 10      | 13                       | 20        | MHz                  |

| Phase detector frequency                                     |        | RF                                                                       |         | 13                       |           | MHz                  |

| Input sensitivity                                            |        | RF                                                                       | -15     |                          |           | dBm                  |

| Reference oscillator sensitivity                             |        |                                                                          | 0.5     |                          | VDD       | Vpeak                |

| In-band phase noise                                          |        | RF                                                                       |         | -90                      |           | dBc/Hz               |

| Spurious tones                                               |        | RF                                                                       |         | -75                      |           | dBc                  |

| Charge pump output current (can be programmed in four steps) |        | RF, VCP = VDD/2<br>RF, VCP = VDD/2<br>RF, VCP = VDD/2<br>RF, VCP = VDD/2 |         | 100<br>200<br>300<br>400 |           | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Charge pump leakage current                                  |        | 0.5 < VCP < VDD - 0.5                                                    |         | 0.1                      |           | nA                   |

| Charge pump sink versus source mismatch                      |        | VCP = VDD/2                                                              |         | 5                        |           | %                    |

| Charge pump current versus<br>voltage/temperature            |        | 0.5 < VCP < VDD - 0.5                                                    |         | 10                       |           | %                    |

|                                                              |        | GSM LO                                                                   | ·       |                          | ·         |                      |

| Operating frequency                                          | Fvco   |                                                                          | 880     |                          | 960       |                      |

| Tuning voltage range                                         |        |                                                                          | 0.3     |                          | VCC – 0.5 |                      |

| Tuning sensitivity                                           | Кисо   |                                                                          |         | 20                       |           |                      |

| Phase noise                                                  |        | @ 10 MHz offset<br>@ 3 MHz offset<br>@ 400 kHz offset                    |         | -144<br>-142<br>-125     |           |                      |

| Table 8. CX74017 Electrical Specifications – Synthesizer (2 of 2) |  |

|-------------------------------------------------------------------|--|

| (TA=25° C, VCCB = 2.7 V unless otherwise noted)                   |  |

| Parameter            | Symbol | Test Condition                                        | Minimum | Typical              | Maximum   | Units |

|----------------------|--------|-------------------------------------------------------|---------|----------------------|-----------|-------|

|                      |        | DCS/PCS LO                                            | )       |                      |           |       |

| Operating frequency  | Fvco   |                                                       | 1710    |                      | 1990      |       |

| Tuning voltage range |        |                                                       | 0.3     |                      | VCC - 0.5 |       |

| Tuning sensitivity   | Кисо   |                                                       |         | 20                   |           |       |

| Phase noise          |        | @ 10 MHz offset<br>@ 3 MHz offset<br>@ 400 kHz offset |         | -138<br>-136<br>-119 |           |       |

Table 9. CX74017 Operation Band Selection Logic

| BANDSEL1 | BANDSEL2 | Band of Operation |

|----------|----------|-------------------|

| 0        | 0        | GSM900            |

| 0        | 1        | GSM900            |

| 1        | 0        | DCS1800           |

| 1        | 1        | PCS1900           |

| Table 10  | <b>Control And Output States</b> | (1 of 2) |

|-----------|----------------------------------|----------|

| Tuble IV. | oona on na output otates         | (1012)   |

| Symbol | Function                       | Description                                          |

|--------|--------------------------------|------------------------------------------------------|

| EN     | Program mode enable bits [1:0] | Logic 11 enables program mode                        |

| LNA    | Gain [2]                       | Logic 1 selects the high gain mode of the LNA        |

| MIX    | [3]                            | Logic 1 selects the high gain mode of the RX mixer   |

| LPF1   | [4]                            | Logic 1 selects the high gain mode of the active LPF |

| VGA2   | V2 gain steps [7:5]            | s5 to s7 program the V2 gain in 6 dB increments:     |

|        |                                | Logic 000 sets gain to 30 dB                         |

|        |                                | Logic 001 sets gain to 24 dB                         |

|        |                                | Logic 010 sets gain to 18 dB                         |

|        |                                | Logic 011 sets gain to 12 dB                         |

|        |                                | Logic 100 sets gain to 6 dB                          |

|        |                                | Logic 101 sets gain to 0 dB                          |

| AUX    | [8]                            | Logic 1 activates 6 dB auxiliary gain                |

| VGA1   | V1 gain steps [11:9]           | S9 to s11 program the V1 gain in 6 dB increments:    |

|        |                                | Logic 000 sets gain to 30 dB                         |

|        |                                | Logic 001 sets gain to 24 dB                         |

|        |                                | Logic 010 sets gain to 18 dB                         |

|        |                                | Logic 011 sets gain to 12 dB                         |

|        |                                | Logic 100 sets gain to 6 dB                          |

|        |                                | Logic 101 sets gain to 0 dB                          |

| VGA1   | V1 fine tune[13:12]            | S12 and s13 program V1 in 2 dB increments:           |

|        |                                | Logic 00 sets gain to 0 dB                           |

|        |                                | Logic 01 sets gain to 2 dB                           |

|        |                                | Logic 10 sets gain to 4 dB                           |

| Symbol | Function                   | Description                                   |

|--------|----------------------------|-----------------------------------------------|

| TXCP   | Tx charge pump bits[15:14] | Two bit translation loop charge pump setting: |

|        |                            | Logic 00 sets TXCP to 0.5 mA                  |

|        |                            | Logic 01 sets TXCP to 1.0 mA                  |

|        |                            | Logic 10 sets TXCP to 1.5 mA                  |

|        |                            | Logic 11 sets TXCP to 2.0 mA                  |

| TXN    | N divider [17:16]          | These two bits set N divider ratio:           |

|        |                            | Logic 00 sets N to 9                          |

|        |                            | Logic 01 sets N to 10                         |

|        |                            | Logic 10 sets N to 11                         |

|        |                            | Logic 11 sets N to 12                         |

| TXR    | R divider [18]             | Set the R divider ratio selection:            |

|        |                            | Logic 0 sets R to 1                           |

|        |                            | Logic 1 sets R to 2.                          |

| TXPOL  | CP polarity [19]           | One bit CP polarity selection:                |

|        |                            | Logic 0 sets POL to Normal                    |

|        |                            | Logic 1 sets POL to Inverted                  |

| RSVD   | Reserved [20]              | Reserved bit                                  |

| RSVD   | Reserved [21]              | Reserved bit                                  |

| RSVD   | Reserved [22]              | Reserved bit                                  |

| RSVD   | Reserved [23]              | Reserved bit                                  |

Table 10. Control And Output States (2 of 2)

#### Table 11. Serial Interface Description for Fractional-N Sx

| Symbol | Function                           | Description                                                                                            |

|--------|------------------------------------|--------------------------------------------------------------------------------------------------------|

| D0     | Address bit [0]                    | Logic 0 enables three-wire programming for synthesizer                                                 |

| D1     | Address bit [1]                    | Logic 0 enables PLL programming and logic 1 enables fractional-modulo programming                      |

| EN     | Enable mode [2]                    | Logic 0 enables synthesizer                                                                            |

| EF     | Integer mode [3]                   | Logic 0 sets the integer-N mode and logic 1 sets the fractional-N mode                                 |

| SP     | Phase detector output polarity [4] | Logic 0 sets the phase detector output for negative VCO gain and logic 1 sets it for positive VCO gain |

| SC     | Charge-pump output current [6:5]   | Charge pump current selection: (logic 00 sets 100 μA, 01 = 200 μA, 10 = 300 μA, 11 = 400 μA)           |

| LD     | Test mode [8:7]                    | Logic 00 multiplexes N divider output to LD output                                                     |

|        |                                    | Logic 01 multiplexes R divider output to LD output                                                     |

|        |                                    | Logic 10 multiplexes lock detect output to LD output                                                   |

| Ν      | Main divider [19:9]                | Sets 11-bit main divider ratio with minimum division ratio of 64                                       |

| R      | Reference divider [23:20]          | Sets 4-bit reference divider ratio with minimum division ratio of 1                                    |

| FN     | Fractional-N modulo [23:2]         | Sets fractional-N modulo up to 2 <sup>22</sup> (= 4,194,300) modulo                                    |

| D23                                   | D22 | D21 | D20 | D19                        | D18                               | D17            | D16 | D15           | D14 | D13            | D12 | D11  | D10              | D9   | D8                    | D7  | D6       | D5     | D4                               | D3   | D2                    | D1 | D0 |

|---------------------------------------|-----|-----|-----|----------------------------|-----------------------------------|----------------|-----|---------------|-----|----------------|-----|------|------------------|------|-----------------------|-----|----------|--------|----------------------------------|------|-----------------------|----|----|

| RSVD                                  | 1   | RS  |     | TXCP<br>Polarity<br>Select | TXR<br>Divider<br>Ratio<br>Select | TXN E<br>Radio |     | TXCP (<br>Sel |     | VGA1<br>Gain S |     | VGA1 | Coarse<br>Select | Gain | Aux<br>Gain<br>Select | VGA | 2 Gain S | Select | Active<br>LPF1<br>Gain<br>Select | Gain | LNA<br>Gain<br>Select | 1  | 1  |

|                                       |     |     |     | ī                          | 1                                 |                |     |               |     |                |     |      |                  |      |                       |     |          |        |                                  |      |                       |    |    |

| D23                                   | D22 | D21 | D20 | D19                        | D18                               | D17            | D16 | D15           | D14 | D13            | D12 | D11  | D10              | D9   | D8                    | D7  | D6       | D5     | D4                               | D3   | D2                    | D1 | D0 |

| R DIVIDER N DIVIDER LD SC SP EF EN    |     |     |     |                            |                                   |                |     |               | 0   | 0              |     |      |                  |      |                       |     |          |        |                                  |      |                       |    |    |

| Reserved for Fractional-N Programming |     |     |     |                            |                                   |                |     | 1             | 0   |                |     |      |                  |      |                       |     |          |        |                                  |      |                       |    |    |

Figure 4. Programming Word Summary

Figure 5. Serial Data Input Timing Diagram For Transceiver

Figure 6. CX74017 64-Pin LGA Package Dimension Drawing

## **Ordering Information**

| Model Name | Manufacturing Part Number | Product Revision |  |  |  |  |

|------------|---------------------------|------------------|--|--|--|--|

| CX74017    |                           |                  |  |  |  |  |

© 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>™</sup>, the Conexant C symbol, and "What's Next in Communications Technologies"<sup>™</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

Additional information, posted at www.conexant.com, is incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

Further Information literature@conexant.com (800) 854-8099 (North America) (949) 483-6996 (International) Printed in USA

#### World Headquarters

Conexant Systems, Inc. 4311 Jamboree Road Newport Beach, CA 92660-3007 Phone: (949) 483-4600 Fax 1: (949) 483-4078 Fax 2: (949) 483-4391

#### **Americas**

U.S. Northwest/ Pacific Northwest – Santa Clara Phone: (408) 249-9696 Fax: (408) 249-7113

U.S. Southwest – Los Angeles Phone: (805) 376-0559 Fax: (805) 376-8180

**U.S. Southwest – Orange County** Phone: (949) 483-9119 Fax: (949) 483-9090

**U.S. Southwest – San Diego** Phone: (858) 713-3374 Fax: (858) 713-4001

U.S. North Central – Illinois Phone: (630) 773-3454 Fax: (630) 773-3907

**СО N E X A N T**<sup>™</sup>

t's next in communications technologies"

U.S. South Central – Texas Phone: (972) 733-0723 Fax: (972) 407-0639

U.S. Northeast – Massachusetts Phone: (978) 367-3200 Fax: (978) 256-6868

**U.S. Southeast – North Carolina** Phone: (919) 858-9110 Fax: (919) 858-8669

U.S. Southeast – Florida/ South America Phone: (727) 799-8406 Fax: (727) 799-8306

U.S. Mid-Atlantic – Pennsylvania Phone: (215) 244-6784 Fax: (215) 244-9292

**Canada – Ontario** Phone: (613) 271-2358 Fax: (613) 271-2359

#### Europe

Europe Central – Germany Phone: +49 89 829-1320 Fax: +49 89 834-2734 Europe North – England Phone: +44 (0)118 920 9500 Fax: +44 (0)118 920 9595

**Europe – Israel/Greece** Phone: +972 9 9524000 Fax: +972 9 9573732

Europe South – France Phone: +33 1 41 44 36 51 Fax: +33 1 41 44 36 90

**Europe Mediterranean – Italy** Phone: +39 02 93179911 Fax: +39 02 93179913

Europe – Sweden Phone: +46 (0) 8 5091 4319 Fax: +46 (0) 8 590 041 10

Europe – Finland Phone: +358 (0) 9 85 666 435 Fax: +358 (0) 9 85 666 220

#### Asia – Pacific

**Taiwan** Phone: (886-2) 2-720-0282 Fax: (886-2) 2-757-6760

Australia Phone: (61-2) 9869 4088 Fax: (61-2) 9869 4077

**China – Central** Phone: 86-21-6361-2515 Fax: 86-21-6361-2516

**China – South** Phone: (852) 2 827-0181 Fax: (852) 2 827-6488

**China – South (Satellite)** Phone: (86) 755-518-2495

**China – North** Phone: (86-10) 8529-9777 Fax: (86-10) 8529-9778

India Phone: (91-11) 692-4789 Fax: (91-11) 692-4712

Korea Phone: (82-2) 565-2880 Fax: (82-2) 565-1440

Korea (Satellite) Phone: (82-53) 745-2880 Fax: (82-53) 745-1440

Singapore Phone: (65) 737 7355 Fax: (65) 737 9077

Japan Phone: (81-3) 5371 1520 Fax: (81-3) 5371 1501

www.conexant.com