# Contents

| Page | Section | Title                                                                          |

|------|---------|--------------------------------------------------------------------------------|

| 3    | 1.      | Introduction                                                                   |

| 3    | 1.1.    | Main Features                                                                  |

| 5    | 2.      | Functional Description                                                         |

| 5    | 2.1.    | I <sup>2</sup> S Interface                                                     |

| 6    | 2.2.    | Interpolation Filter                                                           |

| 6    | 2.3.    | Variable Sample and Hold                                                       |

| 6    | 2.4.    | 3rd-order Noise Shaper and Multibit DAC                                        |

| 6    | 2.5.    | Analog Low-pass                                                                |

| 6    | 2.6.    | Input Select and Mixing Matrix                                                 |

| 6    | 2.7.    | Postfilter Op Amps, Deemphasis Op Amps, and Line-Out                           |

| 7    | 2.8.    | Analog Volume                                                                  |

| 7    | 2.9.    | Headphone Amplifier                                                            |

| 8    | 2.10.   | Clock System                                                                   |

| 8    | 2.10.1. | Standard Mode                                                                  |

| 8    | 2.10.2. | MPEG Mode                                                                      |

| 9    | 2.11.   | I <sup>2</sup> C Bus Interface                                                 |

| 9    | 2.12.   | Registers                                                                      |

| 9    | 2.13.   | Chip Select                                                                    |

| 9    | 2.14.   | Reduced Feature Mode                                                           |

| 10   | 3.      | Specifications                                                                 |

| 10   | 3.1.    | Outline Dimensions                                                             |

| 10   | 3.2.    | Pin Connections and Short Descriptions                                         |

| 12   | 3.3.    | Pin Descriptions                                                               |

| 12   | 3.3.1.  | Power Supply Pins                                                              |

| 12   | 3.3.2.  | Analog Audio Pins                                                              |

| 12   | 3.3.3.  | Oscillator and Clock Pins                                                      |

| 13   | 3.3.4.  | Other Pins                                                                     |

| 13   | 3.4.    | Pin Configuration                                                              |

| 14   | 3.5.    | Pin Circuits                                                                   |

| 15   | 3.6.    | Control Registers                                                              |

| 17   | 3.7.    | Electrical Characteristics                                                     |

| 17   | 3.7.1.  | Absolute Maximum Ratings                                                       |

| 18   | 3.7.2.  | Recommended Operating Conditions                                               |

| 20   | 3.7.3.  | Characteristics                                                                |

| 25   | 4.      | Applications                                                                   |

| 25   | 4.1.    | Line Output Details                                                            |

| 25   | 4.2.    | Recommended Low-Pass Filters for Analog Outputs                                |

| 26   | 4.3.    | Recommendations for Filters and Deemphasis                                     |

| 26   | 4.4.    | Recommendations for MegaBass Filter without Deemphasis plus 1st-order low-pass |

| 27   | 4.5.    | Power-up/down Sequence                                                         |

| 27   | 4.5.1.  | Power-up Sequence                                                              |

| 27   | 4.5.2.  | Power-down Sequence                                                            |

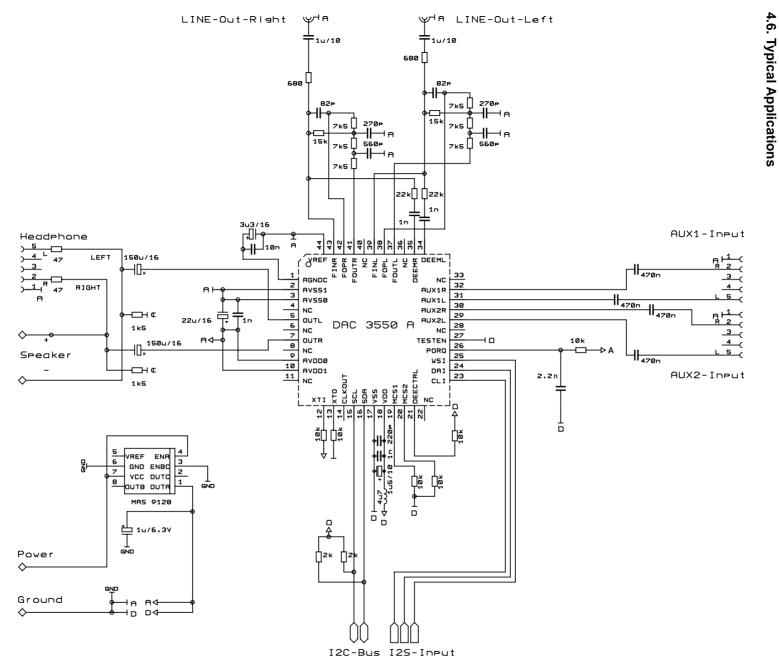

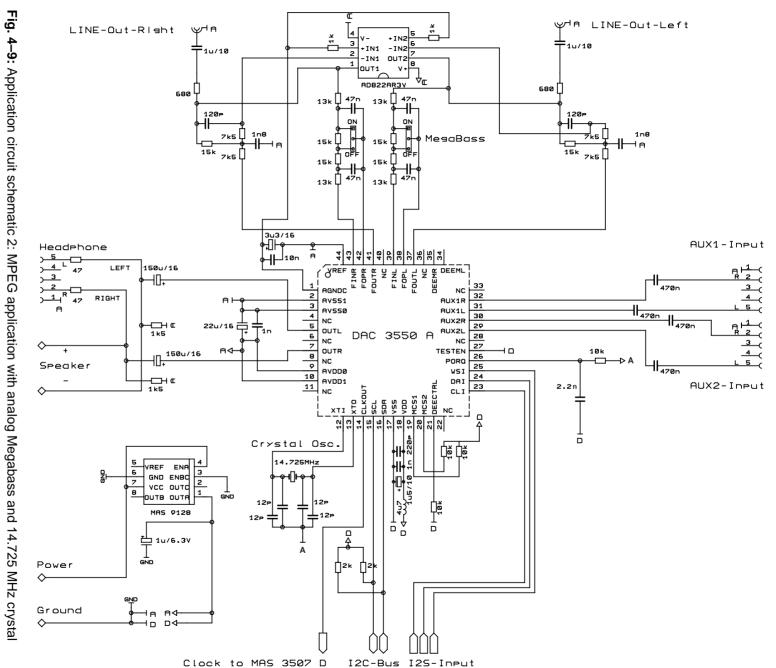

| 28   | 4.6.    | Typical Applications                                                           |

| 32   | 5.      | Data Sheet History                                                             |

|      |         |                                                                                |

#### Stereo Audio DAC

#### 1. Introduction

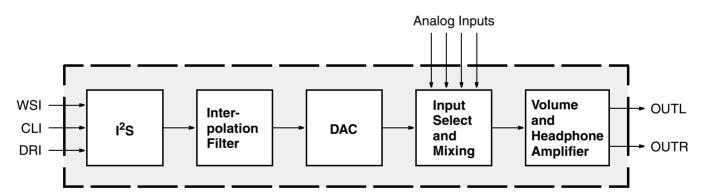

The DAC 3550A is a single-chip, high-precision, dual digital-to-analog converter designed for audio applications. The employed conversion technique is based on oversampling with noise-shaping.

With Micronas' unique multibit sigma-delta technique, less sensitivity to clock jitter, high linearity, and a superior S/N ratio has been achieved. The DAC 3550A is controlled via I<sup>2</sup>C bus.

Digital audio input data is received by a versatile I<sup>2</sup>S interface. The analog back-end consists of internal analog filters and op amps for cost-effective additional external sound processing. The DAC 3550A provides line-out, headphone/speaker amplifiers, and volume control. Moreover, mixing additional analog audio sources to the D/A-converted signal is supported.

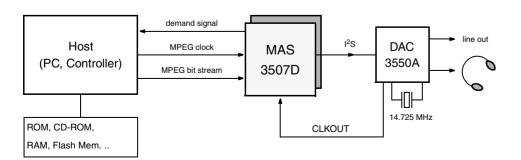

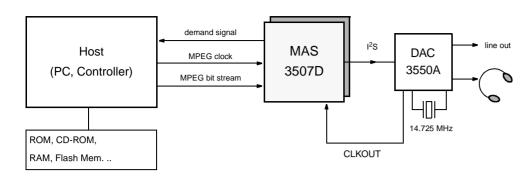

The DAC 3550A is designed for all kinds of applications in the audio and multimedia field, such as: MPEG players, CD players, DVD players, CD-ROM players, etc. The DAC 3550A ideally complements the MPEG 1/2 layer 2/3 audio decoder MAS 3507D.

No crystal required for standard applications with sample rates from 32 to 48 kHz. Crystal required only for automatic sample rate detection below 32 kHz, MPEG mode (refer to Section 2.10), and use of clock output CLKOUT.

#### 1.1. Main Features

- no master main input clock required

- integrated stereo headphone amplifier and mono speaker amplifier

- SNR of 103 dBA

- I<sup>2</sup>C bus, I<sup>2</sup>S bus

- internal clock oscillator

- full-feature mode by I<sup>2</sup>C control (three selectable subaddresses)

- reduced feature mode for non-I<sup>2</sup>C applications

- continuous sample rates from 8 kHz to 50 kHz

- analog deemphasis for 44.1 kHz

- analog volume and balance: +18...-75 dB and mute

- oversampling and multibit noise-shaping technique

- THD better than 0.01 %

- two additional analog stereo inputs (AUX) with source selection and mixing

- supply range: 2.7 V...5.5 V

- low-power mode

- additional line-out

- on-chip op amps for cost-effective external analog sound processing

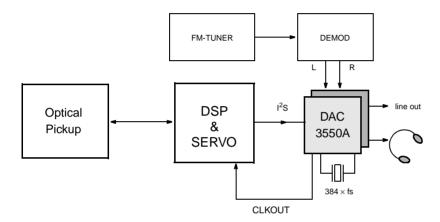

Fig. 1-1: Block diagram of the DAC 3550A

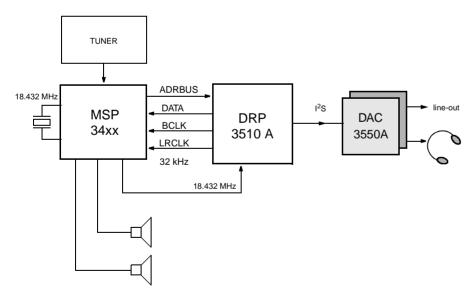

Fig. 1-2: Typical application: MPEG Layer 3 Player

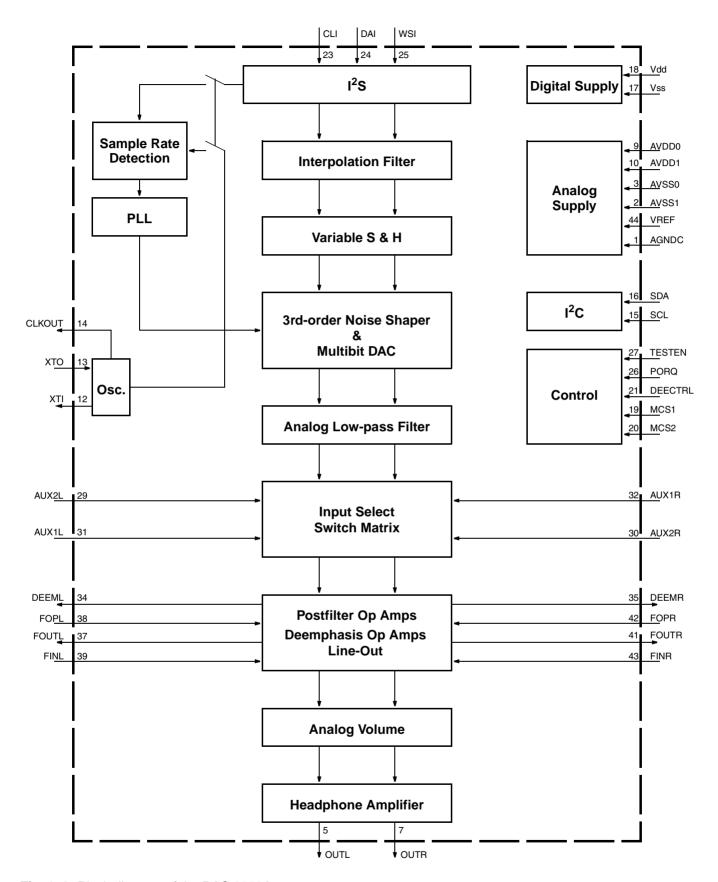

Fig. 1-3: Block diagram of the DAC 3550A

#### 2. Functional Description

#### 2.1. I<sup>2</sup>S Interface

The I<sup>2</sup>S interface is the digital audio interface between the DAC 3550A and external digital audio sources such as CD/DAT players, MPEG decoders etc. It covers most of the I<sup>2</sup>S-compatible formats.

All modes have two common features:

- 1. The MSB is left justified to an I<sup>2</sup>S frame identification (WSI) transition.

- 2. Data is valid on the rising edge of the bit clock CLI.

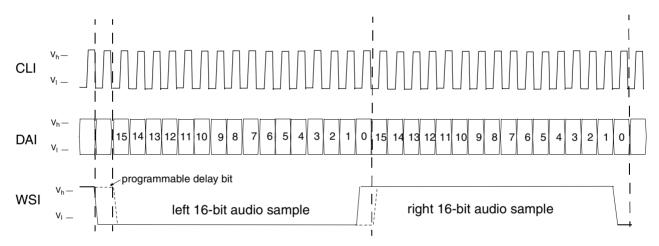

#### 16-bit mode

In this case, the bit clock is  $32 \times \text{fs}_{\text{audio}}$ . Maximum word length is 16 bit.

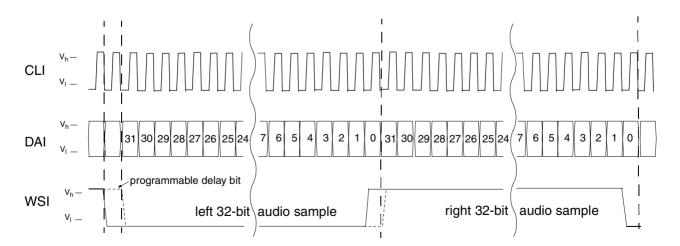

#### 32-bit mode

In this case, the bit clock is  $64 \times \mathrm{fs}_{\mathrm{audio}}$ . Maximum word length is 32 bit.

#### **Automatic Detection**

No I<sup>2</sup>C control is required to switch between 16- and 32-bit mode. It is recommended to switch the DAC 3550A into mute position during changing between 16- and 32-bit mode.

For high-quality audio, it is recommended to use the 32-bit mode of the I<sup>2</sup>S interface to make use of the full dynamic range (if more than 16 bits are available).

#### **Left-Right Selection**

Standard I<sup>2</sup>S format defines an audio frame always starting with left channel and low-state of WSI. However, I<sup>2</sup>C control allows changing the polarity of WSI.

#### **Delay Bit**

Standard I<sup>2</sup>S format requires a delay of one clock cycle between transitions of WSI and data MSB. In order to fit other formats, however, this characteristic can be switched off and on by I<sup>2</sup>C control.

Fig. 2-1: I<sup>2</sup>S 16-bit mode (LR\_SEL=0)

**Fig. 2–2:** I<sup>2</sup>S 32-bit mode (LR\_SEL=0)

**Note:** Volume mute should be applied before changing I<sup>2</sup>S mode in order to avoid audible clicks.

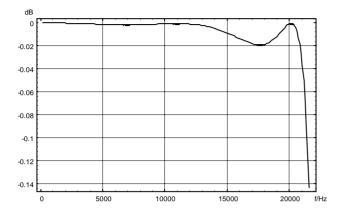

#### 2.2. Interpolation Filter

The interpolation filter increases the sampling rate by a factor of 8. The characteristic for  $fs_{audio} = 48 \text{ kHz}$  is shown in Fig. 2–3.

**Fig. 2–3:** 1→8 Interpolation filter; frequency range: 0...22 kHz

#### 2.3. Variable Sample and Hold

The advantage of this system is that even at low sample frequencies the out-of-band noise is not scaled down to audible frequencies.

### 2.4. 3rd-order Noise Shaper and Multibit DAC

The 3rd-order noise shaper converts the oversampled audio signal into a 5-bit noise-shaping signal at a high sampling rate. This technique results in extremely low quantization noise in the audio band.

#### 2.5. Analog Low-pass

The analog low-pass is a first order filter with a cut-off frequency of approximately 1.4 MHz which removes the high-frequency components of the noise-shaping signal.

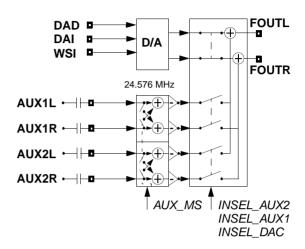

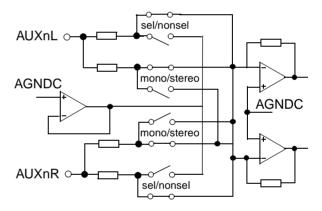

#### 2.6. Input Select and Mixing Matrix

This block is used to switch between or mix the auxiliary inputs and the signals coming from the DAC. A switch matrix allows to select between mono and stereo mode as shown in Fig. 2–4.

Fig. 2-4: Switch matrix

Mono mode is realized by adding left and right channel.

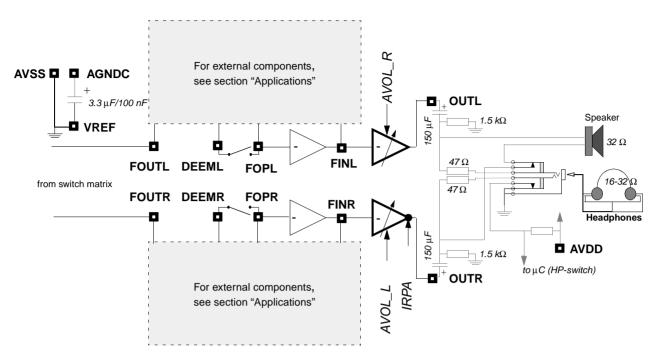

# 2.7. Postfilter Op Amps, Deemphasis Op Amps, and Line-Out

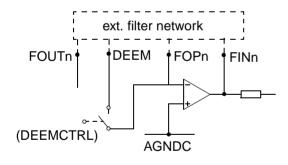

This block contains the active components for the analog postfilters and the deemphasis network. The op amps and all I/O-pins for this block are shown in Fig. 2–5.

Fig. 2-5: Postfilter op amps, deemphasis op amps, and line-out

#### 2.8. Analog Volume

The analog volume control covers a range from  $+18~\mathrm{dB}$  to  $-75~\mathrm{dB}$ . The lowest step is the mute position.

Step size is split into a 3-dB and a 1.5-dB range:

-75 dB...-54 dB: 3 dB step size -54 dB...+18 dB: 1.5 dB step size

# 2.9. Headphone Amplifier

The headphone amplifier output is provided at the OUTL and OUTR pins connected either to stereo headphones or a mono loudspeaker. The stereo headphones require external 47- $\Omega$  serial resistors in both channels. If a loudspeaker is connected to these outputs, the power amplifier for the right channel must be switched to inverse polarity. In order to optimize the available power, the source of the two output amplifiers should be identical, i.e. a monaural signal.

Please note, that if a speaker is connected, it should strictly be connected as shown in Fig. 2–5. Never use a separate connector for the speaker, because electrostatic discharge could damage the output transistors.

Table 2–1: Volume Control

| Volume/dB  | AVOL             |

|------------|------------------|

| 18.0       | 111000           |

| 16.5       | 110111           |

| 15.0       | 110110           |

| 13.5       | 110101           |

| -          | -                |

| 0.0        | 101100 (default) |

| -1.5       | 101011           |

| _          | _                |

| -54.0      | 001000           |

| -57.0      | 000111           |

| -          | -                |

| <b>-75</b> | 000001           |

| Mute       | 000000           |

#### 2.10. Clock System

The advantage of the DAC 3550A clock system is that no external master clock is needed. Most DACs need  $256 \times fs_{audio}$ ,  $384 \times fs_{audio}$ , or at least an asynchronous clock.

All internal clocks are generated by a PLL circuit, which locks to the  $I^2S$  bit clock (CLI). If no  $I^2S$  clock is present, the PLL runs free, and it is guaranteed that there is always a clock to keep the IC controllable by  $I^2C$ .

The device can be set to two different modes:

- Standard mode

- MPEG mode

In the standard mode, I<sup>2</sup>C subaddressing is possible (ADR0, ADR1, ADR2).

MPEG mode always uses ADR3.

To select the modes, the MCS1/MCS2 pins must be set according to Table 2–2.

Table 2-2: Operation Modes

| MCS1 | MCS2 | Mode          | Sub-<br>address | Default<br>Sample<br>Rate |

|------|------|---------------|-----------------|---------------------------|

| 0    | 0    | Stan-<br>dard | ADR0            | 32–48 kHz                 |

| 0    | 1    | Stan-<br>dard | ADR1            | 32–48 kHz                 |

| 1    | 0    | Stan-<br>dard | ADR2            | 32–48 kHz                 |

| 1    | 1    | MPEG          | ADR3            | Automatic                 |

#### 2.10.1. Standard Mode

without I<sup>2</sup>C

In standard mode, sample rates from 48 kHz to 32 kHz are handled without  $I^2C$  control automatically. The setting for this range is the default setting.

with I<sup>2</sup>C

Sample rates below 32 kHz require an I<sup>2</sup>C control to set the PLL divider. This ensures that even at low sample rates, the DAC 3550A runs at a high clock rate. This avoids audible effects due to the noise-shaping technique of the DAC 3550A. Sample rate range is continuous from 8 to 50 kHz. The I<sup>2</sup>C setting of low sample rates must follow according to Section 3.6. "Control Registers" on page 15.

An additional mode allows automatic sample rate detection. In this case, the clock oscillator is required and must run at frequencies between 13.3 MHz to 17 MHz. This mode, however, does not support continuous sample rates. Only the following sample rates are allowed:

8 kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48 kHz

The sample rate detection allows a tolerance of  $\pm 200$  ppm at WSI.

If the oscillator is not used for automatic sample rate detection, it can be used as a general-purpose clock for the application. The frequency range in this case is 10 MHz to 25 MHz.

#### 2.10.2. MPEG Mode

This mode should be used in conjunction with MAS 3507D in MPEG player applications. In this case a 14.725 MHz signal is needed to provide a clock for the MAS 3507D and to allow an automatic sample rate detection in the DAC 3550A. All MPEG sample rates from 8 to 48 kHz can be detected. The internal processing and the DAC itself are automatically adjusted to keep constant performance throughout the entire range. I<sup>2</sup>C control for sample rate adjustment is not needed in this case. Register SR\_REG[0:2] is locked to SRC\_A; see Section 3.6. "Control Registers" on page 15.

The MPEG sample rates:

8 kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48 kHz

As in standard mode, the sample rate detection allows a tolerance of  $\pm 200$  ppm at WSI.

Subaddressing is not possible in MPEG mode; this means, in multi-DAC systems, only one DAC 3550A can run in MPEG mode.

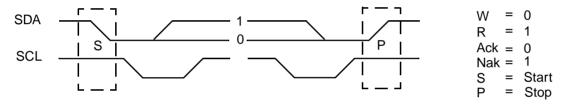

# 2.11. I<sup>2</sup>C Bus Interface

The DAC 3550A is equipped with an I<sup>2</sup>C bus slave interface. The I<sup>2</sup>C bus interface uses one level of sub-addressing: The I<sup>2</sup>C bus address is used to address the IC. The subaddress allows chip select in multi DAC applications and selects one of the three internal registers. The registers are write-only. The I<sup>2</sup>C bus chip address is given below.

The registers of the DAC 3550A have 8- or 16-bit data size; 16-bit registers are accessed by writing two 8-bit data words.

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0   |

dev write = \$9A.

| S | dev_write | Ack | sub_adr | Ack | 1 byte data | Ack | Р    | 8-bit I <sup>2</sup> C write access |     |   |                                      |

|---|-----------|-----|---------|-----|-------------|-----|------|-------------------------------------|-----|---|--------------------------------------|

| S | dev_write | Ack | sub_adr | Ack | 1 byte data | Ack | 1 by | te data                             | Ack | Р | 16-bit I <sup>2</sup> C write access |

Fig. 2–6: I<sup>2</sup>C bus protocols for write operations

#### 2.12. Registers

In Section 3.6. "Control Registers" on page 15, a definition of the DAC 3550A control registers is shown. A hardware reset initializes all control registers to 0. The automatic chip initialization loads a selected set of registers with the default values given in the table.

All registers are write-only.

The register address is coded by 3 bits (RA1, RA0) according to Table 2–3.

Table 2–3: I<sup>2</sup>C Register Address

| RA1 | RA0 | Mnemonics |

|-----|-----|-----------|

| 0   | 1   | SR_REG    |

| 1   | 0   | AVOL      |

| 1   | 1   | GCFG      |

The mnemonics used in the DAC 3550A demo software of Micronas are given in the last column.

#### 2.13. Chip Select

Chip select allows to connect up to four DAC 3550A to an  $I^2C$  control bus. The chip subaddresses are defined by the MCS1/MCS2 (Mode and Chip Select) pins. Only in standard mode, chip select is possible. MPEG mode always uses chip subaddress 3.

Register address and chip select are mapped into the subaddress field in Table 2–4.

# 2.14. Reduced Feature Mode

If I<sup>2</sup>C control is not used, the IC is in the default mode (see Section 3.6. "Control Registers" on page 15) after start-up. Default Volume setting is 0 dB and digital audio input is set to standard I<sup>2</sup>S. Sample rates from 32 kHz to 48 kHz are supported in this mode. Applications with no need for volume control or analog input could use this mode.

Table 2-4: I<sup>2</sup>C Subaddress

| 7    | 6    | 5 | 4 | 3 | 2 | 1   | 0   |

|------|------|---|---|---|---|-----|-----|

| MCS2 | MCS1 |   |   |   |   | RA1 | RA0 |

# 3. Specifications

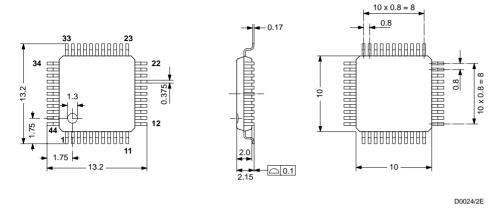

# 3.1. Outline Dimensions

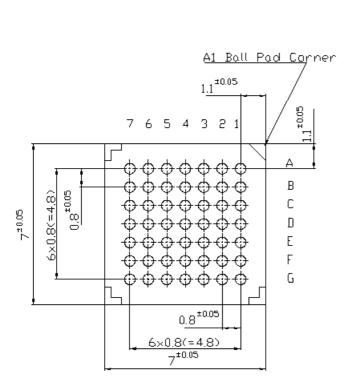

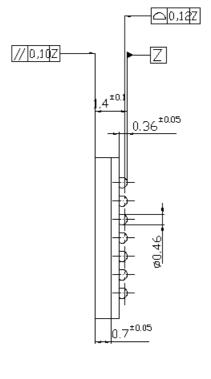

Fig. 3–1: 44-Pin Plastic Metric Quad Flat Package (PMQFP44) Weight approximately 0.4 g Dimensions in mm

# 3.2. Pin Connections and Short Descriptions

NC = not connected, leave vacant LV = if not used, leave vacant

VSS = if not used, connect to VSS

X = obligatory; connect as described in application

diagram

VDD = connect to VDD

| Pin<br>No. | Pin Name | Туре   | Connection (if not used) | Short Description                          |

|------------|----------|--------|--------------------------|--------------------------------------------|

| 1          | AGNDC    | IN/OUT | Х                        | Analog reference Voltage                   |

| 2          | AVSS1    | IN     | Х                        | VSS 1 for audio back-end                   |

| 3          | AVSS0    | IN     | Х                        | VSS 0 for audio output amplifiers          |

| 4          | NC       |        | LV                       | Not connected                              |

| 5          | OUTL     | OUT    | LV                       | Audio Output: Headphone left or Speaker +  |

| 6          | NC       |        | LV                       | Not connected                              |

| 7          | OUTR     | OUT    | LV                       | Audio Output: Headphone right or Speaker – |

| 8          | NC       |        | LV                       | Not connected                              |

| 9          | AVDD0    | IN     | Х                        | VDD 0 for audio output amplifiers          |

| 10         | AVDD1    | IN     | Х                        | VDD 1 for audio back-end                   |

| 11         | NC       |        | LV                       | Not connected                              |

| 12         | XTI      | IN     | Х                        | Quartz oscillator pin 1                    |

| 13         | хто      | IN/OUT | Х                        | Quartz oscillator pin 2                    |

| 14         | CLKOUT   | OUT    | LV                       | Clock Output                               |

| 15         | SCL      | IN/OUT | LV                       | I <sup>2</sup> C clock                     |

| Pin<br>No. | Pin Name | Туре   | Connection (if not used) | Short Description                                        |

|------------|----------|--------|--------------------------|----------------------------------------------------------|

| 16         | SDA      | IN/OUT | LV                       | I <sup>2</sup> C data                                    |

| 17         | VSS      | IN     | Х                        | Digital VSS                                              |

| 18         | VDD      | IN     | Х                        | Digital VDD                                              |

| 19         | MCS1     | IN     | Х                        | I <sup>2</sup> C Chip Select 1                           |

| 20         | MCS2     | IN     | Х                        | I <sup>2</sup> C Chip Select 2                           |

| 21         | DEECTRL  | IN     | VSS                      | Deemphasis on/off Control                                |

| 22         | NC       |        | LV                       | Not connected                                            |

| 23         | CLI      |        | VSS                      | I <sup>2</sup> S Bit Clock                               |

| 24         | DAI      | IN     | VSS                      | I <sup>2</sup> S Data                                    |

| 25         | WSI      | IN     | VSS                      | I <sup>2</sup> S Frame Identification                    |

| 26         | PORQ     | IN     | VDD                      | Power-On Reset, active-low                               |

| 27         | TESTEN   | IN     | Х                        | Test Enable                                              |

| 28         | NC       |        | LV                       | Not connected                                            |

| 29         | AUX2L    | IN     | LV                       | AUX2 left input for external analog signals (e.g. tape)  |

| 30         | AUX2R    | IN     | LV                       | AUX2 right input for external analog signals (e.g. tape) |

| 31         | AUX1L    | IN     | LV                       | AUX1 left input for external analog signals (e.g. FM)    |

| 32         | AUX1R    | IN     | LV                       | AUX1 right input for external analog signals (e.g. FM)   |

| 33         | NC       |        | LV                       | Not connected                                            |

| 34         | DEEML    | OUT    | LV                       | Deemphasis Network Left                                  |

| 35         | DEEMR    | OUT    | LV                       | Deemphasis Network Right                                 |

| 36         | NC       |        | LV                       | Not connected                                            |

| 37         | FOUTL    | OUT    | Х                        | Output to left external filter                           |

| 38         | FOPL     | IN/OUT | Х                        | Filter op amp inverting input, left                      |

| 39         | FINL     | IN/OUT | Х                        | Input for FOUTL or filter op amp output (line out)       |

| 40         | NC       |        | LV                       | Not connected                                            |

| 41         | FOUTR    | OUT    | Х                        | Output to right external filter                          |

| 42         | FOPR     | IN/OUT | Х                        | Right Filter op amp inverting input                      |

| 43         | FINR     | IN/OUT | Х                        | Input for FOUTR or filter op amp output (line out)       |

| 44         | VREF     | IN     | X                        | Analog reference Ground                                  |

#### 3.3. Pin Descriptions

### 3.3.1. Power Supply Pins

The DAC 3550A combines various analog and digital functions which may be used in different modes. For optimized performance, major parts have their own power supply pins. All VSS power supply pins must be connected.

# **VDD (18)**

VSS (17)

The VDD and VSS power supply pair are connected internally with all digital parts of the DAC 3550A.

# AVDD0 (9) AVSS0 (3)

AVDD0 and AVSS0 are separate power supply pins that are exclusively used for the on-chip headphone/loudspeaker amplifiers.

# AVDD1 (10) AVSS1 (2)

The AVDD1 and AVSS1 pins supply the analog audio processing parts, except for the headphone/loud-speaker amplifiers.

# 3.3.2. Analog Audio Pins

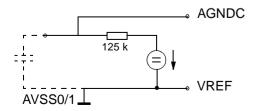

# AGNDC (1)

Reference for analog audio signals. This pin is used as reference for the internal op amps. This pin must be blocked against VREF with a 3.3  $\mu$ F capacitor.

**Note:** The pin has a typical DC-level of 1.5/2.25 V. It can be used as reference input for external op amps when no current load is applied.

#### **VREF (44)**

Reference ground for the internal band-gap and biasing circuits. This pin should be connected to a clean ground potential. Any external distortions on this pin will affect the analog performance of the DAC 3550A.

**AUX1L (31)**

**AUX1R (32)**

**AUX2L (29)**

**AUX2R (30)**

The AUX pins provide two analog stereo inputs. Auxiliary input signals, e.g. the output of a conventional receiver circuit or the output of a tape recorder can be connected with these inputs. The input signals have to be connected by capacitive coupling.

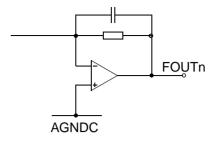

**FOUTL (37)**

**FOPL (38)**

FINL (39)

**FOUTR (41)**

**FOPR (42)**

**FINR (43)**

Filter op amps are provided in the analog baseband signal paths. These inverting op amps are freely accessible for external use by these pins.

The FOUTL/R pins are connected with the buffered output of the internal switch matrix. The FOPL/R-pins are directly connected with the inverting inputs of the filter op amps. The FINL/R pins are connected with the outputs of the op amps. The driving capability of the FOUTL/R pins is not sufficient for standard line output signals. Only the FINL/R pins are suitable for line output.

### OUTL (5) OUTR (7)

The OUTL/R pins are connected to the internal output amplifiers. They can be used for either stereo headphones or a mono loudspeaker. The signal of the right channel amplifier can be inverted for mono loudspeaker operation.

**Caution:** A short circuit at these pins for more than a momentary period may result in destruction of the internal circuits.

#### 3.3.3. Oscillator and Clock Pins

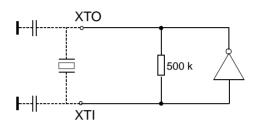

# XTI (12)

XTO (13)

The XTI pin is connected to the input of the internal crystal oscillator, the XTO pin to its output. Both pins should be directly connected to the crystal and two ground-connected capacitors (see application diagram).

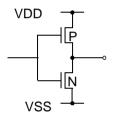

# CLKOUT (14)

The CLKOUT pin provides a buffered output of the crystal oscillator.

**Caution:** Power dissipation limit may be exceeded in case of short to VSS or VDD.

**CLI (23)**

DAI (24)

WSI (25)

These three pins are inputs for the digital audio data DAI, frame indication signal WSI, and bit clock CLI. The digital audio data is transmitted in an I<sup>2</sup>S-compatible format. Audio word lengths of 16 and 32 bits are supported, as well as SONY and Philips I<sup>2</sup>S protocol.

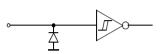

#### **SCL (15)**

**SDA (16)**

SCL (serial clock) and SDA (serial data) provide the connection to the serial control interface (I<sup>2</sup>C).

#### 3.3.4. Other Pins

# **TESTEN (27)**

Test enable. This pin is for test purposes only and must always be connected to VSS.

#### **PORQ (26)**

This pin may be used to reset the chip. If not used, this pin must be connected to VDD.

# **DEEML (34) DEEMR (35)**

These pins connect an external analog deemphasis network to the signal path in the analog back-end. This connection can be switched on and off by an internal switch which is controlled either by  $I^2C$  or the DEECTRL-pin.

# DEECTRL (21)

If no I<sup>2</sup>C-control is used, deemphasis can be switched on and off with this pin.

# MCS1 (19) MCS2 (20)

Mode select pins to select MPEG, Standard Mode, and I<sup>2</sup>C subaddress.

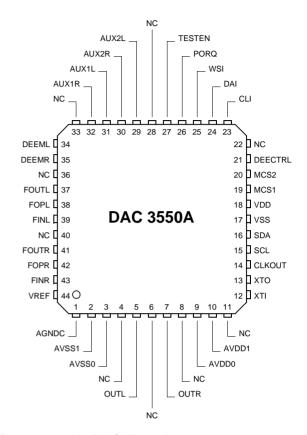

# 3.4. Pin Configuration

Fig. 3-2: 44-pin PMQFP package

#### 3.5. Pin Circuits

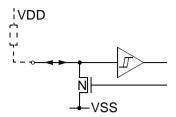

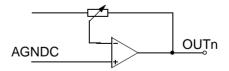

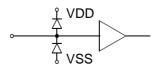

Fig. 3-3: Input/Output Pins SDA, SCL

Fig. 3-4: Input Pins DAI, WSI, PORQ, CLI

Fig. 3-5: Output Pin CLKOUT

Fig. 3–6: Pins FINR, FOPR, FINL, FOPL, DEEML, DEEMR

Fig. 3-7: Pins AGNDC, VREF

Fig. 3-8: Output Pins FOUTL, FOUTR

Fig. 3-9: Input/Output Pins XTI, XTO

Fig. 3–10: Input Pins AUX1R, AUX1L, AUX2R, AUX2L, AGNDC

Fig. 3-11: Output Pins OUTL, OUTR

Fig. 3-12: Input Pins MCS1, MCS2, DEECTRL

14

# 3.6. Control Registers

| I <sup>2</sup> C Sub-<br>address<br>(hex) | Number of Bits | Mode | Function                                                                                                                                     | Default<br>Values<br>(hex) | Name                                                             |

|-------------------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------|

| SAMPLE                                    |                |      |                                                                                                                                              |                            |                                                                  |

| 01                                        | 8              | w    | sample rate control                                                                                                                          | 0H                         |                                                                  |

|                                           |                |      | bit[7:5] not used, set to 0                                                                                                                  |                            |                                                                  |

|                                           |                |      | bit[4] L/R-bit<br>0 (WSI = 0 $\rightarrow$ left channel) <sup>1)</sup><br>1 (WSI = 0 $\rightarrow$ right channel) <sup>1)</sup>              |                            | LR_SEL                                                           |

|                                           |                |      | bit[3] Delay-Bit<br>0 No Delay<br>1 1 bit Delay                                                                                              |                            | SP_SEL                                                           |

|                                           |                |      | bit[2:0] sample rate control 000 32–48 kHz 001 26–32 kHz 010 20–26 kHz 011 14–20 kHz 100 10–14 kHz 101 8–10 kHz 11x <sup>2)</sup> autoselect |                            | SRC_48<br>SRC_32<br>SRC_24<br>SRC_16<br>SRC_12<br>SRC_8<br>SRC_A |

| ANALOG                                    | VOLUME         | AVOL |                                                                                                                                              | <br>                       |                                                                  |

| 02                                        | 16             | w    | audio volume control                                                                                                                         | 2C2CH                      |                                                                  |

|                                           |                |      | bit[15] not used, set to 0                                                                                                                   |                            |                                                                  |

|                                           |                |      | bit[14] deemphasis on/off<br>0 deemphasis off<br>1 deemphasis on                                                                             |                            | DEEM                                                             |

|                                           |                |      | bit[13:8] analog audio volume level left: 000000 mute 000001 -75 dB 101100 +0 dB (default) 111000 +18 dB                                     |                            | AVOL_L                                                           |

|                                           |                |      | bit[7:6] not used, set to 0                                                                                                                  |                            |                                                                  |

|                                           |                |      | bit[5:0] analog audio volume level right 000000 mute 000001 -75 dB 101100 +0 dB (default) 111000 +18 dB                                      |                            | AVOL_R                                                           |

| I <sup>2</sup> C Sub-<br>address<br>(hex) | Number<br>of Bits | Mode | Function | 1                                                        | Default<br>Values<br>(hex) | Name       |

|-------------------------------------------|-------------------|------|----------|----------------------------------------------------------|----------------------------|------------|

| Global C                                  | onfiguration      | GCFG |          |                                                          |                            |            |

| 03                                        | 8                 | W    | global c | onfiguration                                             | 4H                         |            |

|                                           |                   |      | bit[7]   | not used, set to 0                                       |                            |            |

|                                           |                   |      | bit[6]   | select 3V-5 V mode<br>0 3 V<br>1 5 V                     |                            | SEL_53V    |

|                                           |                   |      | bit[5]   | power-mode<br>0 normal<br>1 low power                    |                            | PWMD       |

|                                           |                   |      | bit[4]   | AUX2 select<br>0 AUX2 off<br>1 AUX2 on                   |                            | INSEL_AUX2 |

|                                           |                   |      | bit[3]   | AUX1 select<br>0 AUX1 off<br>1 AUX1 on                   |                            | INSEL_AUX1 |

|                                           |                   |      | bit[2]   | DAC select<br>0 DAC off<br>1 DAC on (default)            |                            | INSEL_DAC  |

|                                           |                   |      | bit[1]   | aux-mono/stereo<br>0 stereo<br>1 mono                    |                            | AUX_MS     |

|                                           |                   |      | bit[0]   | invert right power amplifier  0 not inverted  1 inverted |                            | IRPA       |

#### 3.7. Electrical Characteristics

# 3.7.1. Absolute Maximum Ratings

| Symbol              | Parameter                                         | Pin<br>Name                                  | Min. | Max.                    | Unit |

|---------------------|---------------------------------------------------|----------------------------------------------|------|-------------------------|------|

| T <sub>A</sub>      | Ambient Operating Temperature <sup>1)</sup>       |                                              | 0    | 70                      | °C   |

| T <sub>S</sub>      | Storage Temperature                               |                                              | -40  | 125                     | °C   |

| P <sub>max</sub>    | Power Dissipation                                 |                                              |      | 500                     | mW   |

| V <sub>SUPA</sub>   | Analog Supply Voltage <sup>2)</sup>               | AVDD0/1                                      | -0.3 | 6                       | V    |

| V <sub>SUPD</sub>   | Digital Supply Voltage                            | VDD                                          | -0.3 | 6                       | V    |

| V <sub>Idig1</sub>  | Input Voltage, digital inputs                     | MCS1,<br>MCS2,<br>DEECTRL                    | -0.3 | V <sub>SUPD</sub> + 0.3 | V    |

| V <sub>Idig2</sub>  | Input Voltage, digital inputs                     | WSI,<br>CLI,<br>DAI,<br>PORQ,<br>SCL,<br>SDA | -0.3 | 6                       | V    |

| I <sub>Idig</sub>   | Input Current, all digital inputs                 |                                              | -5   | +5                      | mA   |

| V <sub>Iana</sub>   | Input Voltage, all analog inputs                  |                                              | -0.3 | V <sub>SUPA</sub> + 0.3 | V    |

| I <sub>lana</sub>   | Input Current, all analog inputs                  |                                              | -5   | +5                      | mA   |

| l <sub>Oaudio</sub> | Output Current, audio output <sup>3)</sup>        | OUTL/R                                       | -0.2 | 0.2                     | Α    |

| l <sub>Odig</sub>   | Output Current, all digital outputs <sup>4)</sup> |                                              | -10  | 10                      | mA   |

<sup>1) =</sup>standard temperature range, DAC 3550A tested in extended temperature range on request

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions/Characteristics" of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

<sup>2)</sup> Both have to be connected together!

<sup>3)</sup> These pins are NOT short-circuit proof!

<sup>4)</sup> Total chip power dissipation must not exceed absolute maximum rating

# 3.7.2. Recommended Operating Conditions

| Symbol              | Parameter                                                               | Pin Name              | Min.                         | Тур.      | Max.  | Unit             |

|---------------------|-------------------------------------------------------------------------|-----------------------|------------------------------|-----------|-------|------------------|

| Temperature         | Ranges and Supply Voltages                                              |                       |                              |           |       | •                |

| T <sub>A</sub>      | Ambient Temperature Range <sup>1)</sup>                                 |                       | 0                            |           | 70    | °C               |

| V <sub>SUPA1</sub>  | Analog Audio Supply Voltage                                             | AVDD0/1               | 3.0 <sup>2)</sup>            | 3.3       | 5.5   | V                |

| V <sub>SUPD</sub>   | Digital Supply Voltage                                                  | VDD                   | 2.7                          | 3.3       | 5.5   | V                |

| Relative Sup        | oply Voltages                                                           |                       |                              |           | •     |                  |

| V <sub>SUPA</sub>   | Analog Audio Supply Voltage in relation to the Digital Supply Voltage   | AVDD0/1               | V <sub>SUPD</sub><br>-0.25 V |           | 5.5 V |                  |

| Analog Refe         | rence                                                                   |                       |                              | •         |       |                  |

| C <sub>AGNDC1</sub> | Analog Reference Capacitor                                              | AGNDC                 | 1.0                          | 3.3       |       | μF               |

| C <sub>AGNDC2</sub> | Analog Reference Capacitor                                              | AGNDC                 |                              | 10        |       | nF               |

| Analog Audi         | o Inputs                                                                |                       |                              | -         |       |                  |

| V <sub>AI</sub>     | Analog Input Voltage AC,<br>SEL_53V = 0                                 | AUXnL/R <sup>3)</sup> |                              | 0.35      | 0.7   | V <sub>rms</sub> |

| V <sub>AI</sub>     | Analog Input Voltage AC,<br>SEL_53V = 1                                 | AUXnL/R <sup>3)</sup> |                              | 0.525     | 1.05  | V <sub>rms</sub> |

| Analog Filter       | r Input and Output                                                      | 1                     | 1                            | 1         |       |                  |

| Z <sub>AFLO</sub>   | Analog Filter Load Output <sup>4)</sup>                                 | FOUTL/R               | 7.5                          |           | 6     | kΩ<br>pF         |

| Z <sub>AFLI</sub>   | Analog Filter Load Input <sup>4)</sup>                                  | FINL/R                | 5.0                          |           | 7.5   | kΩ<br>pF         |

| Analog Audi         | o Output                                                                |                       |                              |           |       | •                |

| Z <sub>LO</sub>     | Audio Line Output <sup>5)</sup> (680 $\Omega$ Series Resistor required) | FINL/R                | 10                           |           | 1.0   | kΩ<br>nF         |

| Z <sub>AOL_HP</sub> | Analog Output Load HP (47 Ω Series Resistor required)                   | OUTL/R                |                              | 32<br>400 |       | Ω<br>pF          |

| Z <sub>AOL_SP</sub> | Analog Output Load SP (bridged)                                         | OUTL/R                |                              | 32<br>50  |       | Ω<br>pF          |

|                     | Analog Output Load SP (Stereo)                                          |                       |                              | 16<br>100 |       | Ω<br>pF          |

<sup>1) =</sup> standard temperature range, DAC 3550A tested in extended temperature range on request

2) typically operable down to 2.7 V, without loss in performance

3) n = 1 or 2

4) Please refer to Section 4.2. "Recommended Low-Pass Filters for Analog Outputs" on page 25.

5) Please refer to Section 4.1. "Line Output Details" on page 25.

| Symbol                 | Parameter                                                   | Pin Name                     | Min.        | Тур.   | Max.        | Unit |  |  |

|------------------------|-------------------------------------------------------------|------------------------------|-------------|--------|-------------|------|--|--|

| I <sup>2</sup> C Input |                                                             |                              |             |        |             |      |  |  |

| f <sub>I2C1</sub>      | I <sup>2</sup> C Clock Frequency, I <sup>2</sup> S active   | SCL                          |             | 400    |             | kHz  |  |  |

| f <sub>I2C2</sub>      | I <sup>2</sup> C Clock Frequency, I <sup>2</sup> S inactive |                              |             | 100    |             | kHz  |  |  |

| Digital Inputs         |                                                             |                              |             | •      |             |      |  |  |

| V <sub>IH</sub>        | Input High Voltage                                          | CLI,<br>WSI,                 | 0.5×<br>VDD |        |             | V    |  |  |

| V <sub>IL</sub>        | Input Low Voltage                                           | DAI,<br>PORQ,<br>SCL,<br>SDA |             |        | 0.2×<br>VDD | V    |  |  |

| Quartz Chara           | cteristics                                                  |                              |             | •      |             |      |  |  |

| F <sub>P</sub>         | Load Resonance Frequency<br>at C <sub>I</sub> = 20 pF       |                              | 13.3        | 14.725 | 17          | MHz  |  |  |

| R <sub>EQ</sub>        | Equivalent Series Resistance                                |                              |             | 12     | 30          | Ω    |  |  |

| C <sub>0</sub>         | Shunt (parallel) Capacitance                                |                              |             | 3      | 5           | pF   |  |  |

| Load at CLKOUT Output  |                                                             |                              |             |        |             |      |  |  |

| C <sub>load</sub>      | Capacitance                                                 | CLKOUT                       | 0           |        | 50          | pF   |  |  |

<sup>1) =</sup>standard temperature range, DAC 3550A tested in extended temperature range on request

2) typically operable down to 2.7 V, without loss in performance

3) n = 1 or 2

4) Please refer to Section 4.2. "Recommended Low-Pass Filters for Analog Outputs" on page 25.

5) Please refer to Section 4.1. "Line Output Details" on page 25.

# 3.7.3. Characteristics

At  $T_A$  = 0 to 70 °C $^*$ ,  $V_{SUPD}$  = 2.7 to 5.5 V,  $V_{SUPA}$  = 3.0 to 5.5 V; typical values at  $T_J$  = 27 °C,  $V_{SUPD}$  =  $V_{SUPA}$  = 3.3 V, quartz frequency = 14.725 MHz, duty cycle = 50 %, positive current flows into the IC

| Symbol               | Parameter                                        | Pin Name                                                    | Min.                       | Тур.                       | Max. | Unit       | Test Conditions                                          |

|----------------------|--------------------------------------------------|-------------------------------------------------------------|----------------------------|----------------------------|------|------------|----------------------------------------------------------|

| Digital Supp         | oly                                              |                                                             |                            | •                          | •    | <u>'</u>   |                                                          |

| I <sub>VDD</sub>     | Current Consumption                              | VDD                                                         |                            | 5                          |      | mA         | V <sub>SUPD</sub> =3 V                                   |

| I <sub>VDD</sub>     | Current Consumption                              | VDD                                                         |                            | 8                          |      | mA         | V <sub>SUPD</sub> =5 V                                   |

| Digital Inpu         | t Pin – Leakage                                  |                                                             |                            |                            |      |            |                                                          |

| I <sub>I</sub>       | Input Leakage Current                            | CLI, WSI,<br>DAI,<br>TESTEN,<br>PORQ,<br>DEECTRL,<br>MCS1/2 |                            |                            | ±1   | μА         | $V_{GND} \le V_I \le V_{SUP}$                            |

| Digital Outp         | out Pin – Clock Out                              |                                                             |                            |                            |      |            |                                                          |

| V <sub>OH</sub>      | Output High Voltage                              | CLKOUT                                                      | V <sub>SUPD</sub><br>- 0.3 |                            |      | V          | no load at output                                        |

| V <sub>OL</sub>      | Output Low Voltage                               |                                                             |                            |                            | 0.3  | V          |                                                          |

| I <sup>2</sup> C Bus |                                                  |                                                             |                            | •                          | •    | 1          |                                                          |

| R <sub>on</sub>      | Output Impedance                                 | SCL, SDA                                                    |                            |                            | 60   | Ω          | $I_{load} = 5 \text{ mA},$<br>$V_{SUPD} = 2.7 \text{ V}$ |

| Analog Sup           | pply                                             |                                                             |                            |                            |      |            |                                                          |

| I <sub>AVDD</sub>    | Current Consumption<br>Analog Audio, SEL_53V = 0 | AVDD0/1                                                     |                            | 8<br>1.5                   | 11   | mA<br>mA   | PWMD = 0, Mute<br>PWMD = 1, Mute                         |

|                      | SEL_53V = 1                                      |                                                             |                            | 11<br>2                    | 15   | mA<br>mA   | PWMD = 0, Mute<br>PWMD = 1, Mute                         |

| PSRR <sub>AA</sub>   | Power Supply Rejection<br>Ratio for Analog Audio | AVDD0/1,<br>OUTL/R                                          |                            | 50                         |      | dB         | 1 kHz sine at<br>100 mV <sub>rms</sub>                   |

|                      | Output                                           |                                                             |                            | 20                         |      | dB         | $\leq$ 100 kHz sine at 100 mV $_{rms}$                   |

| PSRR <sub>LO</sub>   | Power Supply Rejection<br>Ratio for Line Output  | AVDD0/1,<br>FINL/R                                          |                            | 50                         |      | dB         | 1 kHz sine at<br>100 mV <sub>rms</sub>                   |

|                      |                                                  |                                                             |                            | 40                         |      | dB         | $\leq$ 100 kHz sine at 100 mV $_{rms}$                   |

| Reference I          | Frequency Generation                             |                                                             |                            |                            |      |            |                                                          |

| V <sub>DCXTI</sub>   | DC Voltage at Oscillator<br>Pins                 | XTI/O                                                       |                            | 0.5 *<br>V <sub>SUPA</sub> |      | V          |                                                          |

| C <sub>LI</sub>      | Input Capacitance at<br>Oscillator Pin           | XTI/O                                                       |                            | 3                          |      | pF         |                                                          |

| Vxtalout             | Voltage Swing at Oscillator<br>Pins, pp          | XTI/O                                                       | 60                         |                            | 100  | %<br>VSUPA |                                                          |

|                      | Oscillator Start-Up Time                         |                                                             |                            |                            | 50   | ms         | $AV_{DD}/V_{DD} \ge 2.5 \text{ V}$                       |

<sup>\* =</sup>standard temperature range, DAC 3550A tested in extended temperature range on request

| Symbol             | Parameter                                                         | Pin Name                      | Min.       | Тур. | Max. | Unit             | Test Conditions                                                                                                                                  |

|--------------------|-------------------------------------------------------------------|-------------------------------|------------|------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Aud         | lio                                                               |                               | ı          |      |      |                  |                                                                                                                                                  |

| V <sub>AO</sub>    | Analog Output Voltage AC                                          | OUTL/R,<br>FOUTL/R,<br>FINL/R | 0.65       | 0.7  | 0.75 | V <sub>rms</sub> | $SEL\_53V = 0, \\ R_L > 5 k\Omega, \\ Analog Gain = 0 dB \\ Input = 0 dBFS digital$                                                              |

|                    |                                                                   |                               | 1.0        | 1.05 | 1.1  | V <sub>rms</sub> | SEL_53V = 1                                                                                                                                      |

| G <sub>AUX</sub>   | Gain from Auxiliary Inputs to Line Outputs                        | AUXnL/R,<br>FINL/R            | -0.5       | 0    | 0.5  | dB               | $ f = 1 \text{ kHz, sine wave,} \\ R_L > 5 \text{ k}\Omega \\ 0.5 \text{ V}_{rms} \text{ to AUXnL/R} $                                           |

| P <sub>HP</sub>    | Output Power (Headphone)                                          | OUTL/R                        |            | 5    |      | mW               | $SEL\_53V = 0, \\ R_L = 32 \ \Omega, \\ Analog \ Gain = +3 \ dB, \\ distortion < 1\%, \\ external \ 47 \ \Omega \ series \\ resistor \ required$ |

|                    |                                                                   |                               |            | 12   |      | mW               | SEL_53V = 1                                                                                                                                      |

| P <sub>SP</sub>    | Output Power (Speaker)                                            | OUTL/R                        |            | 120  |      | mW               | $R_L = 32~\Omega~(bridged),$ Analog Gain = +3 dB,<br>distortion < 10%,<br>SEL_53V = 0, IRPA = 1                                                  |

|                    |                                                                   |                               |            | 280  |      | mW               | SEL_53V = 1                                                                                                                                      |

| G <sub>AO</sub>    | Analog Output Gain<br>Setting Range                               | OUTL/R                        | <b>-75</b> |      | 18   | dB               |                                                                                                                                                  |

| dG <sub>AO1</sub>  | Analog Output Gain<br>Step Size                                   | OUTL/R                        |            | 3.0  |      | dB               | Analog Gain:<br>-75 dB54 dB                                                                                                                      |

| dG <sub>AO2</sub>  | Analog Output Gain<br>Step Size                                   | OUTL/R                        |            | 1.5  |      | dB               | Analog Gain:<br>-54 dB+18 dB                                                                                                                     |

| E <sub>GA1</sub>   | Analog Output Gain Error                                          | OUTL/R                        | -2         |      | 2    | dB               | -46.5 dB≥Analog Gain<br>≥-54 dB                                                                                                                  |

| E <sub>GA2</sub>   | Analog Output Gain Error                                          | OUTL/R                        | -1         |      | 1    | dB               | -40.5 dB≥Analog Gain<br>≥-45 dB                                                                                                                  |

| E <sub>GA3</sub>   | Analog Output Gain Error                                          | OUTL/R                        | -0.5       |      | 0.5  | dB               | +18 dB≥Analog Gain<br>≥–39 dB                                                                                                                    |

| E <sub>dGA</sub>   | Analog Output Gain<br>Step Size Error                             | OUTL/R                        | -0.5       |      | 0.5  | dB               | +18 dB≥Analog Gain<br>≥–48 dB                                                                                                                    |

| SNR <sub>AUX</sub> | Signal-to-Noise Ratio from<br>Analog Input to Line Output         | AUXn,<br>FINL/R               |            | 98   |      | dB               | SEL_53V = 0:<br>input -40 dB below                                                                                                               |

|                    | Signal-to-Noise Ratio from<br>Analog Input to Headphone<br>Output | AUXn,<br>OUTn                 |            | 93   |      | dB               | 0.7 V <sub>rms</sub> Analog Gain = 0 dB, BW =20 Hz20 kHz unweighted                                                                              |

| Symbol              | Parameter                                                       | Pin Name           | Min. | Тур. | Max. | Unit | Test Conditions                                                                                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------|--------------------|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SNR <sub>1</sub>    | Signal-to-Noise Ratio                                           | OUTL/R             | 89   | 91   |      | dB   | $\begin{array}{l} R_L \geq 32~\Omega \\ \text{(external 47 $\Omega$ series} \\ \text{resistor required)} \\ \text{BW =20 Hz0.5 fs} \\ \text{unweighted,} \\ \text{Analog Gain = 0 dB,} \\ \text{Input = $-20$ dBFS} \\ \end{array}$ |

|                     |                                                                 | FINL/R             | 90   | 92   |      | dB   | $R_L \ge 5 \text{ k}\Omega$ ,<br>$R_{dec} \ge 612 \Omega$<br>BW etc. as above<br>$16 \text{ bit } I^2 \text{S}$ , $\text{SEL\_} 53 \text{V} = 0$                                                                                    |

|                     |                                                                 |                    |      | 94   |      | dB   | 32 bit $I^2$ S, SEL_53V = 0                                                                                                                                                                                                         |

|                     |                                                                 |                    |      | 96   |      | dB   | 16 bit I <sup>2</sup> S, SEL_53V = 1                                                                                                                                                                                                |

|                     |                                                                 |                    |      | 98   |      | dB   | 32 bit I <sup>2</sup> S, SEL_53V = 1                                                                                                                                                                                                |

|                     |                                                                 |                    |      | 103  |      | dBA  | 32 bit $I^2$ S, SEL_53V = 1                                                                                                                                                                                                         |

| SNR <sub>2</sub>    | Signal-to-Noise Ratio                                           | OUTL/R             | 58   | 62   |      | dB   | $R_L \ge 32~\Omega$ (external 47 $\Omega$ series resistor required) BW = 20 Hz0.5 fs unweighted Analog Gain = $-40.5$ dB, Input = $-3$ dBFS                                                                                         |

| Lev <sub>Mute</sub> | Mute Level                                                      | OUTL/R             |      | -110 |      | dBV  | BW = 20 Hz22 kHz<br>unweighted, no digital<br>input signal,<br>Analog Gain = Mute                                                                                                                                                   |

| R <sub>D/A</sub>    | D/A Pass Band Ripple                                            | OUTL/R,<br>FOUTL/R |      | -0.1 |      | dB   | 00.446 fs<br>(no external filters<br>used)                                                                                                                                                                                          |

| A <sub>D/A</sub>    | D/A Stop Band Attenuation                                       |                    |      | 40   |      | dB   | 0.557.533 fs<br>(no external filters<br>used)                                                                                                                                                                                       |

| BW <sub>AUX</sub>   | Bandwidth for<br>Auxiliary Inputs                               | AUXnL/R,<br>FINL/R |      | 760  |      | kHz  | (no external filters used)                                                                                                                                                                                                          |

| THD <sub>ALO</sub>  | Total Harmonic Distortion from Auxiliary Inputs to Line Outputs | AUXnL/R,<br>FINL/R |      |      | 0.01 | %    | $BW = 20 \text{ Hz22 kHz,} \\ \text{unweighted,} \\ R_{\text{L}} > 5 \text{ k}\Omega \\ \text{Input 1 kHz at 0.5 V}_{\text{rms}} \\ R_{\text{dec}} \ge 612 \Omega$                                                                  |

| THD <sub>DLO</sub>  | Total Harmonic Distortion<br>(D/A converter to Line<br>Output)  | FINL/R             |      |      | 0.01 | %    | $BW = 20 \ Hz 0.5 \ fs,$ unweighted, $R_L > 5 \ k\Omega$ Input 1 kHz at $-3 \ dBFS$ $R_{dec} \ge 612 \ \Omega$                                                                                                                      |

| THD <sub>HP</sub>   | Total Harmonic Distortion (Headphone)                           | OUTL/R             |      |      | 0.05 | %    | $BW = 20 \ Hz0.5 \ fs,$ unweighted, $R_L \ge 32 \ \Omega$ (47 $\Omega$ series resistor required), Analog Gain = 0 dB, Input 1 kHz at $-3$ dBFS                                                                                      |

| Symbol              | Parameter                                         | Pin Name                       | Min. | Тур. | Max. | Unit | Test Conditions                                                                                                                                                                                                                                                                                                       |

|---------------------|---------------------------------------------------|--------------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THD <sub>SP</sub>   | Total Harmonic Distortion<br>(Speaker)            | OUTL/R                         |      |      | 0.5  | %    | $BW = 20 \text{ Hz} 0.5 \text{ fs,} \\ \text{unweighted, } R_L \geq 32 \ \Omega \\ \text{(speaker bridged),} \\ \text{Analog Gain} = 0 \text{ dB,} \\ \text{Input 1 kHz at} -3 \text{ dBFS}$                                                                                                                          |

| XTALK <sub>LO</sub> | Cross-Talk<br>Left/Right Channel<br>(Line Output) | AUXnL/R,<br>FOUTL/R,<br>FINL/R | -70  | -80  |      | dB   | $\begin{array}{l} f=1\text{ kHz, sine wave,} \\ R_L>7.5\text{ k}\Omega \\ \text{Analog Gain}=0\text{ dB,} \\ \text{Input}=-3\text{ dBFS or} \\ 0.5\text{ V}_{rms}\text{ to AUXnL/R} \\ \end{array}$                                                                                                                   |

| XTALK <sub>HP</sub> | Crosstalk<br>Left/Right Channel<br>(Headphone)    | OUTL/R                         | -70  | -80  |      | dB   | $\begin{array}{l} f=1 \text{ kHz, sine wave,} \\ \text{OUTL/R: } R_L \geq 32 \; \Omega \\ \text{(47 } \Omega \text{ series resistor required)} \\ \text{Analog Gain} = 0 \text{ dB,} \\ \text{Input} = -3 \text{ dBFS or} \\ 0.5 \text{ V}_{rms} \text{ to AUXnL/R} \\ \end{array}$                                   |

| XTALK <sub>2</sub>  | Crosstalk between<br>Input Signal Pairs           | AUXnL/R                        | -70  | -80  |      | dB   | $\begin{array}{l} f=1\text{ kHz, sine wave,} \\ \text{FOUTL/R: } R_{L} > 7.5\text{ k}\Omega \\ \text{OUTL/R: } R_{L} \geq 32\Omega \\ \text{(47 }\Omega\text{ series resistor required)} \\ \text{Analog Gain} = 0\text{ dB,} \\ \text{Input} = -3\text{ dBFS and} \\ 0.5\text{ $V_{rms}$ to AUXnL/R} \\ \end{array}$ |

| V <sub>AGNDC</sub>  | Analog Reference Voltage                          | AGNDC                          |      | 1.5  |      | V    | $\begin{array}{l} \text{SEL\_53V} = 0 \\ \text{R}_{\text{L}} >> 10 \; \text{M}\Omega, \\ \text{referred to VREF} \end{array}$                                                                                                                                                                                         |

|                     |                                                   |                                |      | 2.25 |      | V    | $\begin{array}{c} \text{SEL\_53V} = 1 \\ \text{R}_{\text{L}} >> 10 \text{ M}\Omega, \\ \text{referred to VREF} \end{array}$                                                                                                                                                                                           |

| Symbol             | Parameter                                                                       | Pin Name | Min.         | Тур.  | Max.         | Unit     | Test Conditions                                                                                                                                                                                      |

|--------------------|---------------------------------------------------------------------------------|----------|--------------|-------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>IAUX</sub>  | Input Resistance at<br>Input Pins                                               | AUXnL/R  | 12.1<br>11.6 | 15    | 17.9<br>19.0 | kΩ<br>kΩ | $\begin{array}{l} T_J = 27~^{\circ}C \\ T_A = 0 \text{ to } 70~^{\circ}C^{1)} \\ \text{Input selected,} \\ \text{PWMD} = 0 \\ \text{i} = \pm 10~\mu\text{A,} \\ \text{referred to VREF} \end{array}$ |

|                    |                                                                                 |          | 24.2<br>23.3 | 30    | 35.8<br>37.9 | kΩ<br>kΩ | $\begin{split} T_J &= 27~^{\circ}\text{C} \\ T_A &= 0 \text{ to } 70~^{\circ}\text{C}^{1)} \\ \text{Input not selected} \\ i &= \pm 10~\mu\text{A}, \\ \text{referred to VREF} \end{split}$          |

| R <sub>OOUT</sub>  | Output Resistance at<br>Output Pins                                             | OUTL/R   |              | 700   |              | Ω        | $T_J$ = 27 °C<br>PWMD = 1<br>i = $\pm$ 200 $\mu$ A,<br>referred to VREF                                                                                                                              |

| R <sub>OFILT</sub> | Output Resistance of Filter Pins                                                | FINL     |              | 15    |              | kΩ       | PWMD = 1, Mute                                                                                                                                                                                       |

|                    | Filter Pins                                                                     | FINR     |              | 11.25 |              | kΩ       | $i = \pm 10 \mu A$ ,<br>referred to VREF                                                                                                                                                             |

| V <sub>Offl</sub>  | Offset Voltage at Input Pins                                                    | AUXnL/R  | -20          |       | 20           | mV       | referred to AGNDC                                                                                                                                                                                    |

| V <sub>OffO</sub>  | Offset Voltage at<br>Output Pins                                                | OUTL/R   | -10          |       | 10           | mV       | Mute referred to AGNDC                                                                                                                                                                               |

| V <sub>OffFO</sub> | Offset Voltage at Filter Output Pins                                            | FOUTL/R  | -20          |       | 20           | mV       | PWMD = 0,<br>referred to AGNDC                                                                                                                                                                       |

| V <sub>OffFI</sub> | Offset Voltage at Filter Input Pins                                             | FINL/R   | -20          |       | 20           | mV       | PWMD = 0,<br>referred to AGNDC                                                                                                                                                                       |

| dV <sub>DCPD</sub> | Difference of DC Voltage at<br>Output Pins after Back-end<br>Low Power Sequence | OUTL/R   | -10          |       | 10           | mV       | Analog Gain = Mute,<br>PWMD switched from 0<br>to 1                                                                                                                                                  |

# 4. Applications

# 4.1. Line Output Details

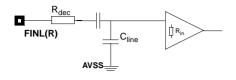

Fig. 4-1: Use of FINL/R as Line Outputs

**Table 4–1:** Load at FINL/R when used as Line Output for external amplifier

| Filter Order                                                           | R <sub>dec</sub>                     | R <sub>in</sub>        |  |  |  |

|------------------------------------------------------------------------|--------------------------------------|------------------------|--|--|--|

| 1st, 2nd, 3rd                                                          | 680 Ω                                | > 10 kΩ                |  |  |  |

|                                                                        | sed for decoupling achieve stability | C <sub>line</sub> from |  |  |  |

| C <sub>line</sub> : Capacitive load according to e.g. cable, amplifier |                                      |                        |  |  |  |

| R <sub>in</sub> : Input resistance of amplifier                        |                                      |                        |  |  |  |

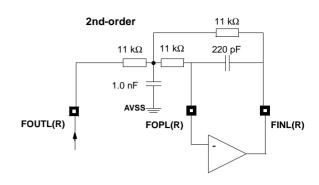

# 4.2. Recommended Low-Pass Filters for Analog Outputs\*

Fig. 4-2: 1st-order low-pass filter

Table 4-2: Attenuation of 1st-order low-pass filter

| Frequency | Gain    |

|-----------|---------|

| 24 kHz    | -2.2 dB |

| 30 kHz    | -3.0 dB |

Fig. 4-3: 2nd-order low-pass filter

Table 4-3: Attenuation of 2nd-order low-pass filter

| Frequency | Gain    |

|-----------|---------|

| 24 kHz    | -1.5 dB |

| 30 kHz    | -3.0 dB |

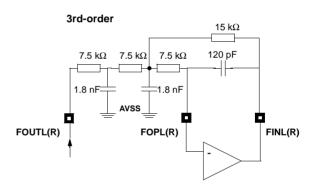

Fig. 4-4: 3rd-order low-pass filter

Table 4-4: Attenuation of 3rd-order low-pass filter

| Frequency | Gain     |

|-----------|----------|

| 18 kHz    | 0.17 dB  |

| 24 kHz    | -0.23 dB |

| 30 kHz    | -3.00 dB |

<sup>\*</sup> without deemphasis circuit

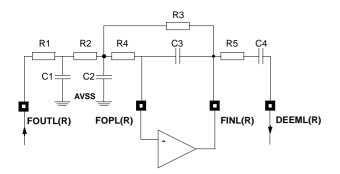

# 4.3. Recommendations for Filters and Deemphasis

Fig. 4-5: General circuit schematic

Table 4-5: Resistor and Capacitor values

|         | 1st order | 2nd order | 3rd order |

|---------|-----------|-----------|-----------|

| R1 (kΩ) | 0         |           | 7.5       |

| C1 (pF) | open      |           | 560       |

| R2 (kΩ) | 18        | 11        | 7.5       |

| C2 (pF) | open      | 1000      | 270       |

| R3 (kΩ) | 18        | 11        | 15        |

| C3 (pF) | 180       | 180       | 82        |

| R4 (kΩ) | 0         | 11        | 7.5       |

| R5 (kΩ) | 18        | 22        | 22        |

| C4 (nF) | 1.8       | 1.0       | 1.0       |

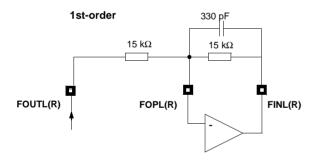

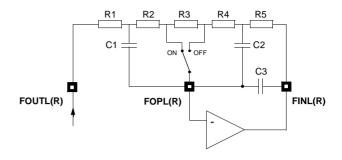

# 4.4. Recommendations for MegaBass Filter without Deemphasis plus 1st-order low-pass

Fig. 4-6: General circuit schematic

Table 4-6: Resistor and Capacitor values

|         | DC-Gain = 10 dB<br>fc1 = 100 Hz<br>fc2 = 330 Hz |

|---------|-------------------------------------------------|

| R1 (kΩ) | 13                                              |

| C1 (nF) | 47                                              |

| R2 (kΩ) | 0                                               |

| R3 (kΩ) | 15                                              |

| R4 (kΩ) | 15                                              |

| R5 (kΩ) | 13                                              |

| C2 (nF) | 47                                              |

| C3 (pF) | 180                                             |

# 4.5. Power-up/down Sequence

In order to get a click-free power-up/down characteristic, it is recommended to use the following sequences:

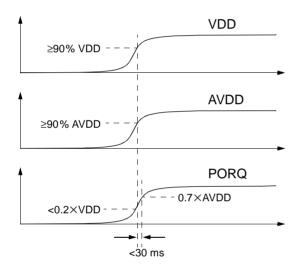

#### 4.5.1. Power-up Sequence

- 1. Start VDD from 0 to +3.3 V and start AVDD0/1 from 0 to +3.3 V/+5 V. AVDD should not ramp up faster than VDD.

- 2. Release PORQ from 0 to AVDD0/1.

- 3. Send I2C: volume, input select, speaker, ... optional.

- 4. Start I2S data.

The most important point is: PORQ has to ramp up after AVDD0/1, simply by using a 10-k $\Omega$  pull-up resistor to AVDD0/1 and a 2.2-nF capacitor to ground. No further control on PORQ is needed.

Fig. 4-7: Power-up sequence

### 4.5.2. Power-down Sequence

- 1. Stop I2S data.

- 2. Send I2C: LOW POWER.

- 3. Switch VDD. AVDD0/1 to 0.

Fig. 4-8: Application circuit schematic 1: Standard application with analog deemphasis. Oscillator not needed

Fig. 4-10: MPEG Layer-3 Player

Fig. 4-11: CD-Player with FM-Radio

Fig. 4-12: ADR Receiver

#### 5. Data Sheet History