# ML2200, ML2208

# 12-Bit Plus Sign Data Acquisition Peripheral

## **GENERAL DESCRIPTION**

The ML2200 and ML2208 Data Acquisition Peripherals (DAP) are monolithic CMOS data acquisition subsystems. These data acquisition peripherals feature an input multiplexer, a programmable gain instrumentation amplifier, a 2.5V bandgap reference, and a 12-bit plus sign A/D converter with built-in sample-and-hold. In addition to a general purpose 8-bit microprocessor interface, the ML2200 and ML2208 include a programmable processor, data buffering, a 16-bit timer, and limit alarms.

The ML2200B and ML2208B self-calibrating algorithmic A/D converters have a maximum non-linearity error over temperature of 0.018% of full-scale, while the ML2200C, ML2200D, ML2208C, and ML2208D have a maximum non-linearity error over temperature of 0.024%.

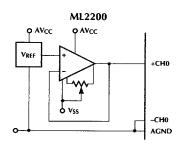

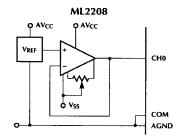

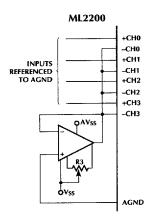

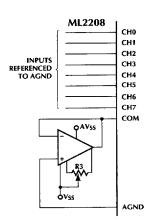

The ML2200 has a four channel differential input multiplexer and the ML2208 has an eight channel single ended input multiplexer.

The digital interface, with software-alterable configurations, is designed to off-load the microprocessor. Control of the DAP is autonomously handled through the control sequencer which receives its instructions from the instruction RAM.

# **FEATURES**

■ Resolution

12-bits + sign

■ Conversion time

(including S/H acquisition)

31.5µs max

■ Sample-and-hold acquisition

2.3µs max

■ Non-linearity error

±3/4 LSB and ±1 LSB max

■ Low harmonic distortion

0.01%

■ No missing codes

Self-calibrating — maintains accuracy over time and temperature

■ Inputs withstand |7V| beyond supplies

■ Internal voltage reference

$2.5V \pm 2\%$

■ Four differential or eight single-ended input channels

■ Data buffering (8 word data RAM)

■ Programmable limit alarm

■ 8-Bit microprocessor interface — interrupt, DMA, or polling

■ 16-Bit timer for programmable conversion rates

■ Standard hermetic 40-pin DIP

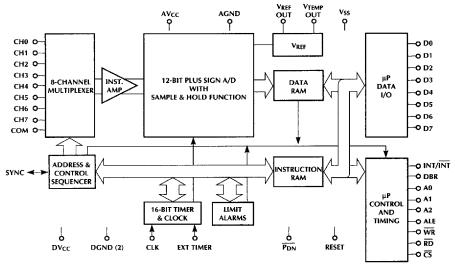

### **BLOCK DIAGRAM**

Micro Linear

2-3

■ 6093418 0003174 9T6 |

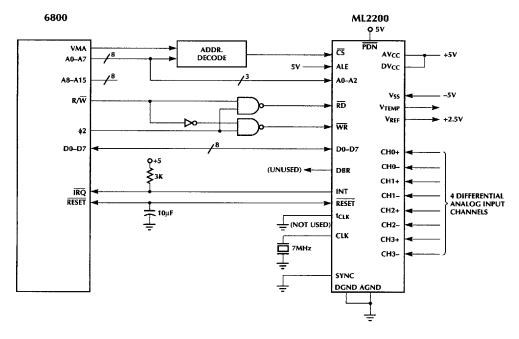

### ML2200 BLOCK DIAGRAM

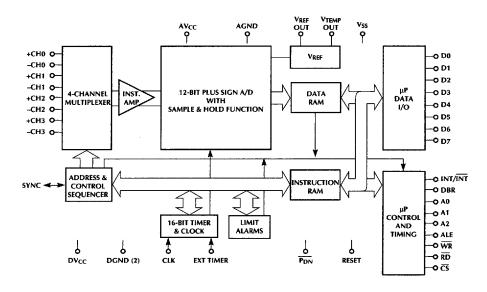

## **BLOCK SCHEMATIC DIAGRAM**

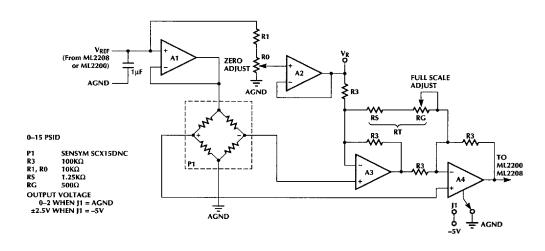

Figure 1. Block Schematic Diagram.

Micro Linear

2-4

6093418 0003175 832

# **PIN DESCRIPTION**

| PIN#               | NAME              | FUNCTION                                                                                                                                                                             | PIN# | NAME              | FUNCTION                                                                                                                                                                                                                                                  |

|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | AGND              | Analog Ground.                                                                                                                                                                       | 28   | DBR               | Data Buffer Ready output active                                                                                                                                                                                                                           |

| 2                  | $V_{TEMP}$        | Voltage output proportional to the die temperature.                                                                                                                                  |      |                   | high indicates that a sequence of<br>operations has completed and<br>data is ready to transfer. DBR is                                                                                                                                                    |

| 3                  | $V_{REF}$         | Internal voltage reference output                                                                                                                                                    |      |                   | not maskable. It can be used to                                                                                                                                                                                                                           |

| 4-11 CH  12 NC COM |                   | Analog Inputs. ML2200 — Positive or negative input of four differential inputs ML2208 — Eight single ended inputs referenced to common pin. Digitally selected by control sequencer. |      |                   | generate an interrupt in addition to the INT pin when the DBRIE bit in the interrupt mask register has not been enabled. DBR is th DMA request pin when DMA mode is enabled. DBR is not active unless in run mode and at least one sequence of operations |

|                    |                   | ML2200 — No connection. ML2208 — Negative common input for the eight input channels. Tie to analog ground or                                                                         |      |                   | has been completed. DBR remains active in the halt mode not acknowledged; low during reset time and power-down.                                                                                                                                           |

|                    |                   | $(V_{SS} + 2.5)$ to $(AV_{CC} - 2.5 \text{ V})$                                                                                                                                      | 29   | DGND              | Digital Ground.                                                                                                                                                                                                                                           |

| 13                 | V <sub>SS</sub>   | Negative power supply; decouple to AGND.                                                                                                                                             | 30   | CLK               | Clock input. Drive with an external clock or crystal reference                                                                                                                                                                                            |

| 14                 | P <sub>DN</sub>   | Power-Down Input When P <sub>DN</sub> = 0, device in power-down mode with register contents retained if AV <sub>CC</sub> >2.0V.                                                      |      |                   | to DGND. The crystal must be<br>parallel resonant with minimum<br>capacitive loading (i.e., No<br>bypass caps should be used and<br>leads should be kept short).                                                                                          |

| 15                 | NC                | No Connection.                                                                                                                                                                       | 31   | RESET             | •                                                                                                                                                                                                                                                         |

| 6-19               | D7, D6,<br>D5, D4 | Bidirectional data bits.                                                                                                                                                             | 31   | KESET             | Active low hardware reset with internal pull up resistor of 200K. Tie to system reset line or to                                                                                                                                                          |

| 20                 | DGND              | Digital Ground.                                                                                                                                                                      |      |                   | grounded capacitor. The capacitor size (usually >6μF) is based on the                                                                                                                                                                                     |

| 21                 | DV <sub>CC</sub>  | $V_{CC}$ Digital power supply. Tie to $AV_{CC}$ from same power supply.                                                                                                              |      |                   | time the power supplies stabilize, to the time reset voltage reaches 1.4V (>400ms).                                                                                                                                                                       |

| 22-25              | D3, D2,           | Bidirectional data bits.                                                                                                                                                             | 32   | T <sub>CLK</sub>  | External timer, T <sub>CLK</sub> is used as                                                                                                                                                                                                               |

| 26                 | D1, D0<br>SYNC    | In the slave mode, SYNC is a                                                                                                                                                         |      | CER               | external clock input for the 16-<br>bit timer when the T <sub>CLK</sub> bit in the<br>control register is set to one.                                                                                                                                     |

| 27                 | INT               | positive edge triggered input used to start a conversion. In master mode, SYNC is an output and indicates a conversion has occurred.                                                 | 33   | ALE               | Address latch enable, active low latches information on A0, A1, A2 and CS. Tie to AV <sub>CC</sub> to disable use when separate address and data bus are used.                                                                                            |

| 27                 | IINI              | Interrupt output. A maskable interrupt programmable to be                                                                                                                            | 34   | A2                | Address 2                                                                                                                                                                                                                                                 |

|                    |                   | active high or low or will default<br>to active high. INT will not clear                                                                                                             | 35   | A1                | Address 1                                                                                                                                                                                                                                                 |

|                    |                   | until acknowledged in halt                                                                                                                                                           | 36   | Α0                | Address 0                                                                                                                                                                                                                                                 |

|                    |                   | mode; not affected by the run or<br>halt state. INT = 0 during reset                                                                                                                 | 37   | CS                | Chip select, active low                                                                                                                                                                                                                                   |

|                    |                   | and inactive during P <sub>DN</sub> .                                                                                                                                                | 38   | RD                | Read, active low enables ML2200 or ML2208 to drive data bus.                                                                                                                                                                                              |

|                    |                   |                                                                                                                                                                                      | 39   | WR                | Write, active low allows writing into the registers.                                                                                                                                                                                                      |

|                    |                   |                                                                                                                                                                                      | 40   | A V <sub>CC</sub> | Positive analog Power supply.<br>Decouple to AGND. Tie to DV <sub>CC</sub><br>from same power supply                                                                                                                                                      |

Micro Linear

2-5

**■** 6093418 0003176 779 **■**

# PIN CONNECTIONS

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltages (AV <sub>CC</sub> and DV <sub>CC</sub> ) 6.0V         |

|-----------------------------------------------------------------------|

| Negative Supply Voltage (VSS) – 6.0V                                  |

| Voltage at Analog Inputs V <sub>SS</sub> – 7V to AV <sub>CC</sub> +7V |

| Voltage at $V_{RE}F$ $V_{SS}$ – 7V to $AV_{CC}$ +7V                   |

| Input Current per Digital Pin±10mA                                    |

| Input Current at Analog Inputs±20mA                                   |

| Storage Temperature Range – 65°C to +150°C                            |

| Package Dissipation @ 25° C1W                                         |

| Lead Temperature (Soldering 10 sec.)                                  |

| Dual-In-Line Package (Plastic)                                        |

# **OPERATING CONDITIONS**

(Note 2)

| n                                                     | T 2T 2T                                    |

|-------------------------------------------------------|--------------------------------------------|

| Temperature Range                                     |                                            |

| ML2200BCP, ML2200CCP, ML2                             |                                            |

| ML2208BCP, ML2208CCP, ML2                             | 208DCP 0°C to 70°C                         |

| Supply Voltage (AV <sub>CC</sub> and DV <sub>CC</sub> | ) 4.5V <sub>DC</sub> to 6.0V <sub>DC</sub> |

| Negative Supply Voltage (VSS)                         | $-4.5V_{DC}$ to $-6.0V_{DC}$               |

Micro Linear

# **ELECTRICAL CHARACTERISTICS**

The following specifications apply for AV $_{CC}$  = DV $_{CC}$  = +5V  $\pm$  5%, V $_{SS}$  = -5V  $\pm$  5%, AGND = DGND = COM = CHX- = 0V, T $_{A}$  = T $_{MIN}$  to T $_{MAX}$  unless otherwise specified. C $_{L}$  = 100pF for D0-D7, C $_{L}$  = 50pF for INT, DBR, and SYNC.

| SYMBOL  | PARAMETER                                                                                                                                                          | NOTES       | CONDITIONS                                                                          | MIN                    | TYP<br>NOTE 3          | MAX                     | UNITS                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------|------------------------|------------------------|-------------------------|--------------------------------------------|

| Convert | er Characteristics                                                                                                                                                 |             | h                                                                                   | 1                      | l                      | ı                       | <b>L</b>                                   |

|         | Linearity Error<br>ML2200BCP, ML2208BCP<br>ML2200CCP, ML2208CCP<br>ML2200DCP, ML2208DCP                                                                            | 4           | $f_{CCLK} = 0.1 \le 7MHz$<br>$f_{CCLK} = 0.1 \le 7MHz$<br>$f_{CCLK} = 0.1 \le 5MHz$ |                        |                        | ±3/4<br>±1<br>±1        | LSB<br>LSB<br>LSB                          |

|         | Unadjusted Zero Error<br>ML2200BCP, ML2208BCP<br>ML2200CCP, ML2208CCP<br>ML2200DCP, ML2208DCP                                                                      | 4           |                                                                                     |                        |                        | ±3/4<br>±2<br>±2        | LSB<br>LSB<br>LSB                          |

|         | Unadjusted Positive and<br>Negative Full Scale Error                                                                                                               | 5           |                                                                                     |                        |                        | ±4                      | LSB                                        |

|         | Zero Error Temperature Coefficient                                                                                                                                 |             |                                                                                     |                        | 0.5                    |                         | ppm/°C                                     |

|         | Gain Temperature Coefficient                                                                                                                                       |             | External Reference                                                                  |                        | 3                      |                         | ppm/°C                                     |

|         | Common-Mode Rejection                                                                                                                                              | 13          |                                                                                     |                        | 80                     |                         | dB                                         |

|         | Analog Input Range                                                                                                                                                 | 5           | All Analog Inputs                                                                   | V <sub>SS</sub> – 0.05 |                        | AV <sub>CC</sub> + 0.05 | ٧                                          |

|         | External Source Resistance for Analog Inputs                                                                                                                       | 5           | Channel = Analog Input<br>Channel = Voltage Reference                               |                        |                        | 2<br>0.5                | kΩ<br>kΩ                                   |

|         | Differential Analog Input Range                                                                                                                                    |             | CHX referred to COM<br>for ML2208<br>CHX+ referred to CHX– for<br>ML2200            | -V <sub>REF</sub>      |                        | +V <sub>REF</sub>       | V                                          |

|         | Off Channel Leakage Current                                                                                                                                        | 5, 6        | On Chan = 2.5V,<br>Off Chan = -2.5V<br>On Chan =-2.5V<br>Off Chan = 2.5V            | -100                   |                        | +100                    | nA                                         |

|         | On Channel Leakage Current                                                                                                                                         | 5, 6        | On Chan = -2.5V,<br>Off Chan = 2.5V<br>On Chan = 2.5V<br>Off Chan =2.5V             | -100                   |                        | +100                    | nA                                         |

|         | Gain Error                                                                                                                                                         | 1           | Gain = 2, 4, or 8                                                                   |                        | 0.03                   |                         | %                                          |

| Voltage | Reference and V <sub>TEMP</sub> Characteristics                                                                                                                    |             |                                                                                     |                        |                        |                         |                                            |

|         | V <sub>REF</sub> Absolute Value                                                                                                                                    | 4           | Referred to AGND                                                                    | 2.45                   |                        | 2.55                    | V                                          |

|         | V <sub>REF</sub> Output Pin Output Resistance Minimum Load Resistance Maximum Load Resistance Temperature Coefficient Line Regulation Load Regulation Output Noise | 5<br>5<br>5 | 4.75 ≤ AV <sub>CC</sub> ≤ 5.25<br>-4.75 ≥ V <sub>SS</sub> ≥ -5.25<br>1μA – 2.5mA    | 1                      | 50<br>1<br>1<br>1<br>1 | 300<br>50               | mΩ<br>kΩ<br>pF<br>ppm/°C<br>mV<br>mV<br>mV |

|         | V <sub>TEMP</sub> Output Pin<br>Absolute Value @ 25°C<br>Volts per °C                                                                                              |             |                                                                                     |                        | AV <sub>CC</sub> – 1.5 |                         | mV/°C                                      |

# Micro Linear

2-7

■ 6093418 0003178 541 ■

# ML2200, ML2208

# **ELECTRICAL CHARACTERISTICS** (Continued)

The following specifications apply for AV<sub>CC</sub> = DV<sub>CC</sub> =  $\pm$ 5V  $\pm$ 5%, V<sub>SS</sub> =  $\pm$ 5V, AGND = DGND = COM = CHX $\pm$ 5V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise specified. C<sub>L</sub> = 100pF for D0–D7, C<sub>L</sub> = 50pF for INT, DBR, and SYNC.

| SYMBOL           | PARAMETER                                                                                                                                               | NOTES        | COND                                                                                                                                                                            | DITIONS                                  | MIN          | TYP<br>NOTE 3        | MAX          | UNITS                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------|----------------------|--------------|----------------------|

| DC Cha           | racteristics                                                                                                                                            |              |                                                                                                                                                                                 |                                          |              |                      |              |                      |

|                  | Power Supply Current AI <sub>CC</sub> , Analog AV <sub>CC</sub> DI <sub>CC</sub> , Digital DV <sub>CC</sub> I <sub>SS</sub> , V <sub>SS</sub>           | 4<br>12<br>4 | $\overline{RD} = \overline{CS} = V_{IH}$                                                                                                                                        |                                          |              | 30<br>10<br>18       | 50<br>30     | mA<br>μA<br>mA       |

| I <sub>CC</sub>  | Standby Current Al <sub>CC</sub> + Dl <sub>CC</sub> Standby Current V <sub>CCPD</sub> Minimum AV <sub>CC</sub> and DV <sub>CC</sub> for power-down data | 4, 9         | $P_{DN}$ pin = GN<br>$P_{DN}$ pin = GN<br>$V_{SS}$ = -5.25 to                                                                                                                   | D                                        | 2            | 10<br>10             | 1000<br>1000 | μΑ<br>μΑ<br>V        |

|                  | retention  Power Supply Rejection  AV <sub>CC</sub> /DV <sub>CC</sub> V <sub>SS</sub>                                                                   |              | DC<br>DC to 25kHz,<br>DC<br>DC to 25kHz,                                                                                                                                        | 200mV <sub>P-P</sub>                     |              | 80<br>50<br>80<br>50 |              | dB<br>dB<br>dB<br>dB |

| VIL              | Input Low Voltage (except CLK, t <sub>CLK</sub> )                                                                                                       | 4            |                                                                                                                                                                                 |                                          |              |                      | 0.8          | V                    |

| V <sub>IL1</sub> | Input Low Voltage (CLK, t <sub>CLK</sub> )                                                                                                              | 4            |                                                                                                                                                                                 |                                          |              |                      | 0.8          | V                    |

| V <sub>lH</sub>  | Input High Voltage (except CLK, t <sub>CLK</sub> )                                                                                                      | 4            |                                                                                                                                                                                 |                                          | 2.0          |                      |              | V                    |

| V <sub>IH1</sub> | Input High Voltage (CLK, t <sub>CLK</sub> )                                                                                                             | 4            |                                                                                                                                                                                 |                                          | 3.5          |                      |              | V                    |

| V <sub>OL</sub>  | Output Low Voltage                                                                                                                                      | 4            | I <sub>OL</sub> = 2.0mA                                                                                                                                                         |                                          |              |                      | 0.45         | ν                    |

| VoH              | Output High Voltage                                                                                                                                     | 5            | I <sub>OH</sub> = -1 mA                                                                                                                                                         |                                          | 4.0          |                      |              | V                    |

| ĺι               | Input Leakage Current<br>(except CLK and RESET)                                                                                                         | 4            | GND < V <sub>IN</sub> < V <sub>CC</sub>                                                                                                                                         |                                          |              |                      | ±10          | μА                   |

| l <sub>L1</sub>  | Input Leakage Current (CLK)                                                                                                                             | 4            | GND < V <sub>IN</sub> <                                                                                                                                                         | V <sub>CC</sub>                          |              |                      | ±200         | μА                   |

| ILO              | Output Leakage Current (D0 - D7)                                                                                                                        | 4            | $\overline{RD} = \overline{CS} = V_{l+}$                                                                                                                                        |                                          |              |                      | ±10          | μА                   |

| I <sub>RST</sub> | RESET Pin Source Current                                                                                                                                | 4            | RESET = 0V                                                                                                                                                                      |                                          | 15           | 50                   | 100          | μА                   |

| Cı               | Input Capacitance (All Digital Inputs)                                                                                                                  |              |                                                                                                                                                                                 |                                          |              | 10                   |              | pF                   |

| Co               | Output Capacitance (All<br>Outputs and D0 – D7)                                                                                                         |              |                                                                                                                                                                                 |                                          |              | 20                   |              | pF                   |

| AC Elec          | ctrical Characteristics (Note 8)                                                                                                                        |              |                                                                                                                                                                                 |                                          |              |                      |              |                      |

| tc               | Conversion Time                                                                                                                                         | 4, 9         | CLK Mode = 0                                                                                                                                                                    | $f_{CLK} = 7.0MHz$<br>$f_{CLK} = 5.0MHz$ | 31.5<br>44.0 |                      |              | μs<br>μs             |

|                  | Sample and Hold Acquisition                                                                                                                             | 4, 9         | CLK Mode = 0                                                                                                                                                                    | $f_{CLK} = 7.0MHz$<br>$f_{CLK} = 5.0MHz$ |              |                      | 2.3<br>3.2   | μs<br>μs             |

| SNR              | Signal-to-Noise Ratio                                                                                                                                   |              | V = 10kHz, 2.5V Sine.<br>f <sub>CLK</sub> = 7MHz (f <sub>SAMPLING</sub> =<br>31.8kHz). Noise is sum of all<br>nonfundamental components<br>up to 1/2 of f <sub>SAMPLING</sub> . |                                          |              | 73                   |              | dB                   |

| THD              | Total Harmonic Distortion                                                                                                                               |              | V = 10kHz, 2.5V Sine. f <sub>CLK</sub> = 7MHz (f <sub>SAMPLING</sub> = 31.8kHz). THD is sum of 2, 3, 4, 5 harmonics relative to fundamental.                                    |                                          |              | <b>-75</b>           |              | dB                   |

2-8

6093418 0003179 488 📟

# **ELECTRICAL CHARACTERISTICS** (Continued)

The following specifications apply for AV<sub>CC</sub> = DV<sub>CC</sub> =  $\pm$ 5V  $\pm$ 5%, V<sub>SS</sub> =  $\pm$ 5V, AGND = DGND = COM = CHX- = 0V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise specified. C<sub>L</sub> = 100pF for D0–D7, C<sub>L</sub> = 50pF for INT, DBR, and SYNC.

| SYMBOL             | PARAMETER                                        | NOTES | CONDITIONS                                                                                                                                                                                                                                                                                                                        | MIN | TYP<br>NOTE 3 | MÀX               | UNITS                       |

|--------------------|--------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-------------------|-----------------------------|

| AC Elec            | trical Characteristics (Note 8) (Continue        | ed)   |                                                                                                                                                                                                                                                                                                                                   |     |               |                   |                             |

| IMD                | Intermodulation Distortion                       |       | $\begin{split} &V_{IN} = f_A + f_B. \; f_A = 9 k Hz \\ &1.25 V \; sine. \; f_B = 10 k Hz, \; 1.25 \\ &sine. \; f_{CLK} = 7 M Hz \\ &(f_{SAMPLING} = 31.8 k Hz). \\ &IMD \; is \; (f_A + f_B), \; (f_A - f_B), \\ &(2f_A - f_B), \; (2f_A + f_B), \; (f_A + 2f_B), \\ &(f_A - 2f_B) \; relative \; to \; fundamental. \end{split}$ |     | <b>-75</b>    |                   | dВ                          |

| FR                 | Frequency Response                               |       | $V_{IN} = 0$ to 10kHz, 2.5V sine relative to 1kHz                                                                                                                                                                                                                                                                                 |     | 0.01          | ·                 | dB                          |

| f <sub>CLK</sub>   | CLK Frequency                                    | 4     | (No crystal)                                                                                                                                                                                                                                                                                                                      | 0.1 |               | 7                 | MHz                         |

| f <sub>CLKX</sub>  | CLK Frequency                                    | 4     | (Crystal)                                                                                                                                                                                                                                                                                                                         | 3   |               | 7                 | MHz                         |

| f <sub>CLKI</sub>  | Internal CLK Frequency                           |       |                                                                                                                                                                                                                                                                                                                                   |     | 1/2           |                   | f <sub>CLK</sub> or         |

| f <sub>CLKT</sub>  | CLK Frequency (t <sub>CLK</sub> only)            | 4     |                                                                                                                                                                                                                                                                                                                                   |     |               | f <sub>CLKI</sub> | MHz                         |

| f <sub>CLKW</sub>  | Minimum Clock High/Low Width (CLK)               | 5     |                                                                                                                                                                                                                                                                                                                                   | 50  |               |                   | ns                          |

| fCLKWT             | Minimum Clock High/Low Width (t <sub>CLK</sub> ) | 5     |                                                                                                                                                                                                                                                                                                                                   | 75  |               |                   | ns                          |

| t <sub>RF</sub>    | Maximum Rise/Fall Times, All Inputs              | 5     |                                                                                                                                                                                                                                                                                                                                   |     |               | 25                | ns                          |

| t <sub>RESET</sub> | Minimum Reset Active Time                        | 4, 10 |                                                                                                                                                                                                                                                                                                                                   | 10  |               |                   | f <sub>CLK</sub><br>Periods |

| t <sub>PDN</sub>   | Power-Up Time                                    |       | Time After P <sub>DN</sub> = V <sub>IH</sub>                                                                                                                                                                                                                                                                                      |     | 1             |                   | ms                          |

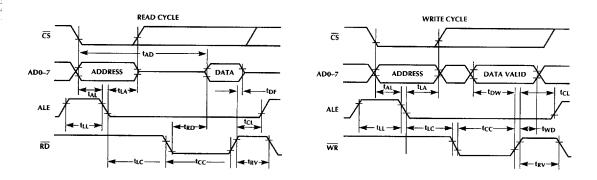

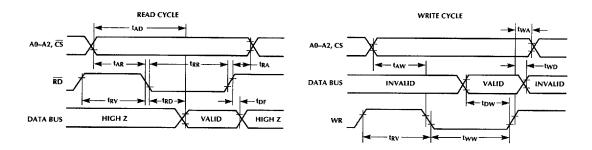

| Non-Mu             | ltiplexed Data Bus Timing                        |       |                                                                                                                                                                                                                                                                                                                                   |     |               |                   | - 1                         |

| t <sub>AL</sub>    | Address to ALE Setup Time                        | 4     |                                                                                                                                                                                                                                                                                                                                   | 20  |               |                   | ns                          |

| tLA                | Address Hold Time After ALE                      | 4     |                                                                                                                                                                                                                                                                                                                                   | 20  |               |                   | ns                          |

| t <sub>LC</sub>    | Latch to RD or WR Control                        | 4     |                                                                                                                                                                                                                                                                                                                                   | 20  |               |                   | ns                          |

| t <sub>RD</sub>    | Valid Data Delay from Read                       | 4     |                                                                                                                                                                                                                                                                                                                                   |     |               | 150               | ns                          |

| t <sub>AD</sub>    | Address Stable to Valid Data                     | 5     |                                                                                                                                                                                                                                                                                                                                   | 150 |               |                   | ns                          |

| tLL                | ALE Width                                        | 4     |                                                                                                                                                                                                                                                                                                                                   | 80  |               |                   | ns                          |

| t <sub>DF</sub>    | Data Bus Float After Read                        | 4     |                                                                                                                                                                                                                                                                                                                                   | 10  |               | 50                | ns                          |

| t <sub>CL</sub>    | Read or Write Control to ALE                     | 4     |                                                                                                                                                                                                                                                                                                                                   | 20  |               |                   | ns                          |

| tcc                | Read or Write Control Width                      | 4     |                                                                                                                                                                                                                                                                                                                                   | 150 |               |                   | ns                          |

| t <sub>DW</sub>    | Data Setup Time for Write                        | 4     |                                                                                                                                                                                                                                                                                                                                   | 100 |               |                   | ns                          |

| t <sub>WD</sub>    | Data Hold Time for Write                         | 4     |                                                                                                                                                                                                                                                                                                                                   | 0   |               |                   | ns                          |

| t <sub>RV</sub>    | Recovery Time Between<br>Two Reads or Writes     | 4     |                                                                                                                                                                                                                                                                                                                                   | 250 |               |                   | ns                          |

| t <sub>AD</sub>    | Address Stable to Valid Data                     | 5     |                                                                                                                                                                                                                                                                                                                                   | 150 |               |                   | ns                          |

| t <sub>AR</sub>    | Address Stable Before Read                       | 4     |                                                                                                                                                                                                                                                                                                                                   | 0   |               |                   | ns                          |

| t <sub>RA</sub>    | Address Hold Time for Read                       | 4     |                                                                                                                                                                                                                                                                                                                                   | 0   |               |                   | ns                          |

| t <sub>RR</sub>    | Read Pulse Width                                 | 4     |                                                                                                                                                                                                                                                                                                                                   | 150 |               |                   | ns                          |

| t <sub>RD</sub>    | Data Delay from Read                             | 4     |                                                                                                                                                                                                                                                                                                                                   |     |               | 150               | ns                          |

| t <sub>DF</sub>    | Read to Data Float                               | 4     |                                                                                                                                                                                                                                                                                                                                   | 10  |               | 50                | ns                          |

2-9

■ TT1 O003180 1TT ■

# **ELECTRICAL CHARACTERISTICS** (Continued)

The following specifications apply for AV<sub>CC</sub> = DV<sub>CC</sub> =  $\pm 5V \pm 5\%$ , V<sub>SS</sub> =  $\pm 5V \pm 5\%$ , AGND = DGND = CHX- = 0V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise specified. C<sub>L</sub> = 100pF for D0-D7, C<sub>L</sub> = 50pF for INT, DBR, and SYNC.

| SYMBOL             | PARAMETER                                       | NOTES | CONDITIONS         | MIN | TYP<br>NOTE 3 | MAX | UNITS             |

|--------------------|-------------------------------------------------|-------|--------------------|-----|---------------|-----|-------------------|

| Non-Mı             | Iltiplexed Data Bus Timing                      |       |                    |     |               |     |                   |

| t <sub>RV</sub>    | Recovery Time Between<br>Two Reads or Writes    | 4     |                    | 250 |               |     | ns                |

| t <sub>AW</sub>    | Address Stable Before Write                     | 4     |                    | 0   |               |     | ns                |

| twa                | Address Hold Time for Write                     | 4     |                    | 0   |               |     | ns                |

| tww                | Write Pulse Width                               | 4     |                    | 150 |               |     | ns                |

| t <sub>DW</sub>    | Data Setup Time for Write                       | 4     |                    | 100 |               |     | ns                |

| t <sub>WD</sub>    | Data Hold Time for Write                        | 4     |                    | 0   |               |     | ns                |

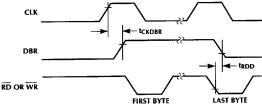

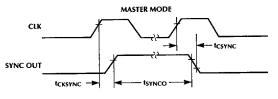

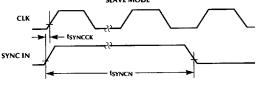

| DMA In             | terrupt and SYNC Timings                        | ,     |                    |     |               |     |                   |

| t <sub>CKDBR</sub> | Clock to DBR Assert                             | 11, 4 | DMA                |     | 120           | 190 | ns                |

| t <sub>RDD</sub>   | Read to DBR Negation on Last Byte               | 4     |                    |     | 110           | 170 | ns                |

| †CKDBR             | Clock to DBR or t <sub>CKINT</sub> , INT Assert | 11, 4 | Non-DMA            |     | 100           | 180 | ns                |

| twrdbr             | Write to DBR or tWRINT INT Negation             | 11, 4 |                    |     | 70            | 120 | ns                |

| tCKSYNC            | Clock to SYNC Delay                             | 11, 4 | Master Mode        |     | 150           | 220 | ns                |

| tsynch             | SYNC Input Width                                | 5     |                    | 3   |               |     | f <sub>CLKI</sub> |

| tsyncck            | SYNC to Clock Setup                             | 4     | Slave: Mode 4 Only | 50  |               |     | ns                |

| tsynco             | Minimum SYNC Output Width                       | 4     |                    | 4   |               | 4   | f <sub>CLKI</sub> |

- Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with respect to ground.

- Note 2: 0°C to +70°C operating temperature range devices are 100% tested with temperature limits guaranteed by 100% testing, sampling, or by correlation with worst-case test conditions.

- Note 3: Typicals are parametric norm at 25°C.

- Note 4: Parameter guaranteed and 100% production tested.

- Note 5: Parameter guaranteed. Parameters not 100% tested are not in outgoing quality level calculation.

- Note 6: Leakage current is measured with the clock not switching.

- Note 7: Power supply rejection is the ratio of the change in zero error to the change in power supply voltage.

- Note 8: All parameters measured from 0.8V to 2.0V.

- Note 9: Power-down current is with power-down pin at GND potential only. Any other level will dissipate more power. Other digital input pins may float but cannot be above VDD or below GND.

- Note 10: RESET should be held active for at least 10 internal clocks after power supplies have stabilized to within 5% of 5V.

- Note 11: Since the internal master lock is the input clock divided by 2, this number can be either the maximum listed or the maximum listed plus 1/2 the input clock period.

- Note 12: When RD = CS =  $V_{IL}$ , the current into the DV<sub>CC</sub> pin depends on the data bus pins D0 D7.

- Note 12: When  $RD = CS = V_{IC}$  the Current line the  $DV_{CC}$  pin depends on the data out pins BO = DV. Note 13: Common-Mode rejection is the ratio of the change in zero error to the change in common-mode input voltage.

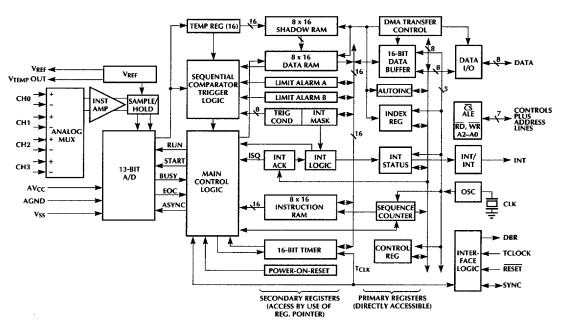

# **TIMING DIAGRAMS**

Figure 2. Multiplexed Bus.

Figure 3. Non-Multiplexed Bus.

2-11

■ 6093418 0003182 T72 **■**

#### TIMING DIAGRAMS (Continued)

There are 2\*n Read Operations where n is the number of words to be transferred. DBR is set and cleared by internal circuitry.

DMA bit in the control register must be set for this operation.

DBR OR INT

twrdbr OR twrint

wr

Figure 4. DMA Mode.

Figure 5. DBR and INT (Non-DMA Mode).

Figure 6. SYNC

## 1.0 FUNCTIONAL DESCRIPTION

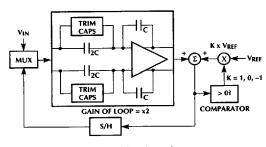

#### 1.1 ALGORITHMIC A/D CONVERTER

Micro Linear's algorithmic converter uses a successive approximation technique. Most of today's successive approximation converters use a DAC to feed back the approximated signal, however this technique requires more circuitry than algorithmic converters. In addition the values of all of the resistors or capacitors in the DAC must be matched to within the accuracy of the converter. This is difficult to do in silicon beyond 10 bits unless trimming is used. An algorithmic converter uses less circuitry and is more easily trimmed. Micro Linear's algorithmic converter is implemented using a 2x amplifier, a sample/hold amp, and a comparator as shown in Figure 7.

Figure 7. Self Calibrating A/D Converter.

The input sample is first multiplied by two then compared to the reference voltage. If the 2x input voltage is greater than the reference, the MSB is a 1 and the reference voltage is subtracted from the 2x input voltage. The remainder is stored in the sample-and-hold. If the 2x input voltage is less than the reference, the MSB is a 0 and the 2x input voltage is stored in the sample-and-hold. This process repeats again, however now the sample-and-hold voltage is multiplied by 2.

#### Self-Calibration

In order to maintain integral and differential linearity to the 1/2 LSB level in an algorithmic converter, two critical parameters need to be controlled, loop offsets and the gain of the loop. Loop offsets are automatically nulled before each conversion using auto-zeroing circuitry on both the sampling amp and the 2x amp. The gain of the loop is adjusted using self-calibration .

Self-calibrating the algorithmic converter, once the offsets have been nulled, is performed by measuring the 2x gain of the loop and adjusting it. The gain can be measured by converting the reference voltage as the input as well as the reference (V<sub>REF</sub>/N<sub>REF</sub>), and examining the output code. Converting V<sub>REF</sub> should yield plus full-scale, since V<sub>REF</sub>/V<sub>REF</sub> should equal 1. If the gain of the loop is slightly less than 2, the resulting LSB of the conversion will be "0". If the magnitude bits of the resulting conversion are all "1s",

2-12

Micro Linear

6093418 0003183 909 **=**

the gain may be too great, therefore the gain is reduced to the point where the threshold of the LSB is reached.

Adjustment of the 2x gain is done with the binary weighted trim capacitor arrays connected to each of the 2C input capacitors. A small value of capacitance is either added to or subtracted from the 2C input caps until the gain of the loop is within 13-bit accuracy of 2.

#### 1.2 MULTIPLEXER INPUT

The input voltage is ±2.5V relative to COM of the ML2208 or a CH- of the ML2200. The input voltages under normal operation must not exceed supply voltages by 0.05V. Each channel is selected by the programmable sequencer.

## 1.3 INTERNAL VOLTAGE REFERENCE AND V<sub>TEMP</sub>

The internal bandgap voltage reference with a temperature coefficient of 50 ppm /°C has an external use current of 2.5mA.

The voltage reference  $V_{\text{TEMP}}$  output is directly proportional to the chip temperature.

#### 1.4 CONVERSION TIMES

The following table lists the conversion times which include the sample-and-hold acquisition time. For a CALRD and CALWR no A/D conversion actually takes place.

| Operation   | Number of<br>Internal Clocks* |

|-------------|-------------------------------|

| 8-bit A/ D  | 80                            |

| 13-bit A∕ D | 110                           |

| CALWR       | 52                            |

| CALRD       | 80                            |

<sup>\*</sup>Internal clock is the external clock divided by two.

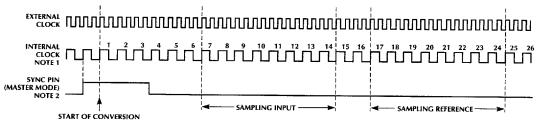

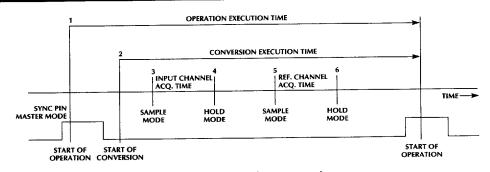

#### 1.5 SAMPLE-AND-HOLD TIMING

Figure 8 shows the internal timing for the sample-andhold circuitry. The relationship between the "Start of Conversion" and the input channel going into sample mode is fixed at 6 internal clocks, regardless of the Start Mode. Six internal clocks after the Start of Conversion, the Sample-and-Hold is switched into the sample mode, placing two 9pF capacitors in parallel with the input pins; one on CH+ and one on CH- for the ML2200, and CH and COM for the ML2208. The sample switch is kept in the sample mode for 8 internal clocks (2.3µs at a 7MHz external clock), then placed in the hold mode. During the next 2 internal clocks the charge on the sample-and-hold is transferred into the A/D, after which the V<sub>REF</sub> pin is sampled for 8 internal clocks.

Figure 8 also illustrates the timing of the SYNC pin in Master Mode during a conversion. SYNC is activated one internal clock cycle before the Start of Conversion and lasts for four internal clocks.

# 1.6 ANALOG INPUTS DIFFERENTIAL INPUTS AND COMMON-MODE REJECTION

The differential inputs of the ML2200 eliminate the effects of common-mode input noise (60Hz, for example), as CH+ and CH- are sampled at the same time.

#### Noise

The leads to the analog inputs should be kept as short as possible to minimize output noise. Noise as well as digital clocks can couple into the inputs and cause errors. Input filters can be used to reduce the effects of these sources.

#### **Power Supply Decoupling**

Low inductance tantalum capacitors of  $1\mu F$  or greater and  $0.01\mu F$  disc ceramic capacitors are recommended for bypassing  $AV_{CC}$  as well as  $V_{SS}$  to AGND. These capacitors should be placed close to the  $AV_{CC}$  and  $V_{SS}$  pins.

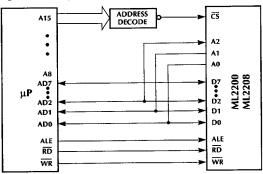

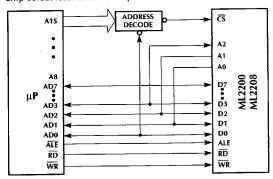

# 2.0 μP HARDWARE INTERFACE

The microprocessor interface is a byte-oriented structure which occupies eight memory or I/O locations in the microprocessor's address space. Each register is readable and writable via the chip select, read and write pins, three address lines, and 8-bit data bus.

Note 1: External clock in phase with internal clock using RESET.

Note 2: Immediate execute mode where start of conversion and start of operation occur at the same time.

Figure 8. Sample-and-Hold Timing.

Micro Linear

2-13

6093418 0003184 845 🖿

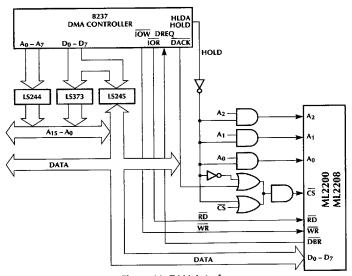

Interfaces are shown for multiplexed address data bus in Figure 9 and Figure 10. When non-multiplexed interfaces

Figure 9. 8-Bit Multiplexed Bus Interface.

#### 2.1 INTERRUPTS

The ML2200 and ML2208 provide two interrupt pins, one for control/status interrupts (INT), and one for data interrupts (DBR). The standard INT pin is maskable via an interrupt mask register while the DBR pin is always enabled to signify that data is available. DBR can be mapped into the INT pin if only one interrupt pin is desired.

The interrupt pin (INT) can be programmed, via the Interrupt Bit Mask register, to be active high, or active low. When programmed for active high, it is driven in both directions. When INT is programmed for active low, it is an open drain output, therefore an external pull-up resistor of 2.5  $k\Omega$  or more should be used. The DAP's Status register can be read to determine whether its interrupt is active or not.

are used, ALE can be tied high. All internal address and chip select latches are transparent.

Figure 10. 16-Bit Multiplexed Bus Interface.

#### 2.2 DMA

The separate DBR pin can also serve as a DMA request signal when DMA operation is enabled in the Control register. DBR goes active high when the data buffer is full and ready to be read. DBR remains high until the last byte in the data buffer has been read. This allows back-to-back DMA cycles or single cycle transfers depending on how the DMA controller is programmed. The data for the DMA cycle is transferred over the 8-bit data bus at address 0 (A0 – A2 =0). The ML2200 or ML2208 automatically places both high and low bytes of the 16-bit wide data buffer at address 0 or 1 for the DMA controller to read. The LOBYT bit in the Control register specifies whether the high or low byte is placed on the bus first. Figure 11 shows a block diagram interfacing to the 8237 DMA controller.

Figure 11. DMA Interface.

2-14

Micro Linear

6093418 0003185 781

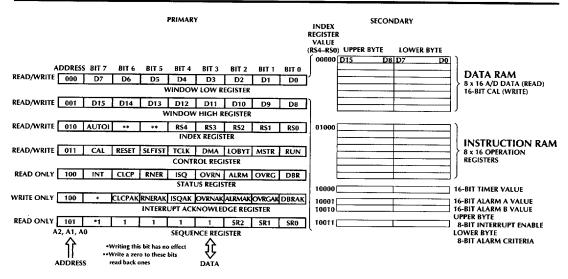

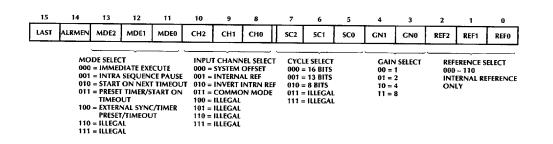

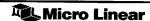

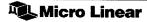

# 3.0 REGISTER DEFINITIONS

These data acquisition peripherals contain six directly addressable 8-bit registers, and twenty indirectly addressable 16-bit registers. Figure 12 illustrates the register architecture while Figures 13, 14 & 15 illustrate the bit maps and addresses. The first three primary registers (Window Low,

Window High, and Index) are used to access the 20 secondary registers. Window Low and Window High provide read /write access to the low and high bytes of the secondary register pointed to by Index.

Figure 12. Register Architecture.

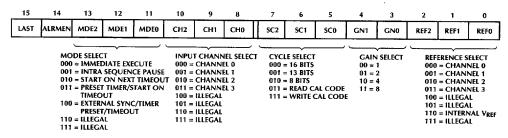

Figure 13. ML2200 Bit Map of Instruction RAM.

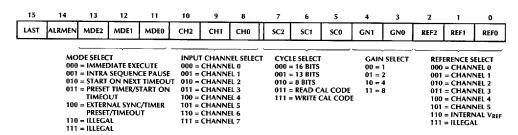

Figure 14. ML2208 Bit Map of Instruction RAM.

2 - 15

6093418 0003186 618 🖿

| 15          | 14      | 13     | 12    | 11     | 10     | 9      | 8     | 7 | 6 | 5 | 4    | 3    | 2      | 1                                                 | 0                   |

|-------------|---------|--------|-------|--------|--------|--------|-------|---|---|---|------|------|--------|---------------------------------------------------|---------------------|

| INTL        | CLC PIE | RNERIE | ISQIE | OVRNIE | ALRMIE | OVRGIE | DBRIE |   |   |   | EN B | EN A | AND/OR | >B/ <b< th=""><th>&gt;A/<a< th=""></a<></th></b<> | >A/ <a< th=""></a<> |

| <del></del> |         |        |       |        |        |        |       |   |   |   |      |      |        |                                                   |                     |

INTERRUPT ENABLE REGISTER

ALARM CRITERIA REGISTER

Figure 15. Interrupt Enable and Alarm Criteria Registers.

| 3.1 Prir | nary R | egister | 3      |       |       |    | READ/<br>WRITE |

|----------|--------|---------|--------|-------|-------|----|----------------|

| D7       | D6     | D5      | D4     | D3    | D2    | D1 | DO             |

|          |        | Win     | dow Lo | w Reg | ister |    | READ/<br>WRITE |

| D15      | D14    | D13     | D12    | D11   | D10   | D9 | D8             |

Window High Register

## Window Registers—Registers 0 and 1

These registers form a two-byte window into the secondary registers. Window Low is the low byte of the secondary 16-bit word, and Window High is the high byte. Any one of the 20 words in the secondary register set can be accessed by first setting a 5-bit address in the Index register, then reading from or writing to the Window registers. Sequential access of the secondary registers is also available without writing to the Index register via the AUTOI bit in the Index register.

| Index Register — Register 2 |     |     |     |     |     |  |  |  |  |  |

|-----------------------------|-----|-----|-----|-----|-----|--|--|--|--|--|

| AUTOI                       | RS4 | RS3 | RS2 | RS1 | RSO |  |  |  |  |  |

| Index Register              |     |     |     |     |     |  |  |  |  |  |

**RSX = Secondary Register Address (Bits 0 to 4):** The lower five bits of this register (RSO – RS4) define the location within the secondary register set that the window registers are positioned at.

**Bits 5 and 6:** Undefined. Writing to these bits have no effect, however a zero should be written; always read as ones.

AUTOI = autoincrement (Bit 7): Setting AUTOI signifies that the lower five addressing bits in the Index register are automatically incremented after either the Window Low or Window High register is accessed. Whether the autoincrement occurs when accessing Window Low or Window High register, is based on the LOBYT bit in the Control register.

Interrupt Operation Caution!!! — Using the autoincrement feature with interrupt driven software deserves special attention. A problem can arise when an interrupt service routine accessing the secondary registers, interrupts another routine accessing secondary registers. This problem can be avoided one of two ways: disable the interrupt in the main routine while accessing secondary registers, or reload the index register to its entry value when exiting the interrupt routine.

Note: The Index register is automatically cleared only under two conditions, one is a RESET, the other is when mode is used. This register is reset to 0 in DMA mode just prior to the DMA request (DBR going active). DMA mode uses the index register for operation, so the index register should never be written to when RUN and DMA are set.

| Control Register — Register 3            |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| CAL RESET SLFTST tCLK DMA LOBYT MSTR RUN |  |  |  |  |  |  |  |  |  |  |

| Control Register                         |  |  |  |  |  |  |  |  |  |  |

RUN (Bit 0): Setting this bit to a one will cause the chip to start executing the operations defined in the Instruction RAM, beginning with location 0. This is referred to as the Run mode. Clearing this bit will place the ML2200 in the Halt mode. The run bit is initially cleared on power up or after a hardware or software reset. In order to properly start the chip operation, the RUN bit should be set after setting all other applicable bits in the control register. The act of halting the chip will always reset the sequence pointer to operation 0. Thus, the next time RUN is asserted, the chip starts from operation 0 again. Placing the chip in the Run or Halt mode has no effect on the Interrupt pins (INT and DBR), nor the status bits in the status register. It is recommended that secondary registers only be written to in the Halt mode. Writing to secondary registers in the Run mode will cause the RNER status bit to be set, indicating a run error. All of the status bits in the Status register should be acknowledged (cleared) before entering the Run mode.

MSTR = master (Bit 1): Indicates whether the SYNC pin will be an input or an output. If set the chip will enter the master mode of operation and the SYNC pin will become an output pin which puts out a sync pulse at the beginning of each operation. This serves as a signal for other slave chips that are used in a synchronous operating method. While in master mode, any operation requiring a sync input will not proceed, and the chip will "hang", waiting for a sync that will never come. The chip default is slave mode with the SYNC pin as an input.

LOBYT = low byte first (Bit 2): This bit is used to indicate which byte is accessed first in AUTOI or DMA operation. When this bit is set, the index register is incremented on the read or write of the Window High register. When this bit is clear, the index register is incremented on the read or write of the Window Low register. If DMA operation is specified, then setting this bit will make the low byte be output first, then the high byte, after which the index register is incremented. Conversely, clearing this bit will output the high byte first, then the low byte, then increment the index register. The default is low.

**DMA = DMA Mode (Bit 3):** When set enables DMA operation. DMA operation proceeds as follows:

The DMA bit must be set after defining all other registers (Instruction RAM, Alarm etc.) but prior to setting the RUN bit. The RUN bit is then set.

2-16

# Micro Linear

6093418 0003187 554 ■

- The sequence of operations in the Instruction RAM is executed.

- At the end of the sequence, the DBR pin goes true, requesting DMA service, and the Index register is automatically cleared, pointing to the first location of the data buffer.

- 4) Each read of either Window Low or Window High register outputs a byte from the data registers. The DMA controller can read Window Low register, or Window High register, or alternate between Window Low and Window High. The same data is placed in both Window Low and Window High registers, and updated in both of them when either one is read. The data is placed in the Window registers beginning with data word 0 and incrementing on up. The placement of the low byte/ high byte order is based on the LOBYT bit in the Control register. The number of bytes transmitted equals twice the number of operations defined, since the words are 16-bits going over an 8-bit bus. DBR remains asserted until all of the bytes have been transmitted. It is negated on the leading edge of the last byte read pulse. DBR acknowledge (setting the DBRAK bit in the Status register) is not required when transferring bytes via DMA.

The AUTOI bit does not have to be set when in the DMA mode. Setting the DMA bit forces the Index register to be auto-incremented in the Run mode. However if AUTOI is not set, then when in Halt mode autoincrement will not be enabled. If the AUTOI bit and DMA bit are both set, the autoincrement will occur in both the Run mode and the Halt mode.

$t_{CLK}$  = enable external timer clock (Bit 4): When set, will divert the clock input for the internal sixteen bit timer to the  $t_{CLK}$  pin. When reset to 0, the timer runs at the internal chip clock frequency, which is  $^{1}/_{2}$  of that generated at the CLK pin.

**SLFTST** = **self test** (**Bit 5**): When set, the function of the input multiplexer is modified to enable self test operations. This bit also redefines the Instruction Word,

specifically the CHAN field of the instruction word (See Figure 16 for the redefinition of the Instruction Word when SLFTST = 1). With SLFTST set the CHAN bits now specify which of four self tests is to be performed as shown below.

| Instruction<br>Word<br>CHAN Field | Function       | Description                                                                                                            |

|-----------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------|

| 000                               | System Offset  | Inputs shorted together and shorted to ground                                                                          |

| 001                               | Internal       | Convert internal V <sub>REF</sub> ,                                                                                    |

|                                   | Reference      | plus side tied to<br>V <sub>REF</sub> , minus side<br>tied to AGND                                                     |

| 010                               | Minus Internal | Convert internal<br>V <sub>REF</sub> , Reference<br>minus side tied to<br>V <sub>REF</sub> , plus side<br>tied to AGND |

| 011                               | Common Mode    | Both inputs of the converter are tied to V <sub>REF</sub>                                                              |

| 100-111                           | Illegal        |                                                                                                                        |

These self-test results are useful for user confidence at power on. The default on reset is 0, normal mode of operation.

**RESET = soft reset (Bit 6):** Is a software reset of the chip. This bit does not have to be cleared once set. The microprocessor should read this bit back to determine if the reset operation has completed, especially if a slow clock rate is being used. It takes at least 4 internal clocks for the reset bit to clear. Microprocessor communication with the chip should be held off until this bit is read back as cleared. When issuing a hardware reset, communication with the chip should be held off until the RESET pin goes inactive. The chip will be in the Halt mode (RUN bit cleared) after a reset. See RESET/Power-On Conditions (Section 4.2) for chip register conditions after a reset.

Figure 16. Bit Map of Instruction Word When SLFTST = 1.

2 - 17

**■** 6093418 0003188 490 |

CAL = calibration start (Bit 7): When set, a self-calibration of the A/D converter will begin. Reading the CAL bit indicates whether the chip has been calibrated since the last reset or power-on condition. If CAL is a 1, then a calibration of the A/D converter has been performed since the last reset or power-up. When setting CAL, the user should not write a 0 back to clear it. Writing a 0 to the CAL bit has no effect; this will not clear it if it was previously set. Attempting to set the RUN bit without this bit being set will result in a run error condition, in which the RNER status bit will be set, and an interrupt being generated if it was enabled in the mask register. The amount of time required for calibration is 8,260 internal clocks, or 16,520 external clocks. To determine when a calibration is complete, the microprocessor should enable the calibration complete interrupt (CLCPIE) in the interrupt mask register, and wait for the interrupt to occur. Interrupt servicing of the calibration complete interrupt is done in a normal manner, in which the interrupt is acknowledged by setting the CLCPAK bit in the interrupt acknowledge register. All I /O to the ML2200 should be avoided during calibration (i.e., 16,520 external clocks after the CAL bit is set), because accessing the chip during calibration could adversely affect the calibration. If an interrupt is not desired, the microprocessor can read the Status register to verify completion 16,520 external clocks after the CAL bit is set. When the CAL bit is set, all other bits in the Control register should be cleared. DO NOT set the CAL and RUN bits simultaneously.

Status Register - Register 4

READ ONLY

|     |      |      |     |      |      |      | ONLI |