Monolithic Digital IC

#### LB1896

### 3-phase Brushless Motor Driver for CD-ROM Spindle Drive Use

### Overview

The LB1896 is a 3-phase brushless motor driver IC that is ideal for driving CD-ROM spindle motors.

## **Functions and Features**

- 120 ° voltage linear technique

- V-type control voltage

- · Switchable control gain

- Control, noncontrol, acceleration/deceleration mode select pins built in.

- Start/Stop pin built in, Hall bias built in.

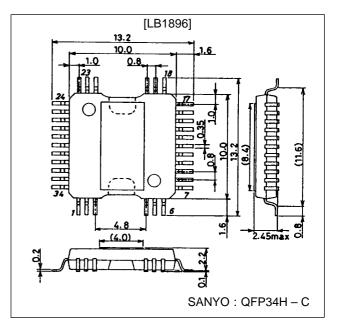

## **Package Dimensions**

unit : mm

#### 3219-QFP34H-C

## **Specifications**

#### Absolute Maximum Ratings at Ta = $25 \circ C$

| Parameter                   | Symbol                | Conditions     | Ratings     | Unit |

|-----------------------------|-----------------------|----------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> 1 max |                | 20          | V    |

|                             | V <sub>CC</sub> 2 max |                | 7.0         | ~    |

| Applied output voltage      | V <sub>OU, V, W</sub> |                | 20          | V    |

| Output current              | lout                  |                | 1.2         | А    |

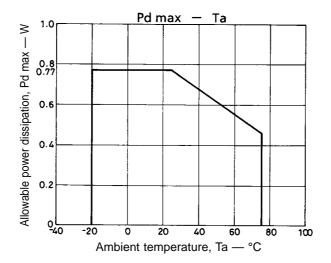

| Allowable power dissipation | Pd max                | Independent IC | 0.77        | W    |

| Operating temperature       | Topr                  |                | -20 to +75  | °C   |

| Storage temperature         | Tstg                  |                | -55 to +150 | °C   |

#### **Operating Conditions at Ta = 25 \circ C**

| Parameter                       | Symbol            | Conditions            | Ratings                     | Unit |

|---------------------------------|-------------------|-----------------------|-----------------------------|------|

| Supply voltage                  | V <sub>CC</sub> 1 |                       | 5 to 18                     | V    |

| Supply voltage                  | V <sub>CC</sub> 2 | $V_{CC}1 \ge V_{CC}2$ | 4.3 to 6.5                  | V    |

| V <sub>Cref</sub> input voltage | V <sub>Cref</sub> |                       | V <sub>CC</sub> 2/2 ±1.0    | V    |

| V <sub>NS</sub> input voltage   | V <sub>NS</sub>   |                       | 0 to V <sub>CC</sub> 2 –1.0 | V    |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

# Electrical Characteristics at Ta = 25 °C, $V_{\rm CC}1$ = 12 V, $V_{\rm CC}2$ = 5 V

| Parameter                                      | Symbol                  | Conditions                                                                                                     | min  | typ  | max  | Unit |

|------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply current 1                               | I <sub>CC</sub> 1       | $V_{C}$ = open, $V_{Cref}$ = open, $R_{L}$ = $\infty$ ,<br>$V_{S/S}$ = 5 V                                     |      | 17   | 30   | mA   |

| Supply current 2                               | I <sub>CC</sub> 2       | $V_{C}$ = open, $V_{Cref}$ = open                                                                              |      | 7.5  | 10.5 | mA   |

| Supply current 3                               | I <sub>CC</sub> 3       | $V_C$ = open, $V_{Cref}$ = open, $R_L$ = $\infty$ ,<br>$V_{S/S}$ = 0 V, (I <sub>CC</sub> of V <sub>CC</sub> 1) |      | 0.9  | 3    | mA   |

| [Drive block]                                  |                         |                                                                                                                |      |      |      |      |

| Output saturation voltage                      | V <sub>O(sat)</sub> 1   | I <sub>OUT</sub> = 0.4 A, sink + source                                                                        |      | 1.6  | 2.2  | V    |

| Ouput saturation voltage                       | V <sub>O(sat)</sub> 2   | I <sub>OUT</sub> = 0.8 A, sink + source                                                                        |      | 2.0  | 3.0  | V    |

| Output TRS sustaining voltage                  | V <sub>O(sus)</sub>     | I <sub>OUT</sub> = 20 mA                                                                                       | 20   |      |      | V    |

| Output static voltage                          | V <sub>OQ</sub>         | $V_{C}$ = 2.5 V, $V_{Cref}$ = 2.5 V                                                                            | 5.7  | 6.0  | 6.3  | V    |

| Hall amplifier input offset voltage            | V <sub>H offset</sub>   |                                                                                                                | -5   |      | +5   | mV   |

| Hall amplifier input bias current              | I <sub>H bias</sub>     |                                                                                                                |      | 1    | 5    | μA   |

| Hall amplifier common-mode input voltage range | V <sub>Hch</sub>        |                                                                                                                | 1.3  |      | 2.2  | V    |

| Hall input/output voltage gain                 | G <sub>VHO</sub>        |                                                                                                                | 40   | 43   | 46   | dB   |

| Control/output drive gain 1                    | G <sub>VCO</sub> 1      | RZ1 = RZ2, GC1 = L, GC2 = L                                                                                    | 26   | 29   |      | dB   |

| Control/output channel difference 1            | ∆G <sub>VCO</sub> 1     | RZ1 = RZ2, GC1 = L, GC2 = L                                                                                    | -1.5 |      | +1.5 | dB   |

| Control/output drive gain 2                    | G <sub>VCO</sub> 2      | RZ1 = RZ2, GC1 = L, GC2 = H                                                                                    | 32   | 35   |      | dB   |

| Control/output channel difference 2            | ∆G <sub>VCO</sub> 2     | RZ1 = RZ2, GC1 = L, GC2 = H                                                                                    | -1.9 |      | +1.9 | dB   |

| Input dead zone voltage                        | V <sub>DZ</sub>         | RZ1 = RZ2, GC1 = L, GC2 = L<br>V <sub>O</sub> (voltage between out and out) = $0.1 \text{ V}$                  | ±13  | ±38  | ±55  | mV   |

| Input bias current 1                           | IB SERVO                | $V_{\rm C} = 1.0 \ {\rm V}$                                                                                    |      |      | 500  | nA   |

| Input bias current 2                           | I <sub>B n.s</sub>      | V <sub>NS</sub> = 1.0 V                                                                                        |      |      | 500  | nA   |

| S/S pin high voltage                           | V <sub>S/S H</sub>      | Input is CMOS level                                                                                            | 4    |      |      | V    |

| S/S pin low voltage                            | V <sub>S/S L</sub>      | Note) S/S pin Vth = V <sub>CC</sub> 2/2                                                                        |      |      | 1    | V    |

| Gain control 1 high voltage                    | V <sub>GC1 H</sub>      | Input is at CMOS level.                                                                                        | 4    |      |      | V    |

| Gain control 1 low voltage                     | V <sub>GC1 L</sub>      | Note) GC1 pin Vth = 2.0 V                                                                                      |      |      | 1    | V    |

| Gain control 2 high voltage                    | V <sub>GC2 H</sub>      | Input is at CMOS level.                                                                                        | 4    |      |      | V    |

| Gain control 2 low voltage                     | V <sub>GC2 L</sub>      | Note) GC2 pin Vth = 2.0 V                                                                                      |      |      | 1    | V    |

| S/S pin input current                          | I <sub>S/S</sub>        | Input voltage = 5 V                                                                                            |      | 50   | 100  | μA   |

| Gain control 1, 2 current                      | I <sub>GC</sub>         | Input voltage = 5 V                                                                                            |      | 53   | 110  | μA   |

| Rotation output saturation voltage             | V <sub>(sat) H.FG</sub> | $I_0 = -5 \text{ mA}$                                                                                          |      | 0.24 | 0.5  | V    |

| Rotation output saturation sustaining voltage  | V <sub>(sus)</sub> H.FG |                                                                                                                |      |      | 7    | V    |

| Hall bias voltage                              | V <sub>H</sub> ±        | I <sub>O</sub> = 5 mA, R <sub>H</sub> = 200 Ω                                                                  | 0.7  | 0.97 | 1.2  | V    |

| CTRL pin high voltage                          | V <sub>CTRL</sub> H     | Common for CTRL1 and CTRL2<br>input CMOS level                                                                 | 4    |      |      | V    |

| CTRL pin low voltage                           | V <sub>CTRL L</sub>     | Note) CTRL pin Vth = 2.5 V                                                                                     |      |      | 1.0  | V    |

| CTRL input current                             | ICTRL                   | Input voltage = 5 V                                                                                            |      | 53   | 110  | μA   |

| TSD operation voltage                          | TSD                     | Design target                                                                                                  | 150  | 180  | 210  | °C   |

| TSD hysteresis                                 | ΔTSD                    | Design target                                                                                                  |      | 15   |      | °C   |

Note) Vth is a design target and not measured.

#### Mode Switching Truth Table

| CTRL0 | CTRL1 | Mode         |

|-------|-------|--------------|

| L     | L     | Control      |

| L     | Н     | Noncontrol   |

| Н     | L     | Acceleration |

| Н     | Н     | Deceleration |

L = 0 to 1.0 V

H = 4.0 V or more

#### Hall Logic Truth Table

|   |                                                                   | Hall input      |                 |                 | F/R Control |  |

|---|-------------------------------------------------------------------|-----------------|-----------------|-----------------|-------------|--|

|   | Source $\rightarrow$ Sink                                         | U <sub>IN</sub> | V <sub>IN</sub> | W <sub>IN</sub> |             |  |

| 1 | $W \rightarrow V$                                                 | Н               | н               |                 | Forward     |  |

|   | $V \rightarrow W$                                                 |                 |                 |                 | Reverse     |  |

| 2 | $W \rightarrow U$                                                 |                 |                 | L               | Forward     |  |

| 2 | $U\toW$                                                           | Н               | L               |                 | Reverse     |  |

| 3 | $V \rightarrow W$                                                 | L               | L               | н               | Forward     |  |

| 5 | $W \to V$                                                         |                 |                 |                 | Reverse     |  |

| 4 | $\begin{array}{c} U \rightarrow V \\ V \rightarrow U \end{array}$ | L               | н               | L               | Forward     |  |

| 4 |                                                                   |                 |                 |                 | Reverse     |  |

| 5 | $V \rightarrow U$                                                 | Н               | L               | н               | Forward     |  |

| 5 | $U\toV$                                                           |                 |                 |                 | Reverse     |  |

| 6 | $U\toW$                                                           | L               | н               |                 | Forward     |  |

|   | $W\toU$                                                           |                 |                 | H               | Reverse     |  |

An input is considered to be HIGH when  $U_{IN}1>U_{IN}2$ ,  $V_{IN}1>V_{IN}2$ , and  $W_{IN}1>W_{IN}2$  by 0.2 V or more. Forward when  $V_C>V_{Cref}$ Reverse when  $V_C<V_{Cref}$

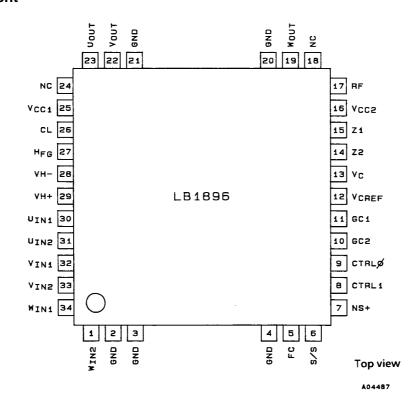

# Pin Assignment

#### **Pin Functions**

| Pin No.        | Pin Name                                                 | Pin Voltage                 | Equivalent Circuit Diagram                                                   | Pin Function                                                                                                                                                                                                                                                                                                                               |

|----------------|----------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 4<br>20, 21 | Frame<br>GND                                             |                             |                                                                              | Frame GND.<br>GND must be shared.                                                                                                                                                                                                                                                                                                          |

| 2              | GND                                                      |                             |                                                                              | GND                                                                                                                                                                                                                                                                                                                                        |

| 23<br>22<br>19 | U <sub>OUT</sub><br>V <sub>OUT</sub><br>W <sub>OUT</sub> |                             | OVCC1<br>(23)<br>(19)<br>ORf<br>A04490                                       | Output pins.<br>Motor connection                                                                                                                                                                                                                                                                                                           |

| 17             | Rf                                                       |                             | OVCC2<br>17) R f<br>404481                                                   | Output Tr GND.<br>A resistor can be connected between this pin<br>and GND to sense the output current as a<br>voltage drop to provide for overcurrent<br>protection.                                                                                                                                                                       |

| 18, 24         | NC                                                       |                             |                                                                              | Idle pins.                                                                                                                                                                                                                                                                                                                                 |

| 16             | V <sub>CC</sub> 2                                        | 4.3 to 6.5 V                |                                                                              | <ul> <li>Power supply for blocks other than the output block.</li> <li>This supply should be kept stable to prevent ripple and noise from entering this pin.</li> </ul>                                                                                                                                                                    |

| 15<br>14       | Z1<br>Z2                                                 |                             | OVCC2<br>OVCC2<br>OVCC2<br>OVCC2<br>OVCC2<br>OCD<br>OCD<br>OCD<br>OCD<br>OCD | <ul> <li>First-stage amplifier gain setting resistors.</li> <li>Z1 and Z2 normally range from several tens of kΩ to several hundreds of kΩ.</li> <li>The gain is about 6 dB.</li> </ul>                                                                                                                                                    |

| 13<br>12       | V <sub>C</sub><br>V <sub>Cref</sub>                      | V <sub>CC</sub> 2/2<br>±1.0 | VCC2<br>VCC2<br>VCC2<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | <ul> <li>V<sub>C</sub> is the speed control pin.<br/>Forward when V<sub>C</sub> &gt; V<sub>Cref</sub>.<br/>Reverse when V<sub>C</sub> &lt; V<sub>Cref</sub>.<br/>V<sub>C</sub> is used to control the output voltage.</li> <li>V<sub>Cref</sub> determines the motor control stop voltage.<br/>V<sub>CC</sub>2/2 in normal use.</li> </ul> |

| 11<br>10       | GC1<br>GC2                                               | 0 to V <sub>CC</sub> 2      | VCC2                                                                         | <ul> <li>Input/output gain switching pins.</li> <li>GC1 is for first-stage amplifier Z1/Z2<br/>switching.</li> <li>When GC1 is LOW, Z1 is selected;<br/>when HIGH, Z2 is selected. GC2 is for<br/>next-stage amplifier switching.</li> </ul>                                                                                               |

Continued on next page.

Continued from preceding page.

| Pin No.                         | Pin Name                                                                                                                   | Pin Voltage                     | Equivalent Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin Function                                                                                                                                                                                                                           |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9<br>8                          | CTRL¢<br>CTRL1                                                                                                             | 0 to V <sub>CC</sub> 2          | VCC2<br>VCC2<br>() (8) (7) (7) (7) (7) (7) (7) (7) (7) (7) (7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Operation mode switching pins.</li> <li>Refer to the Mode Switching Truth Table<br/>for selection of control, acceleration, or<br/>deceleration.</li> </ul>                                                                   |

| 7                               | NS+                                                                                                                        | 0 to<br>V <sub>CC</sub> 2 – 1 V | VCC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>Input pin at noncontrol mode.</li> <li>The input-output gain is 14 dB.<br/>(GC2: LOW)</li> <li>Motor stops when V<sub>NS</sub> = 0 V.</li> </ul>                                                                              |

| 6                               | S/S                                                                                                                        | 0 to V <sub>CC</sub> 2          | €                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>When the S/S pin is HIGH, START;<br/>when LOW, STOP.</li> <li>The threshold is V<sub>CC</sub>2/2.</li> </ul>                                                                                                                  |

| 5                               | FC                                                                                                                         |                                 | 5<br>5<br>5<br>6<br>6<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Connect a capacitor between this pin and<br>GND to reduce the input/output gain<br>frequency response and to stop the<br>oscillator.                                                                                                   |

| 1<br>34<br>33<br>32<br>31<br>30 | W <sub>IN</sub> 2<br>W <sub>IN</sub> 1<br>V <sub>IN</sub> 2<br>V <sub>IN</sub> 1<br>U <sub>IN</sub> 2<br>U <sub>IN</sub> 1 | 1.3 to 2.2 V                    | 34         1           32         1           30         1           1         1           33         33           30         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1           1         1< | W-phase Hall device input pins.<br>Logic "H" represent $W_{IN}1 > W_{IN}2$<br>V-phase Hall device input pins.<br>Logic "H" represent $V_{IN}1 > V_{IN}2$<br>U-phase Hall device input pins.<br>Logic "H" represent $U_{IN}1 > U_{IN}2$ |

Continued on next page.

Continued from preceding page.

| Pin No.  | Pin Name          | Pin Voltage            | Equivalent Circuit Diagram                                                                 | Pin Function                                                                                                                                                                             |

|----------|-------------------|------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29<br>28 | VH+<br>VH–        | 2.4 V<br>1.4 V         | CC2<br>(28)<br>(28)<br>(28)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29 | <ul> <li>Hall device power supply pins.<br/>A voltage difference of 1.0 V is developed<br/>between VH+ and VH</li> </ul>                                                                 |

| 27       | H.FG              | 0 to V <sub>CC</sub> 2 |                                                                                            | <ul> <li>Hall FG pin.</li> <li>The Hall waveform is converted into a pulse signal and then used as the FG pulse signal.</li> </ul>                                                       |

| 26       | CL                | 0 to V <sub>CC</sub> 2 | ZG<br>W<br>W<br>CC2<br>VCC2<br>VCC2<br>A04502                                              | <ul> <li>When the Rf pin voltage becomes equal to<br/>the C<sub>L</sub> pin voltage, the current limiter<br/>operate. The C<sub>L</sub> voltage is determined<br/>externally.</li> </ul> |

| 25       | V <sub>CC</sub> 1 | 5 to 18 V              |                                                                                            | <ul> <li>Power supply for output block.</li> <li>This supply should be kept stable to<br/>prevent ripple and noise from entering this<br/>pin.</li> </ul>                                |

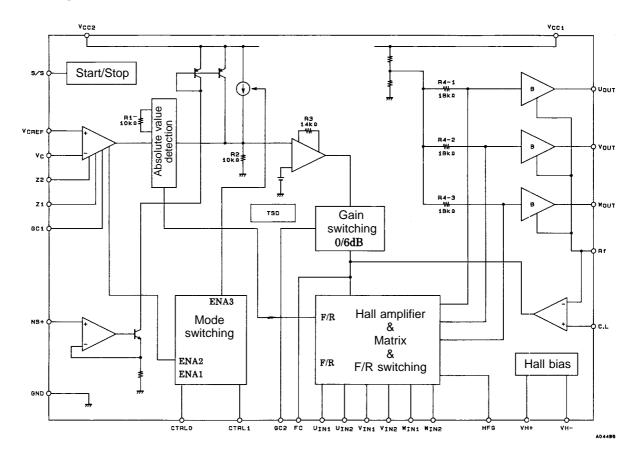

#### **Block Diagram**

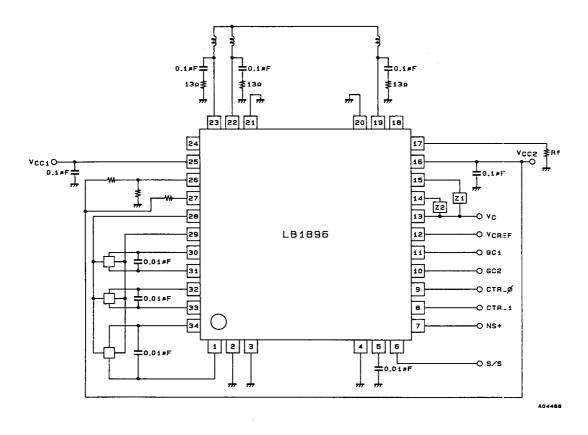

**Sample Application Circuit**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1996. Specifications and information herein are subject to change without notice.