## **Typical Applications**

The HMC226 is ideal for:

- 900 MHz ISM/Cellular

- 1900 MHz PCS

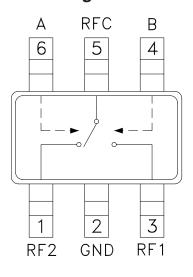

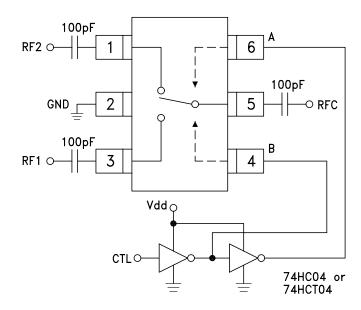

## **Functional Diagram**

#### Features

Low Insertion Loss: 0.6 dB

Ultra Small Package: SOT26

High Input P1dB: +35 to +38 dBm

High Input IP3: +55 to +61 dBm

Positive Control: 0/+3V to 0/+8V

## **General Description**

The HMC226 is a low-cost SPDT switch in a 6-lead SOT26 package for use in transmit-receive applications which require very low distortion at high signal power levels. The device can control signals from DC to 2.0 GHz and is especially suited for 450 MHz, 900 MHz, and 1.8 - 2.0 GHz applications with 0.5 to 0.8 dB loss. The design provides exceptional P1dB and intermodulation performance; a +35 dBm 1dB compression point and +55 dBm third order intercept at +3 volt bias. RF1 and RF2 are reflective opens when "Off". On-chip circuitry allows single positive supply operation at very low DC current with control inputs compatible with CMOS and most TTL logic families.

# Electrical Specifications, $T_A = +25^{\circ}$ C, Vctl = 0/+3 Vdc, 50 Ohm System

| Parameter                                                                 |                                | Frequency                                    | Min.           | Тур.              | Max.              | Units          |

|---------------------------------------------------------------------------|--------------------------------|----------------------------------------------|----------------|-------------------|-------------------|----------------|

| Insertion Loss                                                            |                                | DC - 0.5 GHz<br>DC - 1.0 GHz<br>DC - 2.0 GHz |                | 0.5<br>0.6<br>0.8 | 0.8<br>0.9<br>1.2 | dB<br>dB<br>dB |

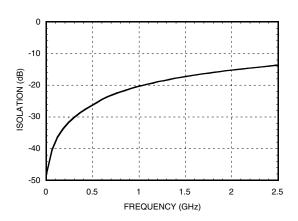

| Isolation                                                                 |                                | DC - 0.5 GHz<br>DC - 1.0 GHz<br>DC - 2.0 GHz | 23<br>17<br>12 | 26<br>20<br>15    |                   | dB<br>dB<br>dB |

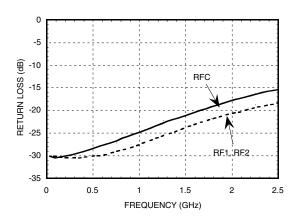

| Return Loss                                                               |                                | DC - 0.5 GHz<br>DC - 1.0 GHz<br>DC - 2.0 GHz | 23<br>21<br>14 | 27<br>25<br>18    |                   | dB<br>dB<br>dB |

| Input Power for 1 dB Compression                                          | 0/5V Control<br>0/3V Control   | 0.3 - 2.0 GHz                                | 34<br>31       | 38<br>35          |                   | dBm<br>dBm     |

| Input Third Order Intercept<br>(Two-Tone Input Power = +26 dBm Each Tone) | 0/5V Control<br>0/3V Control   | 0.3 - 2.0 GHz                                |                | 61<br>55          |                   | dBm<br>dBm     |

| Switching Characteristics                                                 |                                | DC - 2.0 GHz                                 |                |                   |                   |                |

| tRISE, tFAL<br>tON, tOFF (50% CTL                                         | L (10/90% RF)<br>to 10/90% RF) |                                              |                | 70<br>140         |                   | ns<br>ns       |

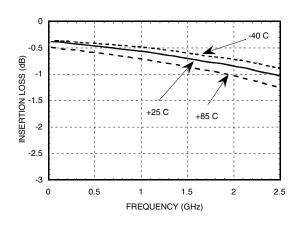

### Insertion Loss vs Temperature

#### Isolation

#### Return Loss

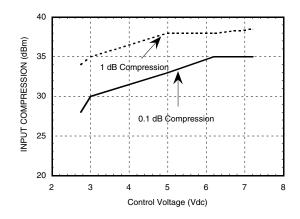

# Input 0.1 and 1.0 dB Compression vs. Control Voltage @ 900 MHz

## Compression vs. Control Voltage @ 900 MHz

| Control<br>Input | Input Power<br>for 0.1 dB<br>Compression | Input Power<br>for 1.0 dB<br>Compression |

|------------------|------------------------------------------|------------------------------------------|

| (Vdc)            | (dBm)                                    | (dBm)                                    |

| +3               | 30                                       | 35                                       |

| +5               | 33                                       | 38                                       |

| +7               | 35                                       | 38.5                                     |

Caution: Do not operate continuously at power levels >1 dB compression and do not "hot switch" power levels greater than +23dBm ( $V_{\rm CTL}$  = +3Vdc).

**Truth Table**\*Control Input Voltage Tolerances are ± 0.2 Vdc.

| Contro     | I Input*   | Control Current |            | Signal Path State |              |  |

|------------|------------|-----------------|------------|-------------------|--------------|--|

| A<br>(Vdc) | B<br>(Vdc) | la<br>(uA)      | lb<br>(uA) | RF to<br>RF1      | RF to<br>RF2 |  |

| 0          | +3         | -5              | 5          | ON                | OFF          |  |

| +3         | 0          | 5               | -5         | OFF               | ON           |  |

| 0          | +5         | -10             | 10         | ON                | OFF          |  |

| +5         | 0          | 10              | -10        | OFF               | ON           |  |

| 0          | +8         | -45             | 45         | ON                | OFF          |  |

| +8         | 0          | 45              | -45        | OFF               | ON           |  |

DC Blocks are required at ports RFC, RF1 and RF2.

# Absolute Maximum Ratings

| Max. Input Power (V <sub>CTL</sub> = 0/+3V) | 0.05 GHz<br>0.5 - 2 GHz |                 |  |

|---------------------------------------------|-------------------------|-----------------|--|

| Control Voltage Range (A & B)               |                         | -0.2 to +12 Vdc |  |

| Storage Temperature                         |                         | -65 to +150 °C  |  |

| Operating Temperature                       |                         | -40 to +85 °C   |  |

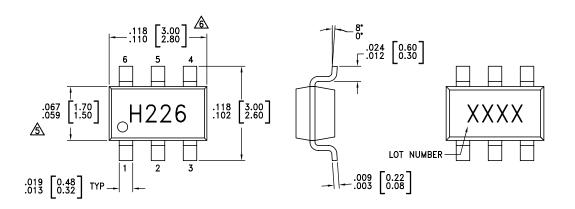

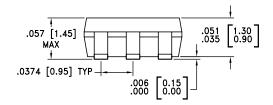

# **Outline Drawing**

#### NOTES:

- 1. PACKAGE BODY MATERIAL: LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED.

- 2. LEADFRAME MATERIAL: COPPER ALLOY

- 3. LEADFRAME PLATING: Sn/Pb SOLDER

- 4. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.15mm PER SIDE.

- dimension does not include moldflash of 0.25mm per side.

- 7. ALL GROUND LEADS MUST BE SOLDERED TO PCB RF GROUND.

# **Typical Application Circuit**

#### Notes:

- 1. Set logic gate and switch Vdd = +3V to +5V and use HCT series logic to provide a TTL driver interface.

- 2. Control inputs A/B can be driven directly with CMOS logic (HC) with Vdd of 3 to 8 Volts applied to the CMOS logic gates.

- 3. DC Blocking capacitors are required for each RF port as shown. Capacitor value determines lowest frequency of operation.

- 4. Highest RF signal power capability is achieved with V set to +10V. The switch will operate properly (but at lower RF power capability) at bias voltages down to +3V.

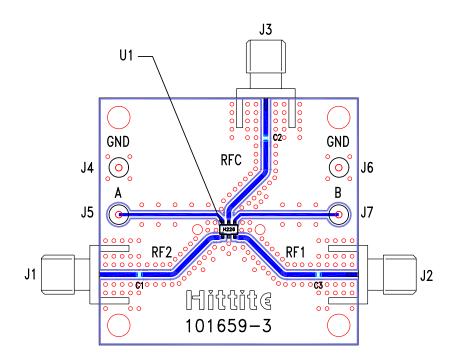

#### **Evaluation Circuit Board**

### List of Material

| Item                                  | Description                 |  |

|---------------------------------------|-----------------------------|--|

| J1 - J3                               | PC Mount SMA RF Connector   |  |

| J4 - J7                               | DC Pin                      |  |

| C1 - C3                               | 330 pF capacitor, 0402 Pkg. |  |

| U1                                    | HMC226 T/R Switch           |  |

| PCB*                                  | 101659 Evaluation PCB       |  |

| * Circuit Board Material: Rogers 4350 |                             |  |

The circuit board used in the final application should be generated with proper RF circuit design techniques. Signal lines at the RF port should have 50 ohm impedance and the package ground leads and package bottom should be connected directly to the ground plane similar to that shown above. The evaluation circuit board shown above is available from Hittite Microwave Corporation upon request.