# Qualification Package TSC87251G2D / TSC83251G2D 0.5 µm SCMOS3 Technology

TEMIC SEMICONDUCTORS IS AN ATMEL COMPANY

# Qualpack TSC87251G2D

| 1. General Information                                                                                | 3      |

|-------------------------------------------------------------------------------------------------------|--------|

| 1.1 Product Description                                                                               | 3      |

| 2. Technology Information                                                                             | 4      |

| 2.1 Wafer Process Technology<br>2.1.1 SCMOS3 0.5um ROM Process<br>2.1.2 SCMOS3 NV 0.5um EPROM Process | 4      |

| 2.2 Product Design                                                                                    |        |

| 2.3 Package Technology<br>2.3.1 Package description<br>2.3.2 Other available packages                 | 6<br>6 |

| 2.4 Test                                                                                              | 7<br>8 |

| 3. Qualification                                                                                      |        |

| 3.1 Change Procedure                                                                                  | . 11   |

| 3.3 Wafer Process Qualification                                                                       | . 13   |

| 3.3.1 Process Module Reliability<br>3.3.1.1 Hot carrier qualification<br>3.3.1.2 Electromigration     | .13    |

| 3.3.1.3 Time Dependent Dielectric Breakdown                                                           | .16    |

| 3.3.2 Z92 Wafer Process Qualification Results                                                         |        |

| 3.4 Package Qualification                                                                             |        |

| 3.5 Device Qualification<br>3.5.1 Failure Mechanisms and Corrective Actions                           |        |

| 3.5.2 Qualification status                                                                            |        |

| 3.6 Outgoing Quality and Reliability<br>3.6.1 AOQ (Average Outgoing Quality)                          |        |

| 3.6.2 EFR (Early Failure Rate)                                                                        | . 22   |

| 4. User Information                                                                                   |        |

| 4.1 Soldering Recommendations                                                                         | . 24   |

| 4.2 DRY PACK Ordering rules                                                                           |        |

| 5. Environmental Information                                                                          |        |

| 6. Other Data                                                                                         | 26     |

| 6.1 ISO9001 Approval Certificate                                                                      |        |

| 6.2 Databook Reference                                                                                | . 27   |

| 6.3 Address Reference                                                                                 | . 27   |

| 7. Revision History                                                                                   | . 28   |

# 1. General Information

## 1.1 Product Description

| Product Name:                    | TSC87251G2D / TSC83251G2D                                               |  |

|----------------------------------|-------------------------------------------------------------------------|--|

| Function:                        | 8/16-bit Microcontrollers<br>32K EPROM / 32K ROM                        |  |

| Wafer process:                   | Z94 (SCMOS 3 NV) / Z92 (SCMOS 3)                                        |  |

| Available plastic package types: | Wide range of packages including PLCC44, PDIP40, PQFP44, TQFP44, VQFP44 |  |

| Other forms                      | Multiple Hermetic Packages, Die, Wafer                                  |  |

| Locations:                       |                                                                         |  |

| Process, product development     | TEMIC Semiconductors Nantes, France                                     |  |

| Wafer plant                      | TEMIC Semiconductors Nantes, France                                     |  |

| QC responsibility                | TEMIC Semiconductors Nantes, France                                     |  |

| Assembly                         | GATEWAY, Philippines - ASE, Taiwan                                      |  |

|                                  | CHINTEIK, Thailand - ANAM, Korea and Philippines CHIPPAC, China         |  |

| Probe test                       | TEMIC Semiconductors Nantes, France                                     |  |

| Final test                       | GATEWAY, Philippines - ASE, Taiwan                                      |  |

|                                  | ANAM, Korea and Philippines                                             |  |

| Shipment control                 | GLOBAL LOGISTICS CENTER, Philippines                                    |  |

| Quality Assurance                | TEMIC Semiconductors Nantes, France                                     |  |

| Reliability testing              | TEMIC Semiconductors Nantes, France                                     |  |

| Failure analysis                 | TEMIC Semiconductors Nantes, France                                     |  |

Product Quality Management Nantes Signed :

Pascal LECUYER

# Qualpack TSC87251G2D

# 2. Technology Information

## 2.1 Wafer Process Technology

2.1.1 SCMOS3 0.5um ROM Process

| Process type (Name):                                                                                 | CMOS (SCMOS3 - Z92)                                                                                                        |  |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Base material:<br>Wafer Thickness (final)<br>Wafer diameter                                          | Bulk<br>475 μm<br>150 mm                                                                                                   |  |

| Number of masks                                                                                      | 16                                                                                                                         |  |

| Gate oxide<br>Material<br>Thickness                                                                  | Silicon dioxide<br>110 A (optical - 120A electrical)                                                                       |  |

| Polysilicon<br>Number of layers<br>Thickness                                                         | 1<br>3000 A                                                                                                                |  |

| Metal<br>Number of layers<br>Material<br>Layer 1 thickness<br>Layer 2 thickness<br>Layer 3 thickness | 3<br>Ti + TiN + AlCu<br>300A + 600A + 5000A + 250A TiN<br>300A + 600A + 5000A + 250A TiN<br>300A + 600A + 6500A + 250A TiN |  |

| Passivation<br>Material<br>Thickness                                                                 | SiO <sub>2</sub> / Si <sub>3</sub> N <sub>4</sub><br>3000A / 7000 A                                                        |  |

#### 2.1.2 SCMOS3 NV 0.5um EPROM Process

| Process type (Name):                                        | CMOS (SCMOS3 NV - Z94)                    |  |

|-------------------------------------------------------------|-------------------------------------------|--|

| Base material:<br>Wafer Thickness (final)<br>Wafer diameter | Bulk<br>475 μm<br>150 mm                  |  |

| Number of masks                                             | 22                                        |  |

| Gate oxide                                                  |                                           |  |

| Material                                                    | Silicon dioxide                           |  |

| Thickness                                                   | 110 A (optical - 120A electrical)         |  |

| Polysilicon                                                 |                                           |  |

| Number of layers                                            | 2                                         |  |

| Thickness Poly1                                             | 2000 A (amorphous)                        |  |

| Thickness Poly2                                             | 3000 A (polysilicon)                      |  |

| Metal                                                       |                                           |  |

| Number of layers                                            | 3                                         |  |

| Material                                                    | Ti + TiN + AlCu + TiN                     |  |

| Layer 1 thickness                                           | 300A Ti + 600A TiN + 5000A AlCu+ 250A TiN |  |

| Layer 2 thickness                                           | 300A Ti + 600A TiN + 5000A AlCu+ 250A TiN |  |

| Layer 3 thickness                                           | 300A Ti + 600A TiN + 6500A AlCu+ 250A TiN |  |

| Passivation                                                 |                                           |  |

| Material                                                    | SiO <sub>2</sub> / Nitride Oxide          |  |

| Thickness                                                   | 3000A /15000 A                            |  |

## 2.2 Product Design

| Die size<br>Pad size           | For TSC87251G2D: 17.84 mm <sup>2</sup> (4250 μm * 4400 μm)<br>For TSC83251G2D: 17.84 mm <sup>2</sup> (4250 μm * 4400 μm)<br>84 μm * 84 μm |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Effective channel length | 0.42 μm                                                                                                                                   |

| Gate poly width                | 0.5 μm                                                                                                                                    |

| Gate poly spacing              | 0.6 µm                                                                                                                                    |

| Metal 1 width                  | 0.6 µm                                                                                                                                    |

| Metal 1 spacing                | 0.7 μm                                                                                                                                    |

| Metal 2 width                  | 0.8 µm                                                                                                                                    |

| Metal 2 spacing                | 0.7 μm                                                                                                                                    |

| Metal 3 width                  | 0.8 µm                                                                                                                                    |

| Metal 3 spacing                | 0.7 μm                                                                                                                                    |

| Contact size                   | 0.6 µm                                                                                                                                    |

| Via 1 size                     | 0.6 µm                                                                                                                                    |

| Via 2 size                     | 0.7 μm                                                                                                                                    |

## 2.3 Package Technology

#### 2.3.1 Package description

Depending on the customer's need. For information, the following data concern the PLCC 44.

| Package weight         | 2.34g                     |  |  |

|------------------------|---------------------------|--|--|

| Chip separation method | Sawing                    |  |  |

| Lead frame             |                           |  |  |

| Material               | Cu                        |  |  |

| Thickness              | 10 mils                   |  |  |

| Size                   | 270*270 mils <sup>2</sup> |  |  |

| Lead plating           | Electroplated Sn/Pb 85/15 |  |  |

| Die attach             |                           |  |  |

| Material               | Silver epoxy              |  |  |

| Туре                   | Ablestick 84-1 LMIS       |  |  |

| Wire bonding           |                           |  |  |

| Material               | Gold                      |  |  |

| Diameter               | 33um                      |  |  |

|                        |                           |  |  |

# TEMIC Semiconductors

# Qualpack TSC87251G2D

| Method              |  |  |  |  |

|---------------------|--|--|--|--|

| Molding             |  |  |  |  |

| Material            |  |  |  |  |

| Flammability rating |  |  |  |  |

| Marking             |  |  |  |  |

| Method              |  |  |  |  |

| Coding example      |  |  |  |  |

Dry packing Tube packed Primary Material

- Material Number per unit Secondary Material Number per unit Labeling (minimum) Bar coding

- 2.3.2 Other available packages PQFP, PDIP, CQFP, CERDIP TQFP, VQFP

## 2.4 Test

Probe equipment

Probe temperature

Test equipment

Test temperature Commercial range Industrial range Automotive range

#### Thermosonic

Sumitomo EME 6300HS UL94V-0

Printed ink T optional special customer marking TSC83C51RB2-MCA © INTEL 80,82 Date-code Lot nbr No

Tube Antistatic PVC 27 Box Cardboard 972 Device type, Quantity, Date Code, Production code Code 39 to EIA-556-A

No dry pack required Dry pack required

SCHLUMBERGER ITS9000 / S15

85°C

SENTRY 15

25°C 25°C and optional 85°C 25°C, 125°c and optional -40°c

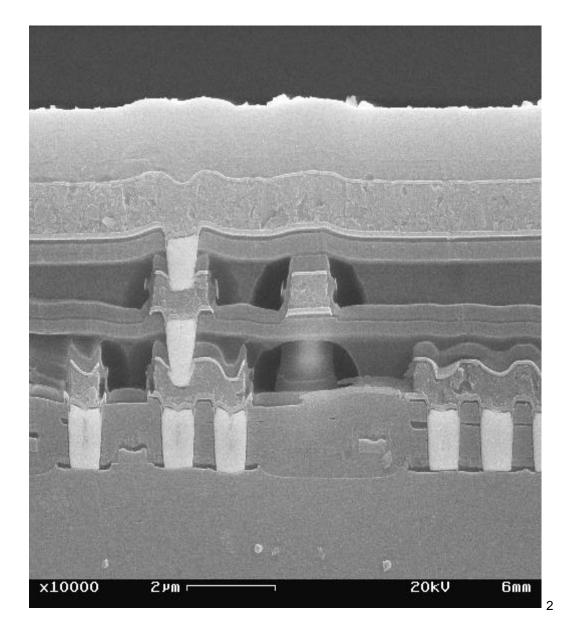

## 2.5 Device Cross Section

**Final Z92 Cross Section**

# TEMIC Semiconductors

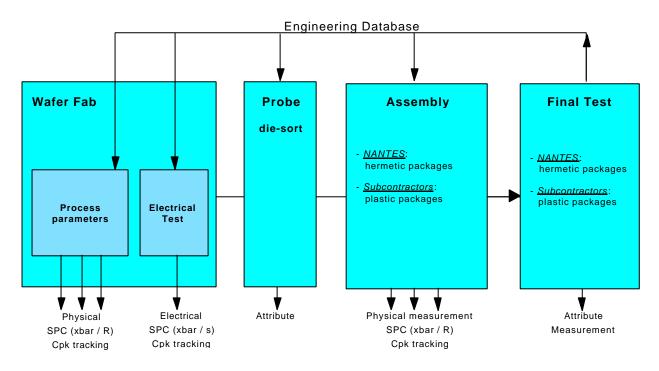

## 2.6 Wafer Process Control

All the inspections and controls are defined as a process step in the production management software, and are led by using a centralized SPC software. PC system could be summarized as follows:

Critical process parameters are identified by using F.M.E.A. and other advanced tools.

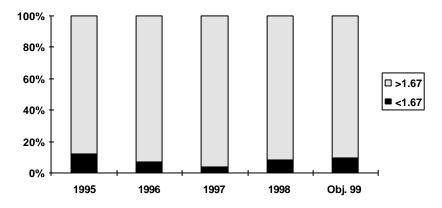

Those parameters are followed in real time with the SPC methodology and their capability is measured and monthly reported in the Operation Review.

For end 1999, the Cpk target is the following:

#### % of all parameters per Cpk categories

## 3. Qualification

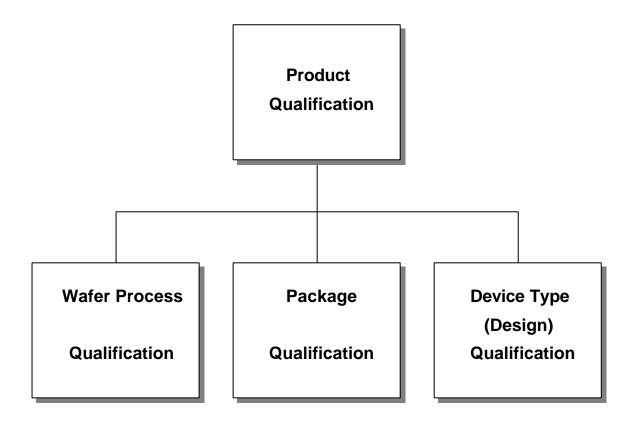

All product qualifications are split into three distinct steps as shown above. This same procedure is also used to qualify a change. Before a product is released for use, it must have been manufactured using a qualified wafer and package process. Before a device is released for production processing, it must also have successfully completed its required specific qualification.

The standard tests which are used for this procedure are shown in the section "Qualification Flow" .

## 3.1 Change Procedure

All changes are controlled by PCN (Product Change Notice). All major changes are notified to the customers affected by the change.

A major change is defined as a change that requires evidence of no electrical, mechanical impact on the product, or a change in the specification or marking of the product or packing. The list of changes usually considered as major is detailed hereafter:

| 1   | General Major Changes                 |  |

|-----|---------------------------------------|--|

| 1-1 | Manufacturing line                    |  |

| 1-2 | Sequence of fabrication process cycle |  |

| 1-3 | Material type                         |  |

| 1-4 | Electrical parameter                  |  |

| 1-5 | External physical dimension           |  |

| 1-6 | Die size                              |  |

| 2   | Changes specific to wafer fabrication area |

|-----|--------------------------------------------|

| 2-1 | Doping method                              |

| 2-2 | Gate oxide formation method                |

| 2-3 | Equipment change                           |

| 2-4 | Layer Thickness                            |

| 2-5 | Module dimensions                          |

| 3          | Changes specific to to assembly process area |  |

|------------|----------------------------------------------|--|

| 3-1        | Sawing method                                |  |

| 3-2        | Die attach                                   |  |

| 3-3        | Wire interconnect tools                      |  |

| 3-4<br>3-5 | Molding process                              |  |

| 3-5        | Tinning method                               |  |

| 4   | Changes specific to test area |

|-----|-------------------------------|

| 4-1 | Specification limit           |

| 4-2 | Test coverage reduction       |

| 4-2 | Product identification        |

| 4-3 | Final conditioning            |

## 3.2 Qualification Flow

General Requirements for Plastic packaged CMOS IC

| Standard                    | Test Description                           | Qualification type<br>(acceptance) |

|-----------------------------|--------------------------------------------|------------------------------------|

| MIL-STD 883D                | Electrical Life Test (Early Failure Rate)  | Device                             |

| Method 1005                 | 12 hours 150°C (Tj) 5.75V                  | (1/2000 12h)                       |

| MIL-STD 883D                | Electrical Life Test (Latent Failure Rate) | Device                             |

| Method 1005                 | 1000 hours 150°C 5.75V Dynamic or Static   | (0/100 500h)                       |

| MIL-STD 883D                | Electrostatic Discharge HBM                | Device                             |

| Method 3015.7               | +/-2000v 1.5kOhm/100pF/3 pulses            | (0/3 per level)                    |

| JEDEC 78                    | Latch up<br>50mW power injection 125°C     | Device<br>(0/10)                   |

| MHS                         | NV Memory Dataretention                    | Device                             |

| PAQA0046                    | High Temperature Storage 165°C             | (0/50 500c)                        |

| MIL-STD 883D                | Temperature Cycling                        | Die and Package                    |

| Method 1010                 | 1000 cycles -65°C/150°C air/air            | (0/50 500c)                        |

| MHS                         | Pressure Pot after Mounting Stress         | Die and Package                    |

| PAQA0184                    | 168 hours 130°C/85%RH                      | (0/50 168h)                        |

| EIA                         | <b>85/85 Humidity Test</b>                 | Die and Package                    |

| JESD22-A101                 | 1000 hours 85°C/85%RH                      | (0/50 500h)                        |

| EIA                         | HAST                                       | Die and Package                    |

| JESD22-A110                 | 336 hours 130°C/85%RH/5.5V                 | (0/50 168h)                        |

| EIA                         | Moisture Sensitivity Ranking               | Package                            |

| JEDEC J-20-STD              | Infra Red Stress 220°C/235°c/3 times       | (0/10 per class)                   |

| MIL-STD 883D<br>Method 2003 | Solderability                              | Package<br>(0/3)                   |

| MIL-STD 883D<br>Method 2015 | Marking Permanency                         | Package<br>(0/5)                   |

## 3.3 Wafer Process Qualification

#### 3.3.1 Process Module Reliability

This chapter contains all the information relative to the reliability of the SCMOS3 technology. Results presented in the following sections concern the reliability of the basic process steps that build up the technology.

#### 3.3.1.1 Hot carrier qualification

#### STATIC NMOS DEGRADATION

| Channel length in µm                                  | 0.5   | 0.55  | 0.6   | 0.65  | 0.7   | 0.5     |

|-------------------------------------------------------|-------|-------|-------|-------|-------|---------|

| Process corner                                        | Fast  | Fast  | Fast  | Fast  | Fast  | Typical |

| Substrate current in µA/µm<br>VD=5.5v, VG=2.25v       | 17    | 15    | 13.4  | 12.1  | 11.1  | 14.7    |

| Substrate current in µA/µm<br>VD=3.6v, VG=1.6v        | 0.35  | 0.3   | 0.25  | 0.22  | 0.2   | 0.3     |

| Lifetime in seconds for 10% shift of Gm at VD=5.5v    | 3.2e3 | 3.7e3 | 4.2e3 | 4.7e3 | 5.2e3 | 3.8e3   |

| Lifetime in seconds for 10% shift of<br>Gm at VD=3.6v | 8e7   | 10e7  | 12e7  | 14e7  | 16e7  | 10e7    |

#### STATIC PMOS DEGRADATION

| Channel length in µm                                  | 0.5    | 0.55   | 0.6    | 0.65   | 0.7    | 0.5     |

|-------------------------------------------------------|--------|--------|--------|--------|--------|---------|

| Process corner                                        | Fast   | Fast   | Fast   | Fast   | Fast   | Typical |

| Substrate current in µA/µm<br>VD=5.5v, VG=2.25v       | 0.31   | 0.28   | 0.25   | 0.22   | 0.21   | 0.24    |

| Substrate current in µA/µm<br>VD=3.6v, VG=1.25v       | 2.3e-3 | 1.9e-3 | 1.6e-3 | 1.4e-3 | 1.1e-3 | 1.6e-3  |

| Lifetime in seconds for 10% shift of<br>Gm at VD=5.5v | 2.7e4  | 3.1e4  | 3.5e4  | 3.9e4  | 4.3e4  | 3.5e4   |

| Lifetime in seconds for 10% shift of<br>Gm at VD=3.6v | 2e7    | 2.5e7  | 3e7    | 3.8e7  | 4.6e7  | 3.2e7   |

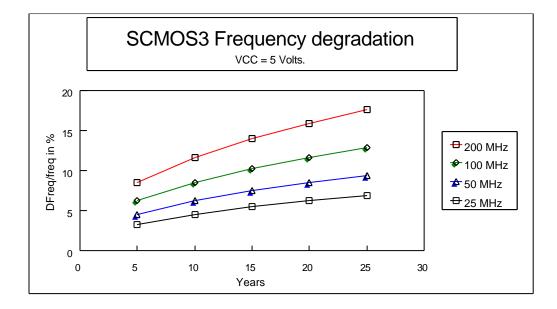

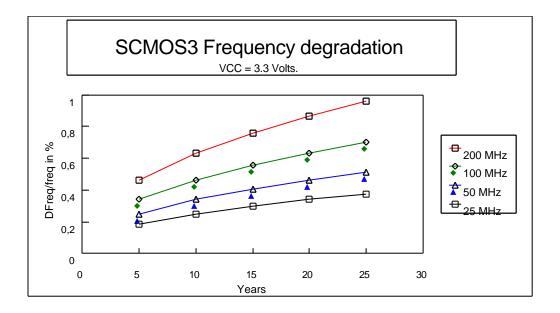

EXPERIMENTAL RESULTS IN DYNAMIC MODE: hot carrier degradation effects on inverter propagation time have been measured on oscillators running at 75 MHz at 7v and 6.5v. Accelerator factor in voltage is then carried out and expected degradation laws at 5v and 3.3v derived. The following graphs show the frequency degradation of oscillators running at 5v and 3.3v.

### 3.3.1.2 Electromigration

#### Characterization

Stresses of electromigration are achieved for 1000 hours on 32 packaged metal line running on flat with a current density of  $2x10^6$  A/cm2 at a temperature of 200°C. Lines are declared to be failed for a shift of the initial resistance by 20%. Results are summarized in the table below.

| Level  | W/L/T(1)    | Structure       | Failures |

|--------|-------------|-----------------|----------|

| Metal1 | 2/2000/0.50 | Ti/TiN/AlCu/TiN | No       |

| Metal2 | 2/2000/0.50 | Ti/TiN/AlCu/TiN | No       |

| Metal3 | 2/2000/0.70 | Ti/TiN/AlCu/TiN | No       |

<sup>(1)</sup>W/L/T=Width/Length/Thickness of the metal line in microns

#### Lifetime projection

The objective of reliability is to reach less than 10FIT on metal line within 10 years at a temperature of 150°C. As no failures have been found at 1000 hours in the above stress conditions a lifetime projection in FIT is meaningless.

However, assuming for AlCu metalization an activation energy in temperature Ea of 0.60eV and an activation in current with a power-law coefficient n of 2, the current density which guarantees no failures within 10 years at 150°C can be extrapolated.

With these assumptions the projected current density for no failures at 150°C within 10 years is calculated as  $5x10^{5}$ A/cm2 which is much higher than the current density of  $2x10^{5}$ A/cm2 specified in the design rules.

#### 3.3.1.3 Time Dependent Dielectric Breackdown

#### **QBD MEASUREMENT:**

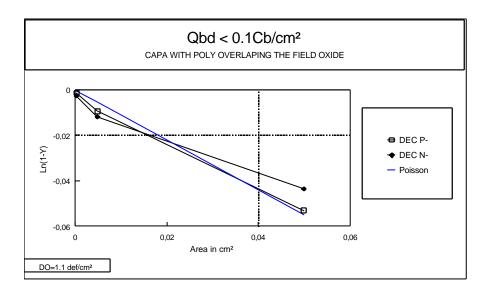

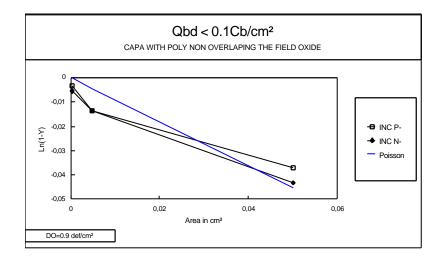

The critical charge, supported by the thin oxide and related to the extrinsic and intrinsic defects, is measured on TOX/P- and TOX/N- capacitors. The tested capacitor areas are varying from 4e-4 to 5e-2 cm2. Two types of capacitors with poly overlaping the field oxide (DEC) and poly non overlaping the field oxide (INC) are measured. The distributions have been obtained from 750 measurements for each area and type of capacitors on 10 different lots.

#### Extrinsic defects:

The two graphs here after represent the % of failures vs area for Qbd below or equal to 0.1 Cb/cm2. The law of Poisson is used to determine the D0 defect density of the extrinsic defects:

Y=1-exp(-Area \* DO)

#### Poly overlaping the Field oxide on Tox/P- and Tox/N-:

The DO is found to be 1.1 def/cm2. This result is in agreement with the goal for D0 of 1 def/cm2.

Poly non overlaping the Field oxide on Tox/P- and Tox/N-:

The DO is found to be 0.9def/cm2. This result is in agreement with the goal for D0 of 1 def/cm2.

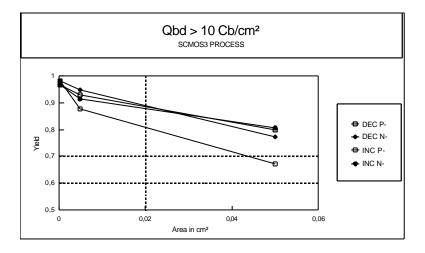

#### Intrinsic defects:

The graph here after represents the percentage of failure for a Qbd > 10 Cb/cm<sup>2</sup> vs the area. The worst case given by the bigest capacitors shows that 67% of the total distribution has a Qbd > 10 Cb/cm<sup>2</sup>. This result guarantees a good reliability behaviour. The critical charge, supported by thin oxide and related to the extrinsic defects, is measured on TOX/P- capacitors of 42570um2 and TOX/N- capacitors of 85140um2. Following are the average results obtained on recent lots from a distribution of about 60 sites per wafer. The minimum specification limit is 10C/cm<sup>2</sup>.

#### **Conclusion:**

The QBD results demonstrate high reliability level of SCMOS3 thin oxide.

#### 3.3.2 Z92 Wafer Process Qualification Results

This section summarizes the cumulated reliability data of 0.5um microcontrollers ROM technology.

| Lots                          | Device Type | Test Description                       | Step                 | Result                   | Comment                                                   |

|-------------------------------|-------------|----------------------------------------|----------------------|--------------------------|-----------------------------------------------------------|

| Z27746A                       | TSC251G2D   | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>500h<br>1000h | 3/2661<br>0/100<br>0/100 | Poly particle<br>Metal3 defect                            |

| Z27735A                       | TS80C32X2   | EFR Dynamic Life Test                  | 12h                  |                          | Contacts alignment                                        |

| Z29249<br>Z29683C<br>Z29936   |             | LFR Life Test                          | 500h<br>1000h        | 0/699<br>0/699           |                                                           |

| Z27300A<br>Z27880A<br>Z28109A | TS83C51RC2  | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>500h<br>1000h | 5/7318<br>0/200<br>0/200 | Passivation scratch<br>Poly particle<br>Silicon breakdown |

| Z26274A<br>Z26407<br>Z27291A  | TS83C51RX2  | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>500h<br>1000h | 3/2238<br>0/173<br>0/173 |                                                           |

| Global | All products | EFR Dynamic Life Test   |               |                  |                              |

|--------|--------------|-------------------------|---------------|------------------|------------------------------|

|        |              | Commercial / Industrial | 12h           | 22/23929         |                              |

|        |              | Automotive (1)          | 24h<br>168h   | 0/3564<br>0/1172 | (828 ppm / 10 mm2)<br>0ppm   |

|        |              | LFR Life Test           | 500h<br>1000h |                  | 4.7 fit<br>(3.0 fit / 10mm2) |

Note (1): The additional operations included in the automotive backend flow allow to reduce significantly the Early Life Failure Rate. As long as needed to achieve the Automotive Quality Assurance requirements, these operations may be any of those described hereafter:

- Statistical wafer sort

- Accelerated Dynamic Burn-in at probe

- Probe critical parameters 3 sigma sort

- Part Average Testing

- Dynamic Burn-in of products

- Other equivalent methods

#### 3.3.3 Z94 Wafer Process Qualification Results

This section summarizes the cumulated reliability data of 0.5um microcontrollers EPROM technology.

| Lots                                              | Device Type | Test Description                       | Step                        | Result                              | Comment                                                                                        |

|---------------------------------------------------|-------------|----------------------------------------|-----------------------------|-------------------------------------|------------------------------------------------------------------------------------------------|

| Z27314A<br>Z27748                                 | TSC87251G2D | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>24h<br>500h          | 4/3772<br>0/360<br>1/150            | Poly bridging, Interlayer oxide defect, functional not identified, metal 2 photo etch bridging |

| Z28233C                                           | TSC87C51RB2 | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>24h<br>500h<br>1000h | 1/1663<br>0/323<br>0/100<br>0/97    | Functional not identified                                                                      |

| Z28090B<br>Z28987<br>Z29142<br>Z29311D<br>Z29568B | TSC87C51RC2 | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>24h<br>500h<br>1000h | 8/11533<br>0/1284<br>0/500<br>0/500 | Poly particle<br>Contact misalignment<br>Capacitor oxide defects                               |

| Z28303C                                           | TSC87C51RD2 | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>24h<br>500h<br>1000h | 2/953<br>0/324<br>0/100<br>0/100    | Poly particle                                                                                  |

| Z28430A                                           | TSC87C52X2  | EFR Dynamic Life Test<br>LFR Life Test | 12h<br>24h<br>500h<br>1000h | 2/2333<br>0/297<br>0/100<br>0/100   | Functional not identified                                                                      |

| Global | All products | EFR Dynamic Life Test   |            |          |                    |

|--------|--------------|-------------------------|------------|----------|--------------------|

|        |              | Commercial / Industrial | 12h        | 17/20254 |                    |

|        |              |                         | <b>•</b> 4 | 0/0500   | (705 ppm / 10mm2)  |

|        |              | Automotive (1)          | 24h        | 0/2588   | 0ppm               |

|        |              |                         | 168h       | 0/950    |                    |

|        |              | LFR Life Test           | 500h       | 1/950    | 14.2 fit           |

|        |              |                         | 1000h      | 0/797    | (11.6 fit / 10mm2) |

|        |              |                         |            |          |                    |

# Qualpack TSC87251G2D

## 3.4 Package Qualification

This section summarizes the initial package qualification data of TSC87251G2D and TSC87251G2D products in PLCC44.

| Lots    | Device Type | Test Description     | Step  | Result | Comment                  |

|---------|-------------|----------------------|-------|--------|--------------------------|

|         |             |                      |       |        |                          |

| Z27314A | TSC87251G2D | 85/85 Humidity       | 500h  | 0/50   |                          |

|         | PLCC44      |                      | 1000h | 0/50   |                          |

|         |             | Moisture Sensitivity | L1    | 0/10   | Pass level 1 of J-20-STD |

|         |             | Ranking              |       |        |                          |

|         |             | HAST after Soldering | 15c   | 0/50   |                          |

|         |             | Stress               | 168h  | 0/50   |                          |

| Z27746A | TSC83251G2D | Thermal Cycles       | 500c  | 0/50   |                          |

|         | PLCC44      | -                    | 1000c | 0/50   |                          |

|         |             | HAST after Soldering | 15c   | 0/50   |                          |

|         |             | Stress               | 168h  | 0/50   |                          |

#### 3.5 Device Qualification

This section presents the qualification results of TSC87251G2D/TSC83251G2D devices.

| Lots    | Device Type           | Test Description      | Step               | Result                   | Comment                                          |

|---------|-----------------------|-----------------------|--------------------|--------------------------|--------------------------------------------------|

| Z27314A | TSC87251G2D<br>PLCC44 | EFR Dynamic Life Test | 12h<br>24h<br>168h | 2/1978<br>0/360<br>0/150 | Interlayer oxide defect<br>Polysilicide particle |

|         |                       | LFR Life Test         | 500h<br>1000h      | 1/150                    | Metal 2 photo etch bridging                      |

|         |                       | High Temp. Retention  | 500h<br>1000h      | 0/50<br>0/50             |                                                  |

| Z27746A | TSC83251G2D<br>PLCC44 | EFR Dynamic Life Test | 12h<br>24h<br>168h | 3/2661<br>0/211<br>0/100 | Polysilicide particle<br>Metal 3 defect          |

|         |                       | LFR Life Test         | 500h<br>1000h      | 0/100<br>0/100           |                                                  |

| Lots   | Device Type | Test Description                           | Step           | Result     | Comment           |

|--------|-------------|--------------------------------------------|----------------|------------|-------------------|

| Z26629 | TSC87251G2D | ESD HBM                                    | 2000V          | 3/3        | Class 1 of MIL883 |

|        |             | Latch up<br>Overvoltage<br>Power injection | 10V<br>50mW    | 0/5<br>0/5 | Latch-up free     |

| Z27746 | TSC83251G2D | ESD HBM                                    | 2000V<br>3000V | 0/3<br>0/3 | Class 2 of MIL883 |

|        |             | Latch up<br>Overvoltage<br>Power injection | 10V<br>50mW    | 0/5<br>0/5 | Latch-up free     |

#### Comments:

No reject observed during package qualification tests.

One reject in LFR, but physical analysis demonstrated the failure was wafer process dependant and not related to the device itself. As a consequence it was not charged for device qualification.

#### 3.5.1 Failure Mechanisms and Corrective Actions

As part of TEMIC continuous improvement policy, all defects are analysed. For all failure mechanisms identified, root causes ranked regards number of occurencies and criticity are investigated and addressed by corrective actions.

| Failure<br>Mechanism         | Root Cause                         | Corrective Action                                                                                                                                                | Date           | Effect                                                                               | Check of<br>Efficiency                       |

|------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------|----------------------------------------------|

| 56% Contacts<br>misalignment | RTA drift                          | Upgrade of RTA equipment                                                                                                                                         | 06/99          | reduce alignment scattering                                                          | Visual inspection,<br>yield - 07/99          |

| 26% Poly defects             | Defect<br>density at<br>Poly level | # Hard mask :<br>replacement of PR<br>Titane mask by masking<br>buffers during Ti<br>deposition for<br># polysilicideBARC<br>(Bottom Anti-Reflective<br>Coating) | 10/98          | Reduction of<br>defect density at<br>Poly level<br>Improve Poly<br>dimension control | Yield<br>EFR - 12/98<br>Yield<br>EFR - 12/98 |

|                              |                                    | # PR strip optimization                                                                                                                                          | 03/99          | Defect density reduction                                                             | EFR - 05/99                                  |

| 6% Metal particles           | PR strip<br>process                | # PR strip method<br>optimized<br># Equipment upgrade<br>(Semitool)                                                                                              | 03/99<br>07/99 | Reduction of the defect density                                                      | Yield – EFR 05/99                            |

| 6% Passivation               | Marginal                           |                                                                                                                                                                  |                |                                                                                      |                                              |

| 6% Silicon<br>breakdown      | Marginal                           |                                                                                                                                                                  |                |                                                                                      |                                              |

#### 3.5.2 Qualification status

The 0.5um logic wafer process was qualified on 1997 September. The qualification was extended to OTP microcontrollers (SCMOS3 NV) process on 1999 April.

The TSC83251G2D was qualified on 1999 January, and OTP version TSC87251G2D was full qualified on 1999 April.

## Qualpack TSC87251G2D

#### 3.6 Outgoing Quality and Reliability

#### 3.6.1 AOQ (Average Outgoing Quality)

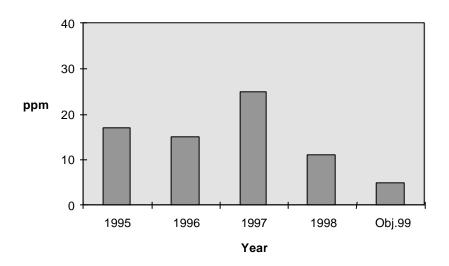

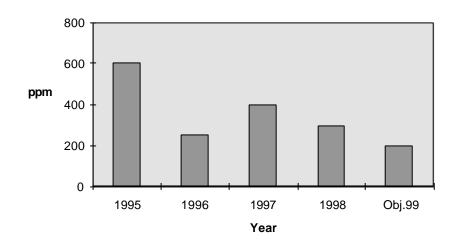

The AOQ is measured following 100% test by sampling outgoing product. The results of this inspection are recorded in ppm (parts per million) using the method defined in JEDEC 16. The figures below cover the last years for both the subject and structurally similar products.

#### 3.6.2 EFR (Early Failure Rate)

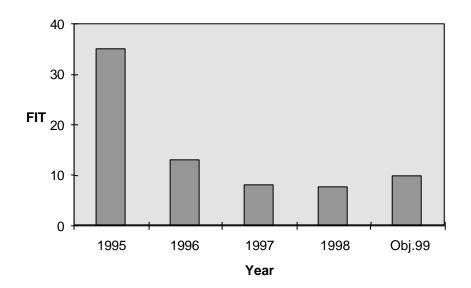

The EFR is measured on a sample of devices by operating them at an elevated temperature and measuring the number which fails to meet specification after 12 hours at 150°C. The figure is expressed in terms of ppm.

#### 3.6.3 LFR (Latent Failure Rate)

The LFR is measured by operating devices at elevated temperatures for 1000 hours and measuring the failure rate. Using the Arrhenius law, the expected failure rate at a operating temperature of 55°C is calculated using an activation Energy of 0.6 eV with a confidence level of 60%. This is expressed in units per billion hours (FIT). The figures given are for the subject and structurally similar products.

## 4. User Information

#### 4.1 Soldering Recommendations

For DRY PACKED products, TEMIC recommends to strictly follow the procedure described hereunder:

- Dry packed products must not be stored more than 1 year at 40°c 90%rh (worst storage conditions assumed)

- A longer storage period is allowed taking into account the following conditions: 5 years max at 25°c (+/-5°c) 50%rh

- From opening of the packs, the product must be assembled within 48 hours. (worst in-process storage condition assumed: 30°c 60%rh)

- If they cannot be soldered within this time period, then the pieces must be dryed at 125°c for 24 hours. Only one drying is allowed.

- Max relative humidity allowed in the bag is 20% (readable on the indicator inside the bag). If this value is reached, then the parts must be dryed at 125°C for 24 hours before mounting.

- For high sensitive products, the delay between pack openning and assembly is reduced to 6 hours (Level 6 of JEDEC 22-A112). In this case, a warning printed on each pack advises the user of this restriction.

## 4.2 DRY PACK Ordering rules

TEMIC qualification procedure allows to classify products according to JEDEC 22-A112 and to determine the convenient conditioning for safe customer use.

Nevertheless, even if the product is not classified as moisture sensitive, it is possible (for example if storage conditions are not properly controlled) to order product with a Dry Pack.

#### 4.3 ESD caution

The user must protect components against EOS and ESD damages by grounding personal and workstations.

## 5. Environmental Information

The TEMIC Environmental Policy aims are :

- Reducing the use of harmful chemicals in its processes

- Reducing the content of harmful materials in its products

- Using re-cyclable materials wherever possible

- Reducing the energy content of its products

As part of that plan, Ozone Depleting Chemicals are being replaced either by TEMIC MHS or its subcontractors' process.

## 6. Other Data

#### 6.1 ISO9001 Approval Certificate

### 6.2 Databook Reference

The datasheet is available upon request to sales representative, or on TEMIC Semiconductors web site: http://www.temic-semi.com

#### 6.3 Address Reference

All inquiries relating to this document should be addressed to the following:

TEMIC Nantes MHS S.A. BP70602 44306 Nantes Cedex 3 France Telephone (33) 2 40 18 18 18 Telefax (33) 2 40 18 19 00

Or Direct contact Pascal LECUYER Quality Engineer Telephone (33) 2 40 18 17 73 Telefax (33) 2 40 18 19 00

## 7. Revision History

| Issue | Modification Notice                  | Application Date |

|-------|--------------------------------------|------------------|

| 0     | Initial Product Qualification Report | 1999 October     |

|       |                                      |                  |

|       |                                      |                  |

|       |                                      |                  |

#### Remarks:

The information given in this document is believed to be accurate and reliable. However, no responsability is assumed by TEMIC for its use. No specific guarantee or warranty is implied or given by this data unless agreed in writing elsewhere.

TEMIC reserves the right to update or modify this information without notification, at any time, in the interest of providing the latest information.

Parts of this publication may be reproduced without special permission on the condition that our author and source are quoted and that two copies of such extracts are placed at our disposal after publication. Before use of such reproduced material the user should check that the information is current.

Written permission must be obtained from the publisher for complete reprints or translations.