## 8K×8 Bit CMOS Electrically Erasable PROM

## **FEATURES**

- Operating Temperature Range

- KM28C64A/65A: Commercial

- KM28C64AI/65AI: Industrial

- Simple Byte Write & Page Write

- Single TTL Level Write Signal

- Internal Address and Data Latch

- Automatic Internal Erase-Before-Write

- Ready/Busy Output Pin (KM28C65A)

- Fast Write Cycle Time

- 64-Byte Page Write Operation

- 5ms Byte and Page Write Cycle Time

- Complete Memory Rewrite: 0.7 seconds

- . Data-Polling and Toggle bit for End of Write Detection

- . Single 5 volt Supply

- Fast Access Time: 120ns

- Power: 100µA—Standby (max.) 40mA—Operating (max.)

- Hardware and Software Data Protection

- Reliable CMOS Floating-Gate Technology

- Endurance: 100,000 Cycle Data Retention: 10 years

- JEDEC Byte-wide Memory Pinout

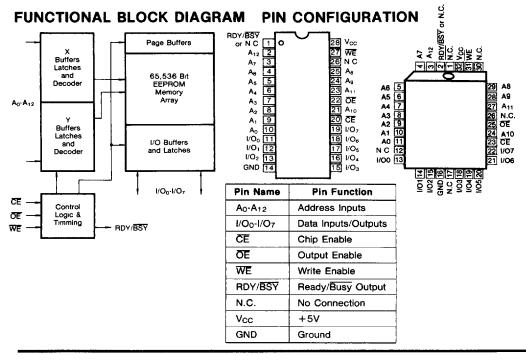

### GENERAL DESCRIPTION

The KM28C64A/65A is a 8,192X8 bit Electrically Erasable Programmable Read Only Memory. It is fabricated with the floating-gate CMOS technology using Fowler-Nordheim tunneling for erasing and programming.

Writing data into the KM28C64A/65A is very simple. The internally self-timed writing cycle latches both address and data to provide a free system bus during the 5ms write period A 64-byte page write enables an entire chip written in 0.7 seconds.

The KM28C64A/65A also features Data-polling and a Toggle bit schemes that signal the processor the early completion of a write cycle without requiring any external hardware. The KM28C65A features Read/Busy which is a hardware scheme to signal the status of the write operation and is especially useful in interrupt driven systems.

The KM28C64A/65A is designed for applications up to 100,000 write cycles per byte. It's on-chip Error Checking and Correction scheme improves the endurance to over 100,000 write cycles.

## **CMOS EEPROM**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                          |      | Symbol            | Rating       | Unit |

|------------------------------------|------|-------------------|--------------|------|

| Voltage on any pin relative to Vss |      | VIN               | -0.3 to +7.0 | V    |

| Temperature Under Bias             | Com. | т.                | -10 to +125  | °C   |

|                                    | Ind. | T <sub>bias</sub> | -65 to +150  | °C   |

| Storage Temperature                |      | T <sub>stg</sub>  | -65 to +150  | °C   |

| Short Circuit Output Current       |      | los               | 5            | mA   |

Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

KM28C64A/65A : Voltage reference to  $V_{SS}$ ,  $T_A$ =0°C to +70°C KM28C64Al/65Al : Voltage reference to  $V_{SS}$ ,  $T_A$ =-40°C to +85°C

| Parameter      | Symbol | Min | Тур | Max | Unit |

|----------------|--------|-----|-----|-----|------|

| Supply Voltage | Vcc    | 4.5 | 5.0 | 5.5 | V    |

| Supply Voltage | Vss    | 0   | 0   | 0   | V    |

#### DC OPERATING CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

| Parameter                      | Symbol           | Test Conditions                                                               | Min  | Max                   | Unit |

|--------------------------------|------------------|-------------------------------------------------------------------------------|------|-----------------------|------|

| Operating Current              | Icc              | CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> ,<br>all I/O's open (Note 1) | _    | 40                    | mA   |

| Standby Current (TTL)          | I <sub>SB1</sub> | CE = V <sub>IH</sub> , all I/O's = open                                       | _    | 1                     | mA   |

| Standby Current (CMOS)         | 1 <sub>SB2</sub> | CE = V <sub>cc</sub> - 0.2, all I/O's = open                                  | _    | 100                   | μА   |

| Input Leakage Current          | lu               | V <sub>IN</sub> = 0 to 5.5V                                                   | _    | 10                    | μΑ   |

| Output Leakage Current         | I <sub>LO</sub>  | V <sub>OUT</sub> = 0 to 5.5V                                                  | _    | 10                    | μΑ   |

| Input High Voltage, all Inputs | V <sub>IH</sub>  |                                                                               | 2.0  | V <sub>CC</sub> + 0.3 | ٧    |

| Input Low Voltage, all Inputs  | VIL              |                                                                               | -0.3 | 0.8                   | ٧    |

| Output High Voltage Level      | V <sub>OH</sub>  | $I_{OH} = -400\mu A$                                                          | 2.4  |                       | ٧    |

| Output Low Voltage Level       | VoL              | I <sub>OL</sub> = 2.1mA                                                       | _    | 0.4                   | ٧    |

| Write Inhibit V∞ Level         | Vwi              |                                                                               | 3.0  | _                     | ٧    |

Note 1: All address toggling from VIL to VIH at 8.4MHz.

## CAPACITANCE (TA=25°C, f=1.0 MHz))

| ltem                     | Symbol           | Conditions          | Min | Max | Unit |

|--------------------------|------------------|---------------------|-----|-----|------|

| Input/Output Capacitance | C <sub>1/O</sub> | V <sub>IL</sub> =0V |     | 10  | pF   |

| Input Capacitance        | CIN              | V <sub>IN</sub> =0V |     | 6   | pF   |

Note: Capacitance is periodically sampled and not 100% tested.

#### **MODE SELECTION**

| CE | ŌĒ | WE | WE Mode I/O               |                          | Power   |

|----|----|----|---------------------------|--------------------------|---------|

| L  | L  | Н  | Read                      | Dout                     | Active  |

| L  | Н  | L  | Write                     | DiN                      | Active  |

|    |    | н  | Data Polling              | $I/O_7 = \overline{D}_7$ | Active  |

| L  | L  | "  | Toggle Bit                | 1/06                     | Active  |

| н  | X  | х  | Standby and Write Inhibit | High-Z                   | Standby |

| Х  | L  | х  | Write Inhibit             | _                        | _       |

| X  | x  | н  | Write Inhibit             | _                        | _       |

# **AC CHARACTERISTICS**

KM28C64A/65A :  $T_A$ =0°C to +70°C V<sub>CC</sub>=5V±10%, unless otherwise noted KM28C64Al/65Al:  $T_A$ =-40°C to +85°C V<sub>CC</sub>=5V±10%, unless otherwise noted

#### **TEST CONDITIONS**

| Parameter                                  | Value                                |

|--------------------------------------------|--------------------------------------|

| Input Pulse Levels                         | 0.45V to 2.4V                        |

| Input Rise and Fall Times                  | 20 ns                                |

| Input and Output Timing measurement Levels | 0 8V and 2.0V                        |

| Output Load                                | 1 TTL Gate and C <sub>L</sub> =100pF |

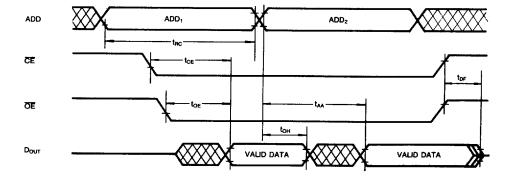

#### **READ CYCLE**

| Parameter                               | Symbol          | KM28C64A-12<br>KM28C65A-12 |     | KM28C64A-15<br>KM28C64AI-15<br>KM28C65A-15<br>KM28C65AI-15 |     | KM28C64A-20<br>KM28C64AI-20<br>KM28C65A-20<br>KM28C65AI-20 |     | KM28C64A-25<br>KM28C64AI-25<br>KM28C65A-25<br>KM28C65AI-25 |     | Unit |

|-----------------------------------------|-----------------|----------------------------|-----|------------------------------------------------------------|-----|------------------------------------------------------------|-----|------------------------------------------------------------|-----|------|

|                                         |                 | Min                        | Max | Min                                                        | Max | Min                                                        | Max | Min                                                        | Max |      |

| Read Cycle Time                         | t <sub>RC</sub> | 120                        |     | 150                                                        |     | 200                                                        |     | 250                                                        |     | ns   |

| Chip Enable Access Time                 | t <sub>CE</sub> |                            | 120 |                                                            | 150 |                                                            | 200 |                                                            | 250 | ns   |

| Address Access Time                     | t <sub>AA</sub> |                            | 120 |                                                            | 150 |                                                            | 200 |                                                            | 250 | ns   |

| Output Enable Access Time               | tos             |                            | 60  |                                                            | 80  |                                                            | 100 |                                                            | 120 | ns   |

| Output or Chip Disable to Output High-Z | t <sub>DF</sub> | 0                          | 50  | 0                                                          | 50  | 0                                                          | 50  | 0                                                          | 50  | ns   |

| Output Hold from Address Change         | t <sub>OH</sub> | 0                          |     | 0                                                          |     | 0                                                          |     | 0                                                          |     | ns   |

# **CMOS EEPROM**

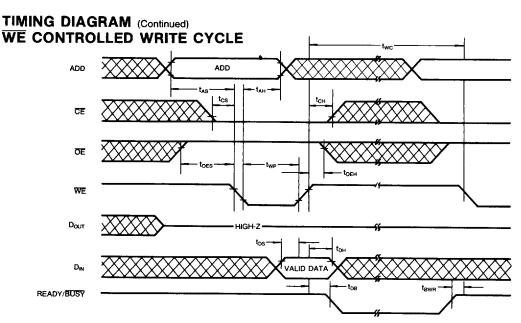

#### **WRITE CYCLE**

| Parameter                        | Symbol           | Min | Max | Unit |

|----------------------------------|------------------|-----|-----|------|

| Write Cycle Time                 | twc              |     | 5   | ms   |

| Address Set-Up Time              | tas              | 0   |     | ns   |

| Address Hold Time                | t <sub>AH</sub>  | 80  |     | ns   |

| Write Set-Up Time                | tcs              | 0   |     | ns   |

| Write Hold Time                  | tсн              | 0   |     | ns   |

| CE Pulse Width                   | tcw              | 100 |     | ns   |

| Output Enable Set-Up Time        | toes             | 10  |     | ns   |

| Output Enable Hold Time          | t <sub>OEH</sub> | 10  |     | ns   |

| WE Pulse Width                   | twp              | 100 |     | ns   |

| Data Set-Up Time                 | tos              | 50  |     | ns   |

| Data Hold Time                   | t <sub>DH</sub>  | 0   |     | ns   |

| Time to Device Busy              | t <sub>DB</sub>  |     | 100 | ns   |

| Busy to Write Recovery Time      | tawa             | 50  |     | ns   |

| Byte Load Cycle Time             | tBLC             | 0.2 | 150 | μs   |

| Last Byte Loaded to Data Polling | tLP              |     | 200 | ns   |

Note: The timer for t<sub>BLC</sub> is reset at a falling edge of WE and restarts at rising edge of WE.

# **TIMING DIAGRAM**

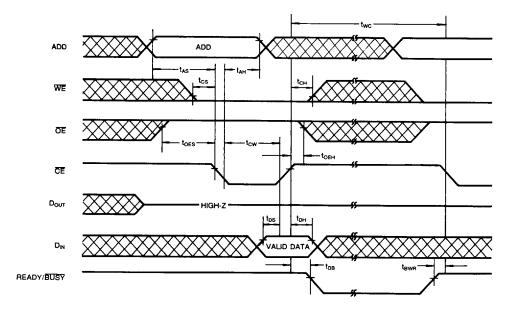

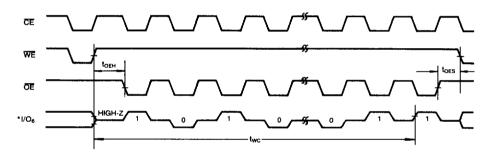

READ CYCLE (WE=VIH)

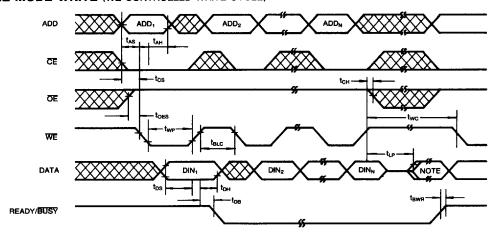

## **CE CONTROLLED WRITE CYCLE**

# **CMOS EEPROM**

# KM28C64A/KM28C65A

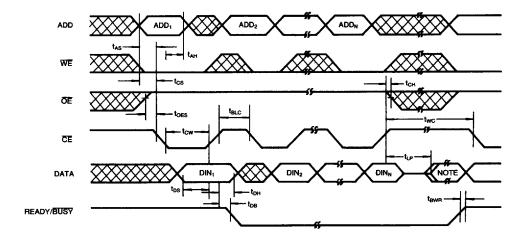

TIMING DIAGRAMS (Continued)

PAGE MODE WRITE (WE CONTROLLED WRITE CYCLE)

67E D

#### PAGE MODE WRITE (CE CONTROLLED WRITE CYCLE)

\* NOTE:  $1/O_7$  output  $\overline{DINN}$  when the chip is read.  $1/O_6$  is toggling between "1" and "0" when the chip is successively read.

# **CMOS EEPROM**

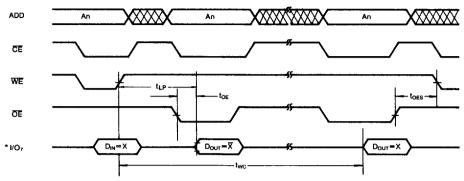

## TIMING DIAGRAMS (Continued) DATA POLLING CYCLE

\* During the write cycle, I/O<sub>7</sub> will produce an inverted data of the last I/O<sub>7</sub> data, loaded into the EEPROM

#### **TOGGLE BIT CYCLE**

\* During the write cycle, I/O6 will toggle between "1" and "0".

## CMOS EEPROM

## DEVICE OPERATION

#### READ

Reading data from the KM28C64A/65A is similar to reading data from a SRAM. A read cycle occurs when WE is high and CE and OE are low. If either CE or OE goes high the read cycle is terminated. This two line control eliminates bus contention in a system environment. The DATA I/O pins are in the high impedance state whenever OE or CE is high.

#### WRITE

Writing data into the KM28C64A/65A is easy. Only a single 5V supply and TTL level signals are required. The on-chip data latches, address latches, high voltage generator, and fully self-timed control logic make writing as easy as writing to a SRAM.

#### \*\*\*\* BYTE WRITE MODE \*\*\*\*

The byte write mode of the KM28C64A/65A is only a part of the page write mode. A single byte data loading followed by a tBLC time-out and by a nonvolitile write cycle will complete a byte mode write.

#### \*\*\*\* PAGE WRITE MODE \*\*\*\*

The KM28C64A/65A allows up to 64 bytes to be written in a single page write cycle. A page write cycle consists of a data loading period, in which from 1 to 64 bytes of data are loaded into the KM28C64A/65A internal registers and a nonvolatile write period, in which the loaded data in the registers are written to the EEPROM cells of the selected page.

Data is loaded into the KM28C64A/65A by sequentially pulsing WE with CE low and OE high. For each addressed location in the page, address is latched on the falling edge of the WE and data is latched on the rising edge of the WE. The data can be loaded in any "Y" address (A<sub>0</sub>-A<sub>5</sub>) order (i.e. data need not be loaded into consecutive locations in memory in anypage) and can be renewed in a data loading period.

Since the timer for the data loading (tBLC) is reset at the falling edge of WE and starts at every rising edge of WE, the only requirement on WE to continue loding the data is that the interval between WE pulses dose not exceed the maximum t<sub>BLC</sub> (150µs). If  $\overline{OE}$  goes low during the data loading period, further attempt to load the data will be ignored because the external WE signal is blocked by OE signal internally. Consequently, the t<sub>BLC</sub> timer is not reset by the external WE pulse if OE is low. The nonvolatile write starts if WE stays high for at least t<sub>BLC</sub> maximum (150µs) after the last WE low to high transition. The page address for the nonvolatile write is the "X" ad-

dress (A6-A12) latched on the last WE. The nonvolatile write period consists of an erase cycle and a program cycle. During the erase cycle, the existing data of the locations being addressed are erased, the new data latched at the register are written into the location during the program cycle. Note that only the addressed location in a page are rewritten during a page write cycle.

The KM28C64A/65A also supports CE controlled write cycle. That means CE can be used to latch address and data as well as WE.

#### STANDBY

Power comsumption is reduced to less than 100µA by deselecting the device with a high input on CE. Whenever CE is high, the device is in the standby mode and I/O<sub>0</sub>-I/O<sub>7</sub> are in the high impedance state, regardless of the state of OE or WE.

#### **DATA PROTECTION**

Features have been designed into the KM28C64A/65A to prevent unwanted write cycles during power supply transitions and system noise periods.

The KM28C64A/65A has a protection feature against WE noises; a WE noise the width shorter than 20ns (typ.) will not start any unwanted write cycle. Write cycles are also inhibited when V<sub>CC</sub> is less than V<sub>WI</sub>=3.0 volts, the write inhibits V<sub>CC</sub> level. During power-up, the KM28C64A/65A automatically prevents any write operation for a period of 5ms (typ.) after V<sub>CC</sub> reaches the V<sub>WI</sub> level. This will provide the system with sufficient time to bring WE and CE to a high level before a write can occur. Read cycles can be executed during this initialization period. Holding either OE low or WE high or CE high during power-on and power-off will inhibit inadvertent writes.

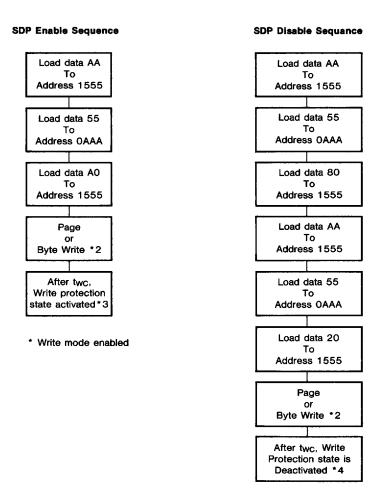

#### \*\*\*\* SOFTWARE DATA PROTECTION \*\*\*\*

The KM28C64A/65A has the JEDEC standard software data protection scheme for enhanced protection of stored data. The scheme does not affect normal write operation if it is not enabled through a SDP enable software algorithm, followed by a write or page write operation. Once the protection mode is enabled, the KM28C64A/65A will not write any data if the SDP enable software algorithm is not proceded. The data protection function can be disabled by exection a SDP disable software algorithm. Power transitions will not reset the SDP feature. All the data and address timings for the SDP enable and disable are identical to those of a page write cycle.

## **CMOS EEPROM**

## **DEVICE OPERATION** (Continued) WRITE COMPLETION INDICATORS

\*\*\* DATA POLLING \*\*\*

The KM28C64A/65A features DATA-Polling at I/O7 to detect the completion of a write cycle using a simple read and compare operation. Such a scheme dose not require any external hardware. During the write period, any attempt to read of the last byte the EEPROM will produce, at I/O7, an inverted inverted value of the last I/O7 data loaded to the EEPROM. True data will be produced at all I/O's once the write cycle has been completed

\*\*\* TOGGLE BIT \*\*\*

The KM28C64A/65A also provides toggle bit at I/O6 to determine the end of a write cycle. During the write cycle, subsequent attempts to read the EEPROM will toggle I/O6 between "1" and "0". Once the write cycle is complete, the toggling will stop and valid data will be read.

\*\*\* READY/BUSY \*\*\*

The KM28C65A has a Ready/Busy output on pin 1 that indicates when the write cycle is complete. The pin is

normally high except when a write cycle is in progress, in which case the pin is low. The Ready/Busy output is configured as an open-drain driver there-by allowing two or more Ready/Busy output to be OR-tied. This pin requires an appropriate pull-up resistor for proper operation. The pull-up resistor value maybe calculated as follows.

$$RP = \frac{V_{CC}(max) \cdot V_{OL}(max)}{I_{OL} + \Sigma I_{L}} = \frac{5.1V}{2.1 \text{mA} + \Sigma I_{L}}$$

where  $\Sigma I_L$  is the sum of the input currents of all devices tied to the Ready/Busy pin.

#### **ENDURANCE AND DATA RETENTION**

KM28C64A/65A is designed for applications requiring up to 100,000 write cycles per EEPROM byte and ten years of data retention. This means that each byte may be reliably written 100,000 times without degrading device operation. The device also featires an on-chip Error Checking and Correction scheme that can detect and correct any single bit failure in a byte, and hence, significant improvements in the endurance and data retention characteristics are achieved.

## **CMOS EEPROM**

#### SOFTWARE DATA PROTECTION ALGORITHIM\*1

Note: 1. Data Format: I/O7-I/O0 (HEX) Address Format: A12-A0 (HEX)

- 2. 1 to 64 byte of data may be loaded in random order.

- 3. Write protection state will be activated after two even if no data is writtern.

- 4. Write protection state will be deactived after.

## **CMOS EEPROM**

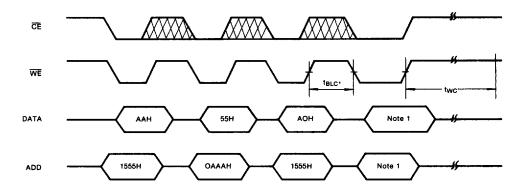

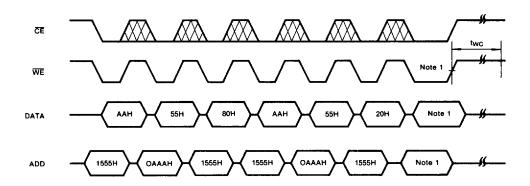

## TIMING DIAGRAM OF SOFTWARE DATA PROTECTION

### SDP ENABLE TIMING SEQUENCE

#### SDP DISABLE TIMING SEQUENCE

<sup>\* ≤</sup>t<sub>BLC</sub> max.

Note 1: 1 to 64 byte of data maybe loaded in random order.

## **CMOS EEPROM**