# MC34010

# **Advance Information**

#### **ELECTRONIC TELEPHONE CIRCUIT**

- Provides All Basic Telephone Station Apparatus Functions in a Single IC, Including DTMF Dialer, Tone Ringer, Speech Network and Line Voltage Regulator

- DTMF Generator Uses Low-Cost Ceramic Resonator with Accurate Frequency Synthesis Technique

- Tone Ringer Drives Piezoelectric Transducer and Satisfies EIA RS-470 Impedance Signature Requirements

- Speech Network Provides Two-Four Wire Conversion with Adjustable Sidetone Utilizing an Electret Transmitter

- On-Chip Regulator Insures Stable Operation Over Wide Range of Loop Lengths

- 12L Technology Provides Low 1.4 Volt Operation and High Static Discharge Immunity

- Microprocessor Interface Port for Automatic Dialing Features

# ELECTRONIC TELEPHONE CIRCUIT

BIPOLAR LINEAR/I<sup>2</sup>L

FN SUFFIX 44-PIN PLCC CASE 777

P SUFFIX PLASTIC PACKAGE CASE 711

This document contains information on a new product. Specifications and information herein are subject to change without notice.

MC34010

# MAXIMUM RATINGS (Voltage References to V-)

| Parameter                                             | Value       | Unit |

|-------------------------------------------------------|-------------|------|

| V+ Terminal Voltage (Pin 34)                          | +20, -1.0   | V    |

| VR Terminal Voltage (Pin 29)                          | +2.0, -1.0  | v    |

| RXO Terminal Voltage (Pin 27)                         | +2.0, -1.0  | V    |

| TRS Terminal Voltage (Pin 37)                         | +35, -1.0   | V    |

| TRO (With Tone Ringer Inactive) Terminal Voltage      | +2.0, -1.0  | v    |

| R1-R4 Terminal Current (Pins 1-4)<br>C1-C4 (Pins 5-8) | ± 100       | mA   |

| CL, TO, DD, I/O, A+                                   | +122, -1.0  | V    |

| Operating Ambient Temperature Range                   | -20 to +60  | °C   |

| Storage Temperature Range                             | -65 to +150 | °C   |

# **GENERAL CIRCUIT DESCRIPTION**

#### Introduction

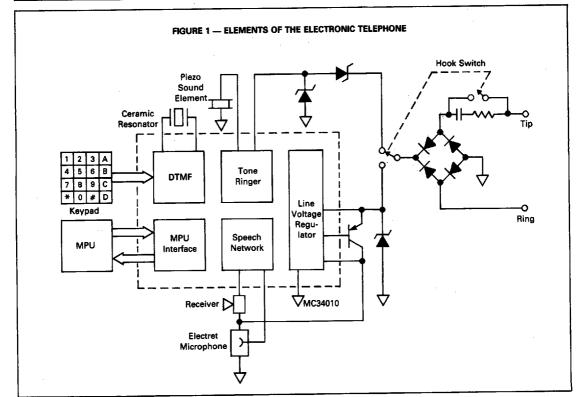

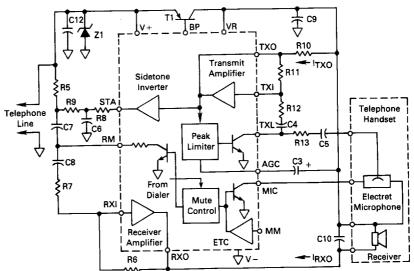

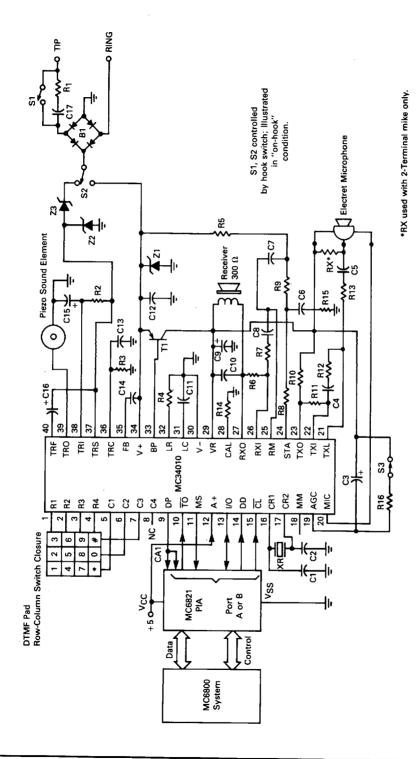

The MC34010 Electronic Telephone Circuit (ETC) provide all the necessary elements of a tone dialing telephone in a single IC. The functional blocks of the ETC include the DTMF dialer, speech network, tone ringer, and dc line interface circuit (Figure 1). The MC34010 also provides a microprocessor interface port that facilitates automatic dialing features.

Low voltage operation is a necessity for telephones in networks where parallel telephone connections are common. An electronic speech network operating in parallel with a conventional telephone may receive line voltages below 2.5 volts. DTMF dialers operate at similarly low-line voltages when signaling through battery powered station carrier equipment. These low voltage requirements have been addressed by realizing the MC34010 in a bipolar/I<sup>2</sup>L technology with appropriate circuit techniques. The resulting speech and dialer circuits maintain specified performance with instantaneous input voltage as low as 1.4 volts.

## Line Voltage Regulator

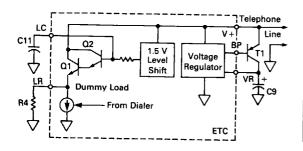

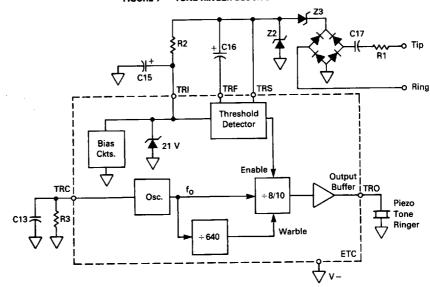

The dc line interface circuit (Figure 3) determines the dc input characteristic of the telephone. At low input voltages (less than 3 volts) the ETC draws only the

## FIGURE 3 - DC LINE INTERFACE BLOCK DIAGRAM

#### PIN CONNECTIONS

FIGURE 2 — MPU INTERFACE CODES

| Key | Row | Column | Code (B3-B0) |

|-----|-----|--------|--------------|

| 1   | 1   | 1      | 1111         |

| 2   | 1   | 2      | 0111         |

| 3   | 1   | 3      | 1011         |

| 4   | 2   | 1 1    | 1101         |

| 5   | 2   | 2      | 0101         |

| 6   | 2   | 3      | 1001         |

| 7   | 3   | 1      | 1110         |

| 8   | 3   | 2      | 0110         |

| 9   | 3   | 3      | 1010         |

| 0   | 4   | 2      | 0100         |

| Α   | 1   | 4      | 0011         |

| В   | 2   | 4      | 0001         |

| C   | 3   | 4      | 0010         |

| D   | 4   | 4      | 0000         |

| *   | 4   | 1 1    | 1100         |

| #   | 4   | 3      | 1000         |

# **GENERAL CIRCUIT DESCRIPTION** (continued)

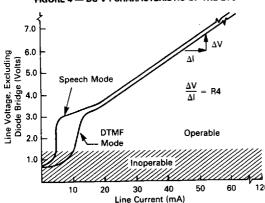

speech and dialer bias currents through the VR regulator. As input voltage increases, Q1 conducts the excess dc line current through resistor R4. The 1.5 volt level shift prevents saturation of Q2 with telephone line signals up to 2.0 volts peak (+5.2 dBm). A constant current (dummy load) is switched off when the DTMF dialer is activated to reduce line current transients. Figure 4 illustrates the dc voltage/current characteristic of an MC34010 telephone.

FIGURE 4 — DC V-I CHARACTERISTIC OF THE ETC

#### Speech Network

The speech network (Figure 5) provides the two-tofour wire interface between the telephone line and the instrument's transmitter and receiver. An electret microphone biased from VR drives the transmit amplifier. For very loud talkers, the peak limiter circuit reduces the transmit input level to maintain low distortion. The transmit amplifier output signal is inverted at the STA terminal and driven through an external R-C network to control the receiver sidetone level. The switched ac resistance at the RM terminal reduces receiver signal when dialing and suppresses clicks due to hook or keypad switch transitions. When transmitting, audio signal currents (iTXO and iRXO) flow through the voltage regulator pass transistor (T1) to drive the telephone line. This feature has two consequences: 1) In the transmitting mode the receiver sidetone current iRXO contributes to the total signal on the line along with iTXO; 2) The ac impedance of the telephone is determined by the receiver impedance and the voltage gain from the line to the receiver amplifier output.

#### **DTMF Dialer**

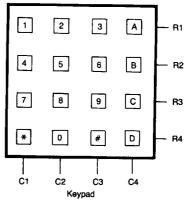

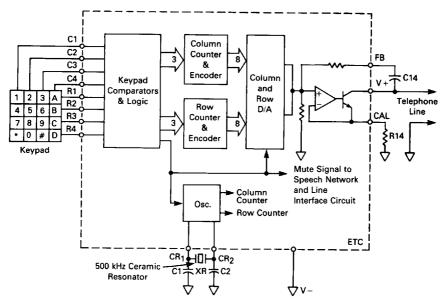

Keypad interface comparators activate the DTMF row and column tone generators (Figure 6) when a row and column input are connected through a SPST keypad. The keypad interface is designed to function with contact resistances up to 1.0 k $\Omega$  and leakage resistances as low as 150 k $\Omega$ . Single tones may be initiated by depressing two keys in the same row or column.

The programmable counters employ a novel design to produce non-integer frequency ratios. The various DTMF tones are synthesized with frequency division errors less than  $\pm 0.16\%$  (Table 1). Consequently an inexpensive ceramic resonator can be used instead of a quartz crystal as the DTMF frequency reference. Total

frequency error less than  $\pm 0.8\%$  can be achieved with  $\pm 0.3\%$  ceramic resonator. The row and column D/A converters produce 16-step approximations of sinusoidal waveforms. Feedback through terminal FB reduces the DTMF output impedance to approximately 2.0 k $\Omega$  to satisfy return loss specifications.

FIGURE 6 — DTMF DIALER BLOCK DIAGRAM

#### **Tone Ringer**

The tone ringer (Figure 7) generates a warbling square wave output drive to a piezo sound element when the ac line voltage exceeds a predetermined threshold level. The threshold detector uses a current mode comparator to prevent on/off chatter when the output current reduces the voltage available at the ringer input. When the average current into the tone ringer exceeds the threshold level, the ringer output TRO commences driving the piezo transducer. This output current sourced from TRI increases the average current measured by the threshold detector. As a result, hysteresis is produced beween the tone ringer on and off thresholds. The output frequency at TRO alternates between  $f_{\rm O}/8$  and  $f_{\rm O}/10$  at a warble rate of  $f_{\rm O}/640$ , where  $f_{\rm O}$  is the ringer oscillator frequency.

#### Microprocessor Interface

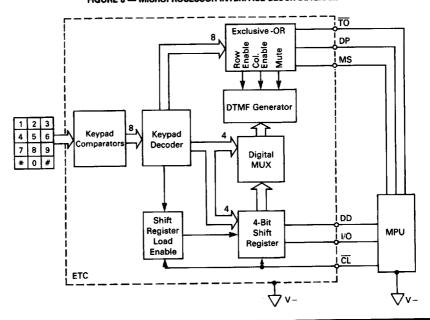

The MPU interface connects the keypad and DTMF sections of the ETC to a microprocessor for storing and retrieving numbers to be dialed. Figure 8 shows the major blocks of the MPU interface section and the interconnections between the keypad interface, DTMF generator and microprocessor. Each button of a 12 or 16 number keypad is represented by a four-bit code (Figure 2). This four-bit code is used to load the programmable counters to generate the appropriate row and column tones. The code is transferred serially to or from the microprocessor when the shift register is

clocked by the microprocessor. Data is transferred through the I/O terminal, and the direction of data flow is determined by the Data Direction (DD) input terminal. In the manual dialing mode, DD is a Logic "0" and the four-bit code from the keypad is fed to the DTMF generator by the digital multiplexer and also output on the I/O terminal through the four-bit shift register. The data sequence on the I/O terminal is B3, B2, B1, B0 and is transferred on the negative edge of the clock input ( $\overline{\text{CL}}$ ). In this mode the shift register load enable circuit cycles the register between the load and read modes such that multiple read cycles may be run for a single-key closure. Six complete clock cycles are required to output data from the ETC and reload the register for a second look.

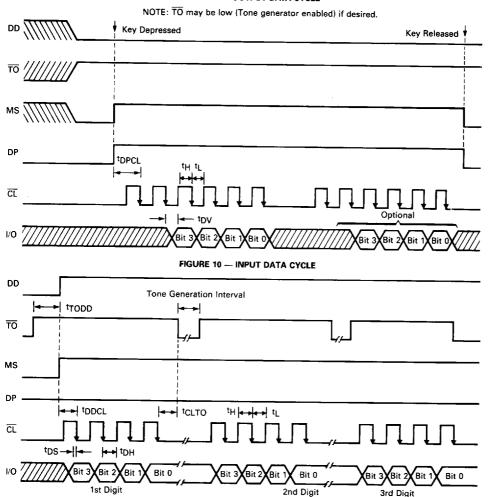

In the automatic dialing mode, DD is a Logic "1" and the four-bit code is serially entered in the sequence B3, B2, B1, B0 into the four-bit shift register. Thus, only four clock cycles are required to transfer a number into the ETC. The keypad is disabled in this mode. A Logic "1" on the Tone Output  $(\overline{10})$  will disable tone outputs until valid data from the microprocessor is in place. Subsequently  $\overline{10}$  is switched to a Logic "0" to enable the DTMF generator. Figures 9 and 10 show the timing waveforms for the manual and automatic dialing modes and Table 2 specifies timing limitations.

The keypad decoder's exclusive OR circuit generates the DP and MS output signals. The DP output indicates (when at a Logic "1") that one, and only one, key is

depressed, thereby indicating valid data is available to the MPU. The DP output can additionally be used to initiate a data transfer sequence to the microprocessor. The MS output (when at a Logic "1") indicates the DTMF generator is enabled and the speech network is muted.

Pin A+ is to be connected to a source of 2.5 to 10 volts (generally from the microprocessor circuit) to enable the pullup circuits on the microprocessor interface outputs (DP, MS, I/O). Additionally, this voltage will

power the entire circuitry (except Tone Ringer) in the absence of voltage at V+. This permits use of the transmit and receive amplifiers, keypad interface, and DTMF generator for non-typical telephone functions.

See Figure 45 for a typical interconnection to an MC6821 PIA (Peripheral Interface Adapter). Connection to a port on any other class of microprocessor will be similar.

FIGURE 7 — TONE RINGER BLOCK DIAGRAM

FIGURE 8 — MICROPROCESSOR INTERFACE BLOCK DIAGRAM

# FIGURE 9 — OUTPUT DATA CYCLE

TABLE 1 -- FREQUENCY SYNTHESIZER ERRORS

|          | DTMF<br>Standard<br>(Hz) | Tone Output<br>Frequency with<br>500 kHz Oscillator | % Deviation from Standard |

|----------|--------------------------|-----------------------------------------------------|---------------------------|

| Row 1    | 697                      | 696.4                                               | - 0.086                   |

| Row 2    | 770                      | 769.2                                               | -0.104                    |

| Row 3    | 852                      | 853.2                                               | +0.141                    |

| Row 4    | 941                      | 939.8                                               | -0.128                    |

| Column 1 | 1209                     | 1207.7                                              | -0.108                    |

| Column 2 | 1336                     | 1336.9                                              | + 0.067                   |

| Column 3 | 1477                     | 1479.3                                              | + 0.156                   |

| Column 4 | 1633                     | 1634.0                                              | +0.061                    |

**TABLE 2 — TIMING LIMITATIONS**

| Symbol                         | Parameter                                     | Min | Тур | Max | Unit | Ref           |

|--------------------------------|-----------------------------------------------|-----|-----|-----|------|---------------|

| fCL                            | Clock Frequency                               | 0   | 20  | 30  | kHz  |               |

| tн                             | Clock High Time                               | 15  | _   | -   | μS   | Figs.<br>9,10 |

| tL                             | Clock Low Time                                | 15  | _   | -   | μs   | Figs.<br>9,10 |

| t <sub>r</sub> ,t <sub>f</sub> | Clock Rise, Fall Time                         | _   | _   | 2.0 | μs   |               |

| †DV                            | Clock Transition to<br>Data Valid             | -   | _   | 10  | μs   | Fig. 9        |

| †DPCL                          | Time from DP High to CL Low                   | 20  | _   | -   | μs   | Fig. 9        |

| †DDCL                          | Time from DD High<br>to CL Low                | 20  | _   | -   | μs   | Fig. 10       |

| tDS                            | Data Setup Time                               | 10  | _   | _   | μs   | Fig. 10       |

| †DH                            | Data Hold Time                                | 10  | _   |     | μs   | Fig. 10       |

| †CLTO                          | Time from CL Low                              | 10  | _   | -   | μs   | Fig. 10       |

| tTODD                          | to TO Low_<br>Time from TO High<br>to DD High | 20  | _   | 1   | μ\$  | Fig. 10       |

# PIN DESCRIPTION

(See Figure 45 for external component identifications.)

| PIN<br>(PLCC) | PIN<br>(DIP) | Designation | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–4           | 1-4          | R1-R4       | Keypad inputs for Rows 1 through 4. When open, internal 8.0 k $\Omega$ resistors pull up the row inputs to a regulated ( $\approx$ 0.5 volt) supply. In normal operation, a row and a column input are connected through a SPST switch by the telephone keypad. Row inputs can also be activated by a Logic "0" (<250 mV) from a microprocessor port.                                                                                                                   |

| 7–10          | 58           | C1-C4       | Keypad inputs for Columns 1 through 4. When open, internal 8.0 k $\Omega$ resistors pull down the column inputs to V $-$ . In normal operation, connecting any column input to any row input produces the respective row and column DTMF tones. In addition to being connected to a row input, column inputs can be activated by a Logic "1" (>250 mV and <1.0 volt).                                                                                                   |

| 11            | 9            | DP          | Depressed Pushbutton (Output) — Normally low; A Logic "1" indicates one and only one, button of the DTMF keypad is depressed.                                                                                                                                                                                                                                                                                                                                           |

| 12            | 10           | TO          | Tone Output (Input) — When a Logic "1," disables the DTMF generator. Keypad is not disabled.                                                                                                                                                                                                                                                                                                                                                                            |

| 13            | 11           | MS          | Mute/Single Tone (Output) — A Logic "1" indicates the tone generator is enabled. A Logic "0" indicates tone generator is disabled.                                                                                                                                                                                                                                                                                                                                      |

| 14            | 12           | A+          | MPU Power Supply (Input) — Enables pullups on the microprocessor section outputs. Additionally, this voltage will power the entire circuit (except Tone Ringer) in the absence of voltage at V+.                                                                                                                                                                                                                                                                        |

| 15            | 13           | I/O         | Input/Output — Serial Input or Output data (determined by DD input) to or from the microprocessor for storing or retrieving telephone numbers. Guaranteed to be a Logic "1" on powerup if DD = Logic "0."                                                                                                                                                                                                                                                               |

| 16            | 14           | DD          | Data Direction (Input) — Determines direction of data flow through I/O pin. As a Logic "1," I/O is an input to the DTMF generator. As a Logic "0," I/O outputs keypad entries to the microprocessor.                                                                                                                                                                                                                                                                    |

| 17            | 15           | CL          | Clock (Input) — Serially shifts data in or out of I/O pin. Data is transferred on negative edge typically at 20 kHz.                                                                                                                                                                                                                                                                                                                                                    |

| 18,19         | 16,17        | CR1, CR2    | Ceramic Resonator oscillator input and feedback terminals, respectively. The DTMF dialer is intended to operate with a 500 kHz ceramic resonator from which row and column tones are synthesized.                                                                                                                                                                                                                                                                       |

| 31            | 28           | CAL         | Amplitude CALibration terminal for DTMF dialer. Resistor R14 from the CAL pin to V – controls the DTMF output signal level at Tip and Ring.                                                                                                                                                                                                                                                                                                                             |

| 38            | 35           | FB          | FeedBack terminal for DTMF output. Capacitor C14 connected from FB to V+ provides ac feedback to reduce the output impedance to Tip and Ring when tone dialing.                                                                                                                                                                                                                                                                                                         |

| 32            | 29           | VR          | Voltage Regulator output terminal. VR is the output of a 1.1 volt voltage regulator which supplies power to the speech network amplifiers and DTMF generator during signaling. To improve regulator efficiency at low line current conditions, an external PNP pass-transistor T1 is used in the regulator circuit. Capacitor C9 frequency compensates the VR regulator to prevent oscillation.                                                                         |

| 36            | 33           | BP          | Base of a PNP Pass-transistor. Under long-loop conditions where low line voltages would cause VR to fall below 1.1 volts, BP drives the PNP transistor T1 into saturation, thereby minimizing the voltage drop across the pass transistor. At line voltages which maintain VR above 1.1 volts, BP biases T1 in the linear region thereby regulating the VR voltage. Transistor T1 also couples the ac speech signals from the transmit amplifier to Tip and Ring at V+. |

| 37            | 34           | V+          | The more positive input to the regulator, speech, and DTMF sections connected to Tip and Ring through the polarity guard diode bridge.                                                                                                                                                                                                                                                                                                                                  |

| 33            | 30           | V-          | The dc common (more negative input) connected to Tip and Ring through the polarity guard bridge.                                                                                                                                                                                                                                                                                                                                                                        |

| 35            | 32           | LR          | DC Load Resistor. Resistor R4 from LR to V — determines the dc input resistance at Tip and Ring. This resistor is external not only to enable programming the dc resistance but also to avoid high on-chip power dissipation with short telephone lines. It acts as a shunt load conducting the excess dc line current. At low line voltages (<3.0 volts), no current flows through LR.                                                                                 |

| 34            | 31           | LC          | DC Load Capacitor. Capacitor C11 from LC to V – forms a low-pass filter which prevents the resistor at LR from loading ac speech and DTMF signals.                                                                                                                                                                                                                                                                                                                      |

| 22            | 20           | MIC         | MICrophone negative supply terminal. The dc current from the electret microphone is returned to V – through the MIC terminal which is connected to the collector of an on-chip NPN transistor. The base of this transistor is controlled either internally by the mute signal from the DTMF generator, or externally by the logic input pin MM.                                                                                                                         |

(continued)

# PIN DESCRIPTION (continued)

| PIN<br>(PLCC) | PIN<br>(DIP) | Designation | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20            | 18           | ММ          | Microphone Mute. The MM pin provides a means to mute the microphone in response to a digital control signal. When this pin is connected to a Logic "1" (>2.0 V) the microphone do return path through the MIC terminal is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 25            | 22           | TXI         | Transmit amplifier Input. TXI is the input to the transmit amplifier from an electret microphone. AC coupling capacitors allow the dc offset at TXI to be maintained approximately 0.6 V above V - by feedback through resistor R11 from TXO.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24            | 21           | TXL         | Transmit Input Limiter. An internal variable resistance element at the TXL terminal controls the transmitter input level to prevent clipping with high signal levels. Coupling capacitors C4 and C5 prevent dc current flow through TXL. The dynamic range of the transmit peak limiter is controlled by resistors R12 and R13.                                                                                                                                                                                                                                                                                                                        |

| 26            | 23           | тхо         | Transmit Amplifier Output. The transmit amplifier output drives ac current through the voltage regulator pass-transistor T1 via resistor R10. The dc bias voltage at TXO is typically 0.6 volts above V – . The transmit amplifier gain is controlled by the R11/R12 + R13 ratio.                                                                                                                                                                                                                                                                                                                                                                      |

| 21            | 19           | AGC         | Automatic Gain Control low-pass filter terminal. Capacitor C3 connected between AGC and VR sets the attack and decay time of the transmit limiter circuit. This capacitor also aids in reducing clicks in the receiver due to hook-switch transients and DTMF on/off transients. In conjunction with internal resistors, C3 (1.0 $\mu$ F) forms a timer which mutes the receiver amplifier for approximately 20 milliseconds after the user goes off-hook or releases a DTMF Key.                                                                                                                                                                      |

| 30            | 27           | RXO         | Receiver Amplifier Output. This terminal is connected to the open-collector NPN output transistor of the receiver amplifier. DC bias current for the output device is sourced through the receiver from VR. The bias voltage at RXO is typically 0.6 volts above the V – Capacitor C10 from RXO to VR provides frequency compensation for the receiver amplifier.                                                                                                                                                                                                                                                                                      |

| 29            | 26           | RXI         | Receiver Amplifier Input. RXI is the input terminal of the receiver amplifier which is driven by ac signals from $V+$ and STA. Input coupling capacitor C8 allows RXI to be biased approximately 0.6 volts above the $V-$ via feedback resistor R6.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28            | 25           | RM          | Receiver Amplifier Mute. A switched resistance at the RM terminal attenuates the receiver amplifier input signal produced by DTMF dialing tones at V + . RM also mutes clicks at the receiver which result from keypad or hook switch transitions. The ac resistance at RM is typically 540 $\Omega$ in the mute mode and 200 $k\Omega$ otherwise. Coupling capacitors C7 and C8 prevent dc current flow through RM.                                                                                                                                                                                                                                   |

| 27            | 24           | STA         | SideTone Amplifier output. STA is the output of the sidetone inverter amplifier whose input is driven by the transmit signal at TXO. The inverted transmit signal from STA subtracts from the receiver amplifier input current from V+, thus reducing the receiver sidetone level. Since the transmitted signal at V+ is phase shifted with respect to TXO by the reactive impedance of the phone line, the signal from STA must be similarly phase-shifted in order to provide adequate sidetone reduction. This phase relationship between the transmit signal at TXO and the sidetone cancellation signal from STA is controlled by R8, R9, and C6. |

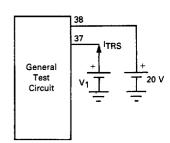

| 41            | 37           | TRS         | Tone Ringer Input Sense. TRS is the most positive input terminal of the tone ringer and the reference for the threshold detector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 42            | 38           | TRI         | Tone Ringer Input terminal. TRI is the positive supply voltage terminal for tone ringer circuitry.<br>Current is supplied to TRI through resistor R2. When the average voltage across R2 exceeds an<br>internal reference voltage (typically 1.6 volts) the tone ringer output is enabled.                                                                                                                                                                                                                                                                                                                                                             |

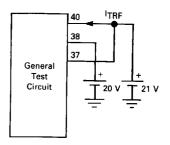

| 44            | 40           | TRF         | Tone Ringer Input Filter capacitor terminal. Capacitor C16 connected from TRF to TRS forms a low-pass filter. This filter averages the signal across resistor R2 and presents this dc voltage to the input of the threshold detector. Line voltage transients are rejected if the duration is insufficient to charge C16 to 1.6 volts.                                                                                                                                                                                                                                                                                                                 |

|               | 36           | TRC         | Tone Ringer oscillator Capacitor and resistor terminal. The relaxation oscillator frequency $f_0$ is set by resistor R3 and capacitor C13 connected from TRC to V – . Typically, $f_0 = (R3C13 + 8.0 \mu s)^{-1}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                    |

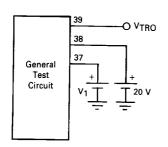

| 13            | 39           | TRO         | Tone Ringer Output terminal. The frequency of the square wave output signal at TRO alternates from f <sub>0</sub> /8 to f <sub>0</sub> /10 at a warble rate of f <sub>0</sub> /640. Typical output frequencies are 1000 Hz and 800 Hz with a 12.5 Hz warble rate. TRO sources or sinks up to 20 mA to produce an output voltage swing of 18 volts peak-to-peak across the piezo transducer. Tone ringer volume control can be implemented by a variable resistor in series with the piezo transducer.                                                                                                                                                  |

# ELECTRICAL CHARACTERISTICS (TA = 25°C)

## KEYPAD INTERFACE CIRCUIT

| Ob an administra                                                                                                             | Test<br>Method | Symbol           | Min                   | Тур | Max                   | Unit |

|------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------------|-----|-----------------------|------|

| Characteristic  Row Input Pullup Resistance mth Row Terminal: m = 1,2,3,4                                                    | 7              | RRm              | 4.0                   | 8.0 | 11                    | kΩ   |

| Column Input Pulldown Resistance nth Column Terminal: n = 1,2,3,4                                                            | 8              | R <sub>Cn</sub>  | 4.0                   | 8.0 | 11                    | kΩ   |

| Ratio of Row-to-Column Input Resistances $K_{m,n} = \begin{array}{c} R_{Rm}, & m=1,2,3,4 \\ R_{Cn}, & n=1,2,3,4 \end{array}$ | 7 & 8          | K <sub>m,n</sub> | 0.88                  | 1.0 | 1.12                  |      |

| Row Terminal Open Circuit Voltage                                                                                            | 7a             | VROC             | 280                   | 380 | 500                   | mVdc |

| Row Threshold Voltage for mth Row Terminal: m = 1,2,3,4                                                                      | 9              | V <sub>Rm</sub>  | 0.70 V <sub>ROC</sub> |     |                       | Vdc  |

| Column Threshold Voltage for nth Column Terminal: n = 1,2,3,4                                                                | 10             | V <sub>Cn</sub>  |                       | _   | 0.39 V <sub>ROC</sub> | Vdc  |

# MICROPROCESSOR INTERFACE

| MICROPROCESSOR INTERFACE                 |     | V=                  | 0.95 | 1.1 | 1.3        | V  |

|------------------------------------------|-----|---------------------|------|-----|------------|----|

| Voltage Regulator Output<br>A+ Regulator | 29  | V <sub>R/A+</sub>   | 0.95 | 1.1 | 1.0        |    |

| A + Input Current Off-Hook               | 28a | IA(off)             | 300  | 500 | 700        | μΑ |

| A + Input Current On-Hook                | 28b | I <sub>A</sub> (on) | 4.0  | 6.0 | 9.0        | mA |

| Input Resistance (DD, TO, CL)            | 30  | Rin                 | 50   | 100 | 150        | kΩ |

| Input Current (I/O)                      | 31  | lin                 |      | 80  | 200        | μΑ |

| Input High Voltage (DD, TO, CL, I/O)     |     | VIH                 | 2.0  | _   | <b>A</b> + | V  |

| Input Low Voltage (DD, TO, CL, I/O)      | _   | VIL                 |      |     | 0.8        | V  |

| Output High Voltage (MS, DP, I/O)        | 32  | Voн                 | 2.4  | 4.0 |            | V  |

| Output Low Voltage (MS, DP, I/O)         | 33  | VOL                 |      | 0.1 | 0.4        | V  |

# LINE VOLTAGE REGULATOR

| Voltage Regulator Output                                                                     | 1a       | V <sub>R</sub>   | 1.0        | 1.1        | 1.2        | Volts |

|----------------------------------------------------------------------------------------------|----------|------------------|------------|------------|------------|-------|

| V+ Current in DTMF Mode                                                                      | 2a       | IDT              | 8.0        | 12         | 14         | mA    |

| Change in IpT with Change in V+ Voltage                                                      | 2b       | ΔΙDΤ             | _          | 0.8        | 2.0        | mA    |

| V+ Current in Speech Mode V+ = 1.7 V V+ = 5.0 V                                              | 1b<br>1c | ISP              | 3.5<br>8.0 | 5.0<br>11  | 7.0<br>15  | mA    |

| Speech to DTMF Mode Current Difference                                                       | 3        | ΔITR             | -2.0       | 2.0        | 3.5        | mA    |

| LR Level Shift<br>V+ = 5.0 V, I <sub>LR</sub> = 10 mA<br>V+ = 18 V, I <sub>LR</sub> = 110 mA | 4a<br>4b | ΔV <sub>LR</sub> | 2.5<br>2.8 | 2.9<br>3.3 | 3.5<br>4.0 | Vdc   |

| LC Terminal Resistance                                                                       | 5        | RLC              | 30         | 50         | 75         | kΩ    |

| Load Regulation                                                                              | 6        | ΔVR              | - 20       | -6.0       | 20         | mVdc  |

# **ELECTRICAL CHARACTERISTICS** (continued)

# SPEECH NETWORK

| Characteristic                      | Test<br>Method | Symbol                 | Min  | Тур  | Max  | Unit |

|-------------------------------------|----------------|------------------------|------|------|------|------|

| MIC Terminal Saturation Voltage     | 20             | VMIC                   |      | 60   | 125  | mVdc |

| MIC Terminal Leakage Current        | 21a            | MIC                    |      | 0.0  | 12.0 | μΑ   |

| MM Terminal Input Resistance        | 21b            | RMM                    | 50   | 100  | 170  | kΩ   |

| TXO Terminal Bias                   | 22a            | BTXO                   | 0.46 | 0.53 | 0.62 |      |

| TXI Terminal Input Bias Current     | 22b            | IXI                    |      | 50   | 250  | nA   |

| TXO Terminal Positive Swing         | 22c            | V <sub>TXO</sub> (+)   | _    | 25   | 60   | mVdc |

| TXO Terminal Negative Swing         | 22d            | V <sub>TXO</sub> (-)   | _    | 130  | 200  | mVdc |

| Transmit Amplifier Closed-Loop Gain | 23a            | GTX                    | 16.5 | 19   | 20   | V/V  |

| Sidetone Amplifier Gain             | 23b            | GSTA                   | 0.41 | 0.45 | 0.55 | V/V  |

| STA Terminal Output Current         | 24             | ISTA                   | 50   | 100  | 250  | μА   |

| RXO Terminal Bias                   | 25a            | B <sub>RXO</sub>       | 0.46 | 0.62 | 0.62 |      |

| RXI Terminal Input Bias Current     | 25b            | IRXI                   |      | 100  | 400  | пA   |

| RXO Terminal Positive Swing         | 25c            | V <sub>RXO</sub> (+)   | _    | 1.0  | 20   | mVdc |

| RXO Terminal Negative Swing         | 25d            | V <sub>RXO</sub> (-)   |      | 40   | 100  | mVdc |

| TXL Terminal OFF Resistance         | 26a            | R <sub>TXL</sub> (OFF) | 125  | 200  | 300  | kΩ   |

| TXL Terminal ON Resistance          | 26b            | R <sub>TXL</sub> (ON)  |      | 20   | 100  | Ω    |

| RM Terminal OFF Resistance          | 27a            | R <sub>BM</sub> (OFF)  | 125  | 180  | 300  | kΩ   |

| RM Terminal ON Resistance           | 27b            | R <sub>RM</sub> (ON)   | 410  | 570  | 770  | Ω    |

#### DTMF GENERATOR

| Row Tone Frequency       | Row 1<br>Row 2<br>Row 3<br>Row 4             | 11a, 11b | fRm              | 692.9<br>765.3<br>848.9<br>935.1     | 696.4<br>769.2<br>853.2<br>939.8     | 699.9<br>773.0<br>857.5<br>944.5     | Hz               |

|--------------------------|----------------------------------------------|----------|------------------|--------------------------------------|--------------------------------------|--------------------------------------|------------------|

| Column Tone Frequency    | Column 1<br>Column 2<br>Column 3<br>Column 4 | 11c, 11d | f <sub>Cn</sub>  | 1201.6<br>1330.2<br>1471.9<br>1625.2 | 1207.7<br>1336.9<br>1479.3<br>1633.4 | 1213.7<br>1343.6<br>1486.7<br>1641.5 | Hz               |

| Row Tone Amplitude       |                                              | 11e      | VRow             | 0.34                                 | 0.39                                 | 0.50                                 | V <sub>rms</sub> |

| Column Tone Amplitude    |                                              | 11f      | V <sub>Col</sub> | 0.43                                 | 0.48                                 | 0.62                                 | V <sub>rms</sub> |

| Column Tone Pre-emphasis | s                                            | 11g      | dB <sub>CR</sub> | 0.5                                  | 1.8                                  | 3.0                                  | dB               |

| DTMF Distortion          |                                              | 12       | % Dis            | _                                    | 4.0                                  | 6.0                                  | %                |

| DTMF Output Resistance   |                                              | 13       | Ro               | 1.0                                  | 2.5                                  | 3.0                                  | kΩ               |

#### **ELECTRICAL CHARACTERISTICS** (continued)

#### **TONE RINGER**

| Characteristic                                             | Test<br>Method | Symbol              | Min       | Тур        | Max        | Unit     |

|------------------------------------------------------------|----------------|---------------------|-----------|------------|------------|----------|

| TRI Terminal Voltage                                       | 14             | VTRI                | 20        | 21.5       | 23         | . Vdc    |

| TRS Terminal Input Current VTRS = 24 volts VTRS = 30 volts | 15a<br>15b     | ITRS                | 70<br>0.4 | 120<br>0.8 | 170<br>1.5 | μA<br>mA |

| TRF Threshold Voltage                                      | 16a            | VTRF                | 1.2       | 1.6        | 1.9        | Vdc      |

| TRF Threshold Hysteresis                                   | 16b            | ΔVTRF               | 100       | 200        | 400        | mVdc     |

| TRF Filter Resistance                                      | 17.            | RTRF                | 30        | 50         | 75         | kΩ       |

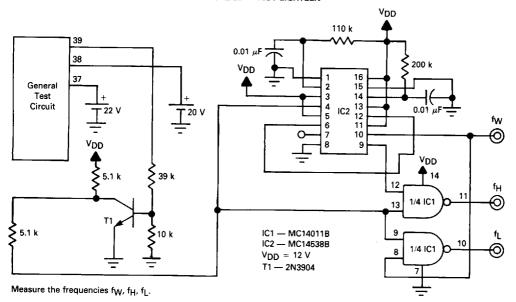

| High Tone Frequency                                        | 18             | fH                  | 920       | 1000       | 1080       | Hz       |

| Low Tone Frequency                                         | 18             | fL                  | 736       | 800        | 864        | Hz       |

| Warble Frequency                                           | 18 .           | fw                  | 11.5      | 12.5       | 13.5       | Hz       |

| Tone Ringer Output Voltage                                 | 19             | V <sub>o(p-p)</sub> | 18        | 20         | 22         | Vp-p     |

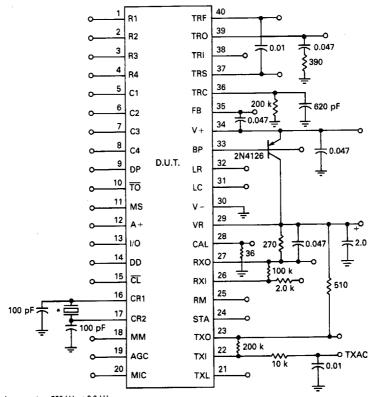

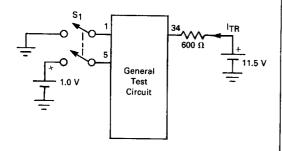

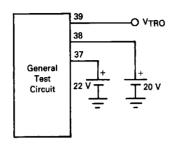

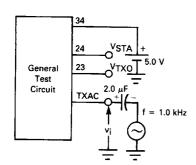

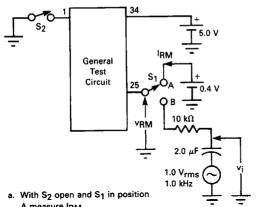

#### FIGURE 11 -- GENERAL TEST CIRCUIT

#### Notes:

- 1. \*Selected ceramic resonator: 500 kHz ± 2.0 kHz.

- Capacitances in μF unless noted.

- 3. All resistances in ohms.

- 4. Pin outs shown are for the 40 pin DIP.

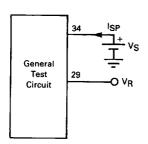

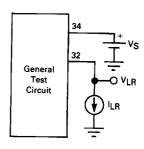

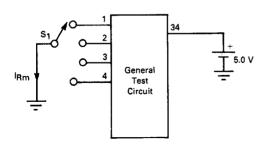

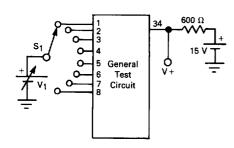

## FIGURE 12 — TEST ONE

- a. Measure  $V_R$  with  $V_S = 1.7 V$

- b. Measure ISP with  $V_S = 1.7 \text{ V}$

- c. Measure ISP with  $V_S = 5.0 \text{ V}$

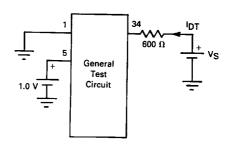

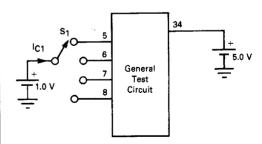

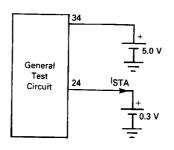

# FIGURE 13 — TEST TWO

- a. Measure  $I_{DT}$  with  $V_S = 11.5 \text{ V}$

- b. Measure IDT with  $V_S = 26$  V. Calculate  $\Delta IDT = IDT = IDT = IDT$

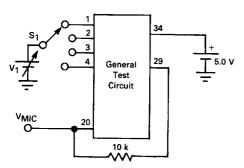

# FIGURE 14 — TEST THREE

# With $S_{1}$ open measure $I_{\mbox{\scriptsize TR}}.$ Close $S_{1}$ and again measure $I_{\mbox{\scriptsize TR}}.$ Calculate:

$$\begin{array}{c|c} \Delta I_{TR} = I_{TR} & - & I_{TR} \\ S_1 & S_1 \\ & Closed & Open \end{array}$$

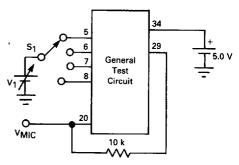

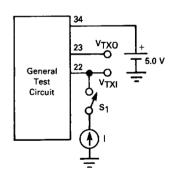

#### FIGURE 15 - TEST FOUR

- a. Set V  $_S=5.0$  V and I  $_{LR}=$  10 mA. Measure V  $_{LR}.$  Calculate  $\Delta V_{LR}=$  V  $_S-$  V  $_{LR}$

- b. Repeat Test 4a with  $V_S = 18 \text{ V}$  and  $I_{LR} = 110 \text{ mA}$

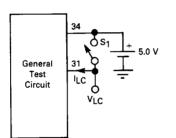

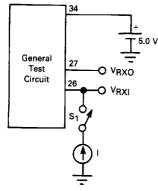

#### FIGURE 17 — TEST SIX

With S<sub>1</sub> open measure V<sub>LC</sub>. Close S<sub>1</sub> and measure I<sub>LC</sub>. Calculate:

$$R_{LC} = \frac{5.0 - V_{LC}}{^{\frac{3}{2}} LC}$$

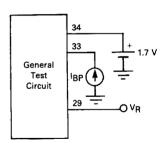

Set IBP = 0.0  $\mu$ A and measure V<sub>R</sub>. Set IBP = 150  $\mu$ A and measure V<sub>R</sub>. Calculate:  $\Delta V_R = V_R \left| \begin{array}{cc} & & V_R \\ & & 0.0 & \mu A \end{array} \right| \ \ 150 \ \mu$

#### FIGURE 18 — TEST SEVEN

Subscript m corresponds to row number.

# FIGURE 19 — TEST EIGHT

Subscript n corresponds to column number.

- a. Set S<sub>1</sub> to Terminal 2 and measure voltage at Terminal 1 (VROC).

- b. Set  $S_1$  to Terminal 1 (m = 1) and measure  $I_{R1}.$  Calculate:  $R_{R1} = V_{ROC} \div \ I_{R1}$

c,d,e. Repeat Test 7b for m = 2,3,4.

a. Set  $S_1$  to Terminal 5 (n = 1) and measure  $I_{C1}.$  Calculate:  $R_{C1}$  = 1.0 V  $\div$   $I_{C1}$

b.c.d. Repeat Test 8a for n = 2,3,4.

#### FIGURE 20 — TEST NINE

m corresponds to row number.

a. Set S<sub>1</sub> to Terminal 1 (m = 1) with V<sub>1</sub> = 1.0 Vdc. Verify V<sub>MIC</sub> is Low (V<sub>MIC</sub> < 0.3 Vdc). Decrease V<sub>1</sub> to 0.70 V<sub>ROC</sub> and verify V<sub>MIC</sub> switches high. (V<sub>MIC</sub> > 0.5 Vdc). V<sub>ROC</sub> is obtained from Test 7a.

b,c,d. Repeat Test 9a for rows 2,3, and 4. (m = 2,3,4)

#### FIGURE 21 - TEST TEN

n corresponds to column number.

a. Set S<sub>1</sub> to Terminal 5 (n = 1) with V<sub>1</sub> = 0 Vdc. Verify VMIC is low (VMIC < 0.3 Vdc). Increase V<sub>1</sub> to 0.39 VROC and verify VMIC switches high, (VMIC > 0.5 Vdc). VROC is obtained from Test 7a.

b,c,d. Repeat Test 10a for columns 2,3, and 4. (n = 2,3,4)

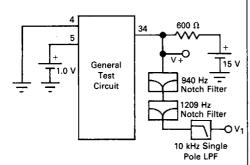

#### FIGURE 22 — TEST ELEVEN

m corresponds to row number. n corresponds to column number.

- a. With  $V_1=0.0~V$  set  $S_1$  to Terminal 1 (m = 1) and measure frequency of tone at  $V_+$ .

- b. Repeat Test 11a for rows 2,3 and 4, (m = 2,3,4).

- c. With  $V_1=1.0\ V$  set  $S_1$  to Terminal 5. (n = 1) and measure frequency of tone at V+.

- d. Repeat Test for columns 2,3, and 4. (n = 2,3,4).

- e. Set S1 to Terminal 4 and V1 = 0.0 V. Measure row tone amplitude at V+ (VROW).

- f. Set  $S_1$  to Terminal 8 and  $V_1 = 1.0$  V. Measure column tone amplitude at  $V_+$ . ( $V_{COL}$ ).

- g. Using results of Tests 11e and 11f, calculate:

$$dB_{CR} = 20 \log_{10} \frac{v_{COL}}{v_{ROW}}$$

#### FIGURE 23 — TEST TWELVE

Measure V+ and V1 with a true rms voltmeter. Calculate:

Note: The notch filters must have 50 dB attenuation at their

respective center frequencies.

% DIS =

$$\frac{V_1(rms)}{V + (rms)} \times 100$$

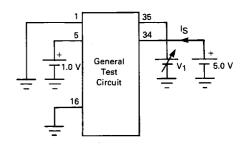

#### FIGURE 24 — TEST THIRTEEN

Measure Is at  $V_1 = 1.8 \text{ V}$  and  $V_1 = 2.8 \text{ V}$ .

Calculate:  $R_0 = 1.0 \text{ V} \div \left[ |S| \frac{-}{2.8 \text{ V}} |S| \frac{1.8 \text{ V}}{1.8 \text{ V}} \right]$

#### FIGURE 25 — TEST FOURTEEN

Set I = 1.0 mA and measure VTRI.

# FIGURE 26 - TEST FIFTEEN

- a. Measure ITRS with  $V_1 = 24 \text{ V}$ .

- b. Measure ITRS with  $V_1 = 30 \text{ V}$ .

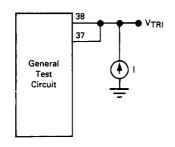

#### FIGURE 27 - TEST SIXTEEN

a. Increase V<sub>1</sub> from 21 V until V<sub>TRO</sub> switches on. Note that V<sub>TRO</sub> will be an 16 V<sub>pp</sub> square wave. Record this value of V<sub>1</sub>. Calculate:

$$V_{TRF} = V_1 - 20 V$$

Decrease V<sub>1</sub> from its setting in Test 16a until V<sub>TRO</sub> ceases switching. Record this value of V<sub>1</sub>. Calculate:

$$\Delta V_{TRF} = V_1 \begin{vmatrix} - & V_1 \\ Test \\ 16a & 16b \end{vmatrix}$$

#### FIGURE 28 — TEST SEVENTEEN

Measure ITRF. Calculate:  $RTRF = 1.0 \div ITRF$ .

#### FIGURE 29 — TEST EIGHTEEN

#### FIGURE 30 - TEST NINETEEN

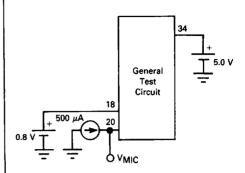

FIGURE 31 — TEST TWENTY

Measure V<sub>MIC</sub>

Measure V<sub>TRO</sub> peak-to-peak voltage swing. Using V<sub>TRI</sub> from Test 14 Calculate:

$V_{O(p-p)} = V_{TRI} - 20 V + V_{TRO}$

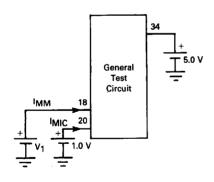

#### FIGURE 32 — TEST TWENTY-ONE

- a. Set V<sub>1</sub> = 2.0 V and measure IMIC.

- b. Set  $V_1 = 5.0 \text{ V}$  and measure I<sub>MM</sub>. Calculate:  $R_{MM} = 5.0 \text{ V} \div I_{MM}$

#### FIGURE 33 - TEST TWENTY-TWO

- a. With S1 open, measure VTXO. Using VR obtained in Test 1 Calculate: BTXO = VTXO  $\div$  VR

- b. With S1 open, measure  $V_{TXO}$  and  $V_{TXI}$ . Calculate:  $I_{TXI} = (V_{TXO} V_{TXI}) \div 200 \text{ k}\Omega$

- c. Close S<sub>1</sub> and set I =  $-10~\mu$ A. Measure V<sub>TXO</sub>. Calculate: V<sub>TXO</sub>(+) = V<sub>R</sub> V<sub>TXO</sub> where V<sub>R</sub> is obtained from Test 1.

- d. Close S<sub>1</sub> and set I =  $+10~\mu$ A. Measure V<sub>TXO</sub>. V<sub>TXO</sub>(-) = V<sub>TXO</sub>.

#### FIGURE 34 - TEST TWENTY-THREE

a. Set the generator for  $v_i=3.0~\text{mV}_{rms}.$  Measure ac voltage  $V_{TXO}.$  Calculate:

$$G_{TX} = \frac{V_{TXO}}{v_i}$$

b. Measure ac voltage V<sub>STA</sub>. Using V<sub>TXO</sub> from Test 23a calculate:

$$G_{STA} = \frac{V_{STA}}{V_{TXO}}$$

## FIGURE 35 — TEST TWENTY-FOUR

Measure ISTA.

## FIGURE 36 — TEST TWENTY-FIVE

- a. With S1 open, measure VRXO. Using VR obtained in Test 1, calculate: BRXO = VRXO  $\div$  VR.

- b. With S1 open, measure VRXO and VRXI. Calculate: IRXI = (VRXO VRX1)  $\div$  100  $k\Omega$

- c. Close S  $_1$  and set I =  $-10~\mu A$ . Measure VRXO. Using VR obtained in Test 1, calculate: VRXO (+) = VR VRXO.

- d. Close S<sub>1</sub> and set I =  $+10~\mu$ A and measure V<sub>RXO</sub>. V<sub>RXO</sub>(-) = V<sub>RXO</sub>.

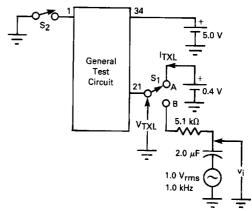

## FIGURE 37 — TEST TWENTY-SIX

- a. Set S<sub>1</sub> to position A with S<sub>2</sub> open. Measure  $I_{TXL}$ . Calculate:  $R_{TXL}$  (OFF) = 0.4 V  $\div$   $I_{TXL}$ .

- b. Set  $S_1$  to position B and close  $S_2.$  Measure ac voltages  $v_i$  and  $V_{TXL}.$  Calculate:

$$R_{TXL}$$

(ON) =  $\frac{V_{TXL}}{v_i - V_{TXL}} \times 5.1 \text{ k}\Omega$

#### FIGURE 38 - TEST TWENTY-SEVEN

A measure IRM.

Calculate: RRM(OFF) = 0.4 V ÷ IRM

b. Close S2 and switch S1 to position B. Measure ac voltages vi and VRM.

Calculate:

Calculate:  $R_{RM}(ON) = \frac{V_{RM}}{v_i - V_{RM}} \times 10 \text{ k}\Omega$

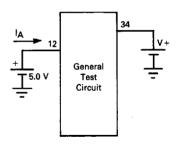

#### FIGURE 39 — TEST TWENTY-EIGHT

a. Set V + = 1.4 V. Measure  $I_{\Delta}(OFF)$

b. Set V + = 0.6 V. Measure  $I_{\Delta}(ON)$

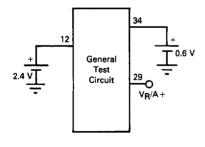

#### FIGURE 40 - TEST TWENTY-NINE

Measure VR/A+

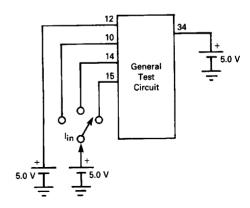

#### FIGURE 41 — TEST THIRTY

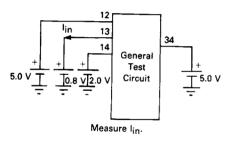

Measure  ${\rm I}_{in}$  at each of three inputs. For each, calculate:  ${\rm R}_{in} = 5.0 \; {\rm V/I}_{in}$

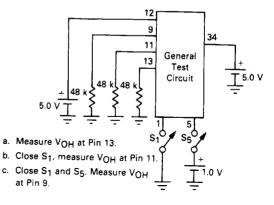

#### FIGURE 42 — TEST THIRTY-ONE

FIGURE 43 — TEST THIRTY-TWO

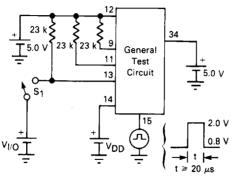

#### FIGURE 44 -- TEST THIRTY-THREE

- a. Set VDD to 0.8 V Measure VOL voltages at Pins 9 and 11.

- b. Close S<sub>1</sub>. Force V<sub>I/O</sub> to 0.8 V and V<sub>DD</sub> to 2.0 V. Apply 4 clock pulses to Pin 15. Open S<sub>1</sub> and decrease V<sub>DD</sub> to 0.8 V. Measure V<sub>OL</sub> at Pin 13.

#### APPLICATIONS INFORMATION

Figure 45 specifies a typical application circuit for the MC34010. Complete listings of external components are provided at the end of this section along with nominal component values.

The hook switch and polarity guard bridge configuration in Figure 45 is one of several options. If two bridges are used, one for the tone ringer and the other for speech and dialer circuits, then the hook switch can be simplified. Component values should be varied to optimize telephone performance parameters for each

application. The relationships between the application circuit components and certain telephone parameters are briefly described in the following:

#### On-Hook Input Impedance

R1, C17, and Z3 are the significant components for on-hook impedance. C17 dominates at low frequencies, R1 at high frequencies and Z3 provides the non-linearity required for 2.5 V and 10 V impedance signature tests. C17 must generally be  $\leq$  1.0  $\mu\text{F}$  to satisfy 5.0 Hz impedance specifications.

#### **Tone Ringer Output Frequencies**

R3 and C13 control the frequency ( $f_0$ ) of a relaxation oscillator. Typically  $f_0 = (R3C13 + 8.0 \ \mu s)^{-1}$ . The output tone frequencies are  $f_0/10$  and  $f_0/8$ . The warble rate is  $f_0/640$ . The tone ringer will operate with  $f_0$  from 1.0 kHz. R3 should be limited to values between 150 k and 300 k.

#### **Tone Ringer Input Threshold**

After R1, C17, and Z3 are chosen to satisfy on-hook impedance specifications, R2 is chosen for the desired ring start threshold. Increasing R2 reduces the ac input voltage required to activate the tone ringer output. R2 should be limited to values between 0.8 k and 2.0 k $\Omega$ .

#### Off-Hook DC Resistance

R4 conducts the dc line current in excess of the speech and dialer bias current. Increasing R4 increases the input resistance of the telephone for line currents above 10 mA. R4 should be selected between 30  $\Omega$  and 120  $\Omega$ .

#### Off-Hook AC Impedance

The ac input impedance is equal to the receive amplifier load impedance (at RXO) divided by the receive amplifier gain (voltage gain from V + to RXO). Increasing the impedance of the receiver increases the impedance of the telephone. Increasing the gain of the receiver amplifier decreases the impedance of the telephone.

#### **DTMF Output Amplitude**

R14 controls the amplitude of the row and column DTMF tones. Decreasing R14 increases the level of tones generated at V  $\pm$  . The ratio of the row and column tone amplitudes is internally fixed. R14 should be greater than 20  $\Omega$  to avoid excessive current in the DTMF output amplifier.

#### **Transmit Output Level**

R10 controls the maximum signal amplitude produced at V+ by the transmit amplifier. Decreasing R10 increases the transmit output signal at V+. R10 should be greater than 220  $\Omega$  to limit current in the transmit amplifier output.

#### **Transmit Gain**

The gain from the microphone to the telephone line varies directly with R11. Increasing R11 increases the signal applied to R10 and the ac current driven through R10 to the telephone line. The closed loop-gain from the microphone to the TXO terminal should be greater than 10 to prevent transmit amplifier oscillations.

Note: Adjustments to transmit level and gain are complicated by the addition of receiver sidetone current to the transmit amplifier output current at V+. Normally the sidetone current from the receiver will increase the transmit signal (if the current in the receiver is in phase with that in R10). Thus the transmit gain and sidetone levels cannot be adjusted independently.

#### Receiver Gain

Feedback resistor R6 adjusts the gain at the receiver amplifier, Increasing R6 increases the receiver amplifier gain.

#### Sidetone Level

Sidetone reduction is achieved by the cancellation of receiver amplifier input signals from R9 and R5. R8, R15, and C6 determine the phase of the sidetone balance signal in R9. The ac voltage at the junction of R8 and R9 should be 180° out of phase with the voltage at V+. R9 is selected such that the signal current in R9 is slightly greater than that in R5. This insures that the sidetone current in the receiver adds to the transmit amplifier output current.

#### Hook-Switch Click Suppression

When the telephone is switched to the off-hook condition C3 charges from 0 volts to a 300 mV bias voltage. During this time interval, receiver clicks are suppressed by a low impedance at the RM terminal. If this click suppression mechanism is desired during a rapid succession of hook switch transitions, then C3 must be quickly discharged when the telephone is on-hook, R16 and S3 provide a rapid discharge path for C3 to reset the click suppression timer. R16 is selected to limit the discharge current in S3 to prevent damage to switch contacts.

#### Microprocessor Interface

The six microprocessor interface lines (DP, TO, MS, DD, I/O, and CL) can be connected directly to a port, as shown in Figure 47. The DP line (Depressed Pushbutton) is also connected to an interrupt line to signal the microprocessor to begin a read data sequence when storing a number into memory. The MC34010A clock speed requirement is slow enough (typically 20 kHz) so that it is not necessary to divide down the processor's system clock, but rather a port output can be toggled. This facilitates synchronizing the clock and data transfer, eliminating the need for hardware to generate the clock.

The DD pin must be maintained at a Logic "0" when the microprocessor section is not in use, so as to permit normal operation of the keypad.

When the microprocessor interface section is not in use, the supply voltage at Pin 12 (A+) may be disconnected to conserve power. Normally the speech circuitry is powered by the voltage supplied at the V+ terminal (Pin 34) from the telephone lines. During this time, A+ powers only the active pullups on the three microprocessor outputs (DP, MS, and I/O). When the telephone is "on-hook," and V+ falls below 0.6 volts, power is then supplied to the telephone speech and dialer circuitry from A+. Powering the circuit from the A+ pin permits communication with a microprocessor, and/or use of the transmit and receiver amplifiers, while the telephone is "on-hook."

# **EXTERNAL COMPONENTS**

(Component Labels Referenced to Figure 45)

| Capacitors        | Nominal<br>Value                 | Description                                                                                                                                    |  |

|-------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C1, C2 100 pF Cer |                                  | Ceramic Resonator oscillator capacitors.                                                                                                       |  |

| СЗ                | 1.0 μF, 3.0 V                    | Transmit limiter low-pass filter capacitor: controls attack and decay time of transmit peak limiter.                                           |  |

| C4, C5            | 0.1 μF                           | Transmit amplifier input capacitors: prevent dc current flow into TXL pin and attenuate low-frequency noise on microphone lead.                |  |

| C6                | 0.05 μF                          | Sidetone network capacitor: provides phase-shift in sidetone path to match that caused by telephone line reactance.                            |  |

| C7, C8            | 0.05 μF                          | Receiver amplifier input capacitors: prevent dc current flow into RM terminal and attenuates low frequency noise on the telephone line.        |  |

| C9                | 2.2 μF, 3.0 V                    | VR regulator capacitor: frequency compensates the VR regulator to prevent oscillation.                                                         |  |

| C10               | 0.01 μF                          | Receiver amplifier output capacitor: frequency compensates the receiver amplifier to prevent oscillation.                                      |  |

| C11               | 0.1 μF                           | DC load filter capacitor: prevents the dc load circuit from attenuating ac signals on V+.                                                      |  |

| C12               | 0.01 μF                          | Telephone line bypass capacitor: terminates telephone line for high frequency signals and prevents oscillation in the VR regulator.            |  |

| C13               | 620 pF                           | Tone ringer oscillator capacitor: determines clock frequency for tone and warble frequency synthesizers.                                       |  |

| C14               | 0.1 μF                           | DTMF output feedback capacitor: ac couples feedback around the DTMF output amplifier which reduce output impedance.                            |  |

| C15               | 4.7 μF, 25 V                     | Tone ringer input capacitor: filters the rectified tone ringer input signal to smooth the supply potential for oscillator and output buffer.   |  |

| C16               | 1.0 μF, 10 V                     | Tone ringer filter capacitor: integrates the voltage from current sense resistor R2 at the input of the threshold detector.                    |  |

| C17               | 1.0 μF, 250 Vac<br>Non-polarized | Tone ringer line capacitor: ac couples the tone ringer to the telephone line; partially controls the on-<br>hook input impedance of telephone. |  |

| Resistors | Nominal<br>Value | Description                                                                                                                                                                           |  |

|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R1        | 6.8 k            | Tone ringer input resistor: limits current into the tone ringer from transients on the telephone line partially controls the on-hook impedance of the telephone.                      |  |

| R2        | 1.8 k            | Tone ringer current sense resistor: produces a voltage at the input of the threshold detector in proportion to the tone ringer input current.                                         |  |

| R3        | 200 k            | Tone ringer oscillator resistor: determines the clock frequency for tone and warble frequency synthesizers.                                                                           |  |

| R4        | 82, 1.0 W        | DC load resistor: conducts all dc line current in excess of the current required for speech or dialing circuits; controls the off-hook dc resistance of the telephone.                |  |

| R5, R7    | 150 k, 56 k      | Receiver amplifier input resistors: couple ac input signals from the telephone line to the receiver amplifier; signal in R5 subtracts from that in R9 to reduce sidetone in receiver. |  |

| R6        | 200 k            | Receiver amplifier feedback resistor: controls the gain of the receiver amplifier.                                                                                                    |  |

| R8, R9    | 1.5 k, 30 k      | Sidetone network resistors: drive receiver amplifier input with the inverted output signal from the transmitter; phase of signal in A9 should be opposite that in R5.                 |  |

| R10       | 270              | Transmit amplifier load resistor: converts output voltage of transmit amplifier into a current that drives the telephone line; controls the maximum transmit level.                   |  |

| R11       | 200 k            | Transmit amplifier feedback resistor: controls the gain of the transmit amplifier.                                                                                                    |  |

| R12, R13  | 4.7 k, 4.7 k     | Transmit amplifier input resistors: couple signal from microphone to transmit amplifier; control the dynamic range of the transmit peak limiter.                                      |  |

| R14       | 36               | DTMF calibration resistor: controls the output amplitude of the DTMF dialer.                                                                                                          |  |

| R15       | 2.0 k            | Sidetone network resistor (optional): reduces phase shift in sidetone network at high frequencies.                                                                                    |  |

| R16       | 100              | Hook switch click suppression current limit resistor (optional): limits current when S3 discharges C3 after switching to the on-hook condition.                                       |  |

| RX        | 3.0 k            | Microphone bias resistor: sources current from VR to power a 2-terminal electret microphone; R <sub>X</sub> is not used with 3-terminal microphones.                                  |  |

# **EXTERNAL COMPONENTS** (continued)

| Semiconductors                                                                                                                                                                                                                                                                | Electret Mic                                                                                                                         | Receiver                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| B1 = MDA101A, or equivalent,<br>or 4-1N4005<br>T1 = 2N4126 or equivalent<br>Z1 = 18 V, 1.5 W, 1N5931A<br>Z2 = 30 V, 1.5 W, 1N5936A<br>Z3 = 4.7 V, 1/2 W, 1N750<br>XR — muRata Erie CSB 500 kHz<br>Resonator, or equivalent<br>Piezo — PBL 5030BC Toko Buzzer<br>or equivalent | Terminal, Primo EM-95 (Use R <sub>X</sub> )     or equivalent     Terminal, Primo 07A181P (Remove R <sub>X</sub> )     or equivalent | Primo Model DH-34 (300 Ω) or equivalen |

Motorola Inc. does not endorse or warrant the suppliers referenced.