TOSHIBA TD7626F/FN

**TENTATIVE**

TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TD7626F, TD7626FN

# 2.7GHz FREQUENCY SYNTHESIZER FOR SATELLITE TV

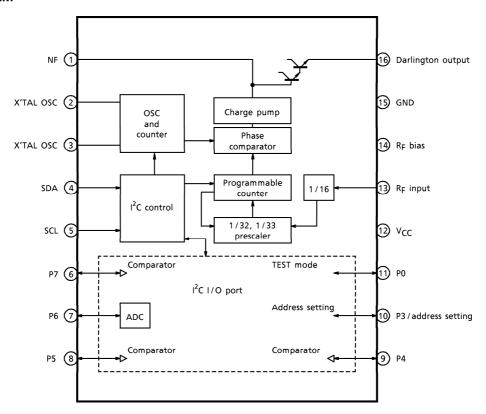

TD7626F and TD7626FN are single-chip frequency synthesizer ICs that can be combined with a  $\mu$ CPU to configure an advanced-function frequency synthesizer system.

TD7626FN comes in a more compact package, pitch

## **FEATURES**

High input sensitivity

$f_{in} = 0.5 \sim 2.7 \text{GHz} : -15 \text{dBmW } (50\Omega) \text{ (Min.)}$

- Built-in 1/16 prescaler

- Built-in 5-level AD converter

- Built-in simple comparators x 3

- Simple control bus (I<sup>2</sup>C bus)

- Four-address selectable by address selector

- Frequency divider ratio settings: 1/512, 1/1024

- Built-in power-on reset circuit

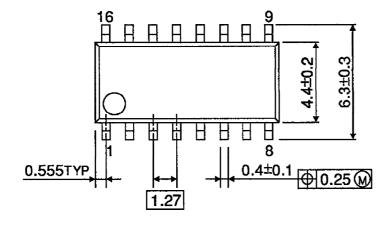

Small flat package version: TD7626F : SOP16 (1.27mm pitch)

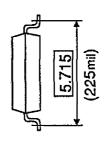

TD7626FN: SSOP16 (0.65mm pitch)

(Note) These devices are easy to be damaged by high static voltage or electric fields. In regards to this, please handle with care.

Status after power-on reset

Band drive P7~P0 : OFF Tuning amp : ON : **50**μ**A** Charge pump output current Reference frequency divider ratio: 1/512 Counter data : All [0]

TD7626F SOP16-P-225-1.27 TD7626FN SSOP16-P-225-0.65B

Weight

SOP16-P-225-1.27 SSOP16-P-225-0.65B : 0.07g (Typ.)

: 0.16g (Typ.)

■ TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

The information contained herein is subject to change without notice.

# **BLOCK DIAGRAM**

# **TERMINAL FUNCTIONS**

| PIN No. | PIN NAME                 | FUNCTION                                                                                                                                                                | INTERFACE CIRCUIT                                 |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1       | NF                       | Compares the phase of the input R <sub>F</sub> signal against the frequency data and feeds back its difference output from the current                                  | 1 3 100Ω<br>1 50Ω                                 |

| 16      | Charge pump<br>output    | pump.                                                                                                                                                                   | os-sw os-sw                                       |

| 2       | X'tal OSC <sub>in</sub>  | Crystal oscillator pins to generate the reference signal for the phase comparator.                                                                                      | 2                                                 |

| 3       | X'tal OSC <sub>out</sub> | Consist of the inverter amp.                                                                                                                                            | 3 20Ω 9.9kΩ 100Ω                                  |

| 4       | SDA                      | Normally used as input/output pins for the I <sup>2</sup> C bus serial data. In TEST mode, used as the input pin for the signal to be compared by the phase comparator. | 4 20Ω 1kΩ Cy 1 Cy 3 |

| 5       | SCL                      | Normally used as the I <sup>2</sup> C bus serial clock input. In TEST mode, used to input the reference signal of the phase comparator.                                 | S 1kΩ (V)     |

| 6       | P7                       | Output can be controlled by setting the band switch data.  The circuit configuration is open collector                                                                  | 6<br>8 3kΩ COMP                                   |

| 8       | P5                       | output. Each pin has a built-in comparator. The status of the comparator can be checked in READ mode.                                                                   | 9 70κΩ                                            |

| 9       | P4                       | In TEST mode, P7 is a counter output which allows counter operation to be checked.                                                                                      |                                                   |

| PIN No.  | PIN NAME                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                      | INTERFACE CIRCUIT                                          |

|----------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 7        | P6                                          | Output can be controlled by setting the band switch data.  The circuit configuration is open collector output.  An A/D converter is built in. In READ mode, five levels of applied voltage can be read.  In TEST mode, outputs the reference signal derived by dividing the crystal OSC signal by the set divider ratio. This allows operation to be checked. | $3k\Omega$ ADC $70k\Omega$                                 |

| 10       | P3                                          | Basically used as the address setting pin. The sub-address can be changed by applied voltage. Can be used as a band switch as well, but incorporates resistance (12k $\Omega$ ) for limiting current.                                                                                                                                                         | $\frac{3k\Omega}{10}$ Address $\frac{70k\Omega}{10}$       |

| 11       | P0                                          | Output can be controlled by setting the band switch data. Incorporates resistance ( $12k\Omega$ ) for limiting current. (Can also be used for setting the prescaler in TEST mode.) (Open collector output)                                                                                                                                                    | $\frac{3k\Omega}{12k\Omega}$ TEST $70k\Omega$              |

| 12       | V <sub>C</sub> C                            | Power supply pin                                                                                                                                                                                                                                                                                                                                              | _                                                          |

| 13<br>14 | R <sub>F</sub> input<br>R <sub>F</sub> bias | Prescaler input pins. The circuit configuration is differential input. Differential reference bias pin 14 has a built-in 15pF capacitor.                                                                                                                                                                                                                      | 13 500Ω 500Ω<br>14 2 b c c c c c c c c c c c c c c c c c c |

| 15       | GND                                         | Ground pin                                                                                                                                                                                                                                                                                                                                                    |                                                            |

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTICS       | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Supply Voltage 1      | V <sub>CC1</sub> | 6.0             | V    |

| Power Dissipation     | PD               | (Note 1)        | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 20∼8</b> 5 | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼150 | °C   |

- (Note 1) F-type: 540mW, FN-type: 560mW

- (Note 2) When using the device at temperatures higher than 25°C, maximum power dissipation decreases for every 1°C as follows: 4.3mW with F-type: 4.5mW with FN-type.

- (Note 3) Do not set the port pins (Pins 6, 7, 8, 9, 10, and 11) at or lower than the level of the GND pin.

- (Note 4) These devices are easy to be damaged by high static voltage or electric fields. In regards to this, please handle with care.

# RECOMMENDED SUPPLY VOLTAGE

| PIN<br>No. | PIN NAME        | MIN. | TYP. | MAX. | UNIT |

|------------|-----------------|------|------|------|------|

| 12         | V <sub>CC</sub> | 4.5  | 5.0  | 5.5  | V    |

**TOSHIBA**

**ELECTRICAL CHARACTERISTICS** (Unless otherwise stated,  $V_{CC}$  = 5V, Ta = 25°C) AC CHARACTERISTICS

| CHARACTERISTIC                     | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                 | MIN. | TYP.      | MAX. | UNIT              |

|------------------------------------|--------------------|----------------------|----------------------------------------------------------------|------|-----------|------|-------------------|

| Supply Current                     | l <sub>CC1</sub>   | 1                    | Band switch: OFF OS: [1]                                       | 20   | 35        | 52   | mA                |

| Prescaler Input<br>Sensitivity     | V <sub>in</sub>    | 2                    | f = 500~2700MHz                                                | - 15 | _         | +3   | dBmW              |

| Logic Input High<br>Voltage        | VIH                |                      | Logic pins (SDA, SCL) In the test circuit, transfer P5         | 3.0  | _         | _    |                   |

| Logic Input Low<br>Voltage         | VIL                | 3                    | data and determine reception<br>from the lighting of the LED   | _    | _         | 0.8  | V                 |

| Logic Output High<br>Voltage       | Voн                |                      | lamp.  Measure the output using a                              | 3.8  | _         | _    |                   |

| Logic Output Low<br>Voltage        | V <sub>OL</sub>    |                      | logic analyzer.                                                | _    | _         | 0.5  |                   |

| Logic Input High<br>Current        | ЧН                 | 3                    | Apply 5V to input pin.                                         | _    | _         | 10   |                   |

| Logic Input Low<br>Current         | lOL                | ]                    | Apply 0V to input pin.                                         | _    | _         | - 20 | μΑ                |

| External OSC Input<br>Amplitude    | osc <sub>in</sub>  | 3                    | OSC <sub>in</sub> (Pin 2)                                      | 350  | _         | 1000 | mV <sub>p-p</sub> |

| OSC Operating<br>Frequency         | OSC <sub>fin</sub> | 3                    | Pins 2, 3                                                      | 3.0  | 4.0       | 4.5  | MHz               |

| Crystal Negative<br>Resistance     | X <sub>tR</sub>    | 3                    | TEST mode, frequency divided crystal signal output, P6 monitor | _    | 1.5       | _    | kΩ                |

| Output Port Flow<br>Current        | IPin               | 3                    | P4, P5, P6, P7                                                 | 5    | _         | _    | mA                |

| Output Port Leakage<br>Current     | <sup>IP</sup> Ik   | 3                    | Apply 12V as pull-up voltage.                                  | _    | _         | 10   | μΑ                |

| Output Port Built-In<br>Resistance | R <sub>port</sub>  | _                    | P0 and P3                                                      | _    | 12        | _    | kΩ                |

| Output Port MAX<br>Voltage         | V <sub>port</sub>  | _                    | P0, P3, P4, P5, P6, P7                                         | _    | _         | 13.2 | V                 |

| A/D Converter Input<br>Voltage     | V <sub>ADC</sub>   | _                    | P6                                                             | 0.0  | _         | 13.2 | ٧                 |

| Comparator Pin Input<br>Voltage    | VCMP               | 3                    | P4, P5, and P7                                                 | 0.0  | _         | 13.2 | V                 |

| Comparator High<br>Voltage         | V <sub>HCMP</sub>  | 3                    | P4, P5, and P7                                                 | 2.0  | _         | 13.2 | V                 |

| Comparator Low<br>Voltage          | V <sub>LCMP</sub>  | 3                    | P4, P5, and P7                                                 | 0.0  | _         | 0.8  | V                 |

| Charge Pump Output<br>Current      | I <sub>chg0</sub>  | _                    | CP: [0]<br>CP: [1]                                             | _    | 50<br>170 | _    | μΑ                |

TOSHIBA TD7626F/FN

# **DATA FORMAT**

a) WRITE mode

|   | BYTE          | MSB                   |                        |                        |                        |                       |                        |                       | LSB   |                  |

|---|---------------|-----------------------|------------------------|------------------------|------------------------|-----------------------|------------------------|-----------------------|-------|------------------|

| 1 | ADDRESS Byte  | 1                     | 1                      | 0                      | 0                      | 0                     | MA1                    | MA0                   | R/W=0 | ACK              |

| 2 | DIVIDER Byte① | 0                     | <b>2</b> <sup>14</sup> | <b>2</b> <sup>13</sup> | <b>2</b> <sup>12</sup> | 2 <sup>11</sup>       | <b>2</b> <sup>10</sup> | <b>2</b> 9            | 28    | ACK              |

| 3 | DIVIDER Byte2 | <b>2</b> <sup>7</sup> | <b>2</b> <sup>6</sup>  | <b>2</b> <sup>5</sup>  | 24                     | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup>  | <b>2</b> <sup>1</sup> | 20    | $ACK \mathbb{D}$ |

| 4 | CONTROL Byte  | 1                     | СР                     | T <sub>1</sub>         | Т0                     | TS2                   | TS1                    | TS0                   | OS    | ACK              |

| 5 | BAND SW Byte  | P7                    | P6                     | P5                     | P4                     | P3                    | Х                      | Х                     | P0    | ACK(L)           |

DATA LATCHDON'T CareACK : Acknowledgment

# b) READ mode

|   | BYTE         | MSB |    |     |     |     |                |     | LSB            |     |

|---|--------------|-----|----|-----|-----|-----|----------------|-----|----------------|-----|

| 1 | ADDRESS Byte | 1   | 1  | 0   | 0   | 0   | MA1            | MA0 | R/W=1          | ACK |

| 2 | STATUS Byte  | 0   | FL | IP7 | IP5 | IP4 | A <sub>2</sub> | Α1  | A <sub>0</sub> | ACK |

ACK: Acknowledgment

# **DATA DETAILS**

MA1, MA0: Programmable address bits

(Indicate applied voltage of pin 10 and corresponding address setting.)

| ADDRESS PIN APPLIED VOLTAGE                | MA1 | MA0 |

|--------------------------------------------|-----|-----|

| 0~0.2×V <sub>CC</sub>                      | 0   | 0   |

| $0.3 \times V_{CC} \sim 0.7 \times V_{CC}$ | 1   | 0   |

| 0~V <sub>CC</sub>                          | 0   | 1   |

| $0.8 \times V_{CC} \sim V_{CC}$            | 1   | 1   |

• CP : Charge pump current setting

$\llbracket \ 0 \ \rrbracket \ : \ 50 \mu A \ (Typ.)$   $\llbracket \ 1 \ \rrbracket \ : \ 170 \mu A \ (Typ.)$

• T<sub>1</sub> : Test mode switching

「0]: NORMAL mode

[1]: TEST mode

• T<sub>0</sub> : Charge pump control setting

0 : Charge pump ON1 : Charge pump OFF

TOSHIBA TD7626F/FN

# • TS2, TS1, TS0 : TEST mode settings

| CHARACTERISTIC        | Т1 | TS2 | TS1 | TS0 | FREQUENCY<br>DIVIDER<br>RATIO | REMARKS                                                                 |

|-----------------------|----|-----|-----|-----|-------------------------------|-------------------------------------------------------------------------|

| Normal State          | 0  | Х   | Χ   | 0   | 1 / 1024                      | _                                                                       |

| Normal State          | 0  | Х   | Х   | 1   | 1/512                         | _                                                                       |

| Charge Burns Sink     | 1  | 1   | 0   | 0   | 1 / 1024                      | FL = 0 : Charge pump output sink side only on                           |

| Charge Pump<br>Source | 1  | 1   | 0   | 1   | 1/512                         | FL = 1 : Charge pump output source side only on                         |

| Output Port OFF       | 1  | 1   | 1   | 0   | 1 / 1024                      | P7~P4 = OFF                                                             |

| Phase Comparator      | 1  | 1   | 1   | 1   | 1/512                         | SDA : Input of signal to be compared                                    |

| Test                  | ı  | '   | J   | '   | 1/312                         | SCL : Reference signal input                                            |

| Crystal Divider       | 1  | 0   | X   | 0   | 1 / 1024                      | P6 : Crystal divider output<br>P7 : Counter output (1/16×32×count data) |

| Counter Output        | 1  | 0   | Х   | 1   | 1/512                         | P0: Prescaler settings…『0』: ON 『1』: OFF P7~P4 = OFF                     |

# X: DON'T Care

• OS : Tuning amp control settings

[ 0 ] : Tuning on (Normal state)

¶ 1

☐ : Tuning off (Fixes charge pump output at 0.0~0.2V)

• FL : Lock detect flag

[ 0 ] : Unlocked

[ 1 ] : Locked

• IP7, IP5, IP4 : Comparator output (P7, P5, P4)

$\llbracket \ 0 \ \rrbracket \ : \ Applied \ voltage \ \dots \ 0.0 \sim 0.8 V$   $\llbracket \ 1 \ \rrbracket \ : \ Applied \ voltage \ \dots \ 2.0 \sim 13.2 V$

• A2, A1, A0 : 5-level A/D converter (P6)

| ADC PIN APPLIED VOLTAGE                      | A <sub>2</sub> | Α1 | A <sub>0</sub> |

|----------------------------------------------|----------------|----|----------------|

| 0.60×V <sub>CC</sub> ~13.2V                  | 1              | 0  | 0              |

| 0.45×V <sub>CC</sub> ~0.60×V <sub>CC</sub>   | 0              | 1  | 1              |

| $0.30 \times V_{CC} \sim 0.45 \times V_{CC}$ | 0              | 1  | 0              |

| $0.15 \times V_{CC} \sim 0.30 \times V_{CC}$ | 0              | 0  | 1              |

| 0~0.15×V <sub>CC</sub>                       | 0              | 0  | 0              |

## I<sup>2</sup>C BUS CONTROLLED FORMAT SUMMARY

Bus controlled format of TD7626F, TD7626FN are based on I<sup>2</sup>C Bus Control format of Philips.

# Data transfer format S | Slave address | 0 | A | Data | A | P | MSB | 7bit | MSB | 8bit | 8bi

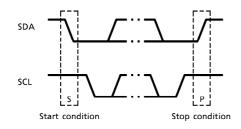

S : Start conditions P : Stop conditions A : Acknowledge

# (1) Start condition and stop condition

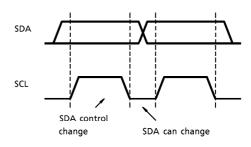

# (2) Bit transfer

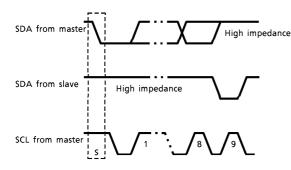

# (3) Acknowledgement

# (4) Slave addresses

| A <sub>6</sub> | A <sub>5</sub> | Α4 | Α3 | A <sub>2</sub> | Α <sub>1</sub> | Α <sub>0</sub> | R/W |

|----------------|----------------|----|----|----------------|----------------|----------------|-----|

| 1              | 1              | 0  | 0  | 0              | Х              | Х              | 0   |

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

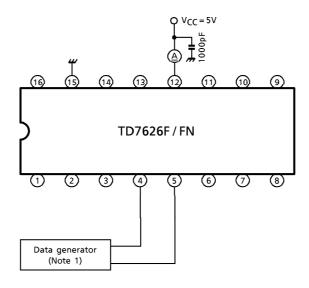

# **TEST CIRCUIT 1**

(Note 1) Band switch···OFF, tuning amp···OFF

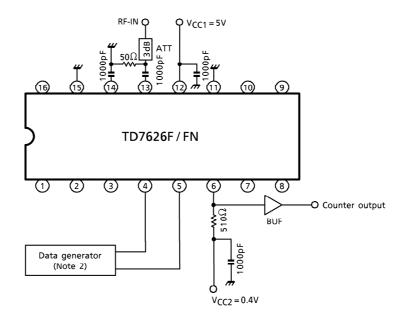

# **TEST CIRCUIT 2**

(Note 2) See TEST mode settings (Counter output)

TOSHIBA TD7626F/FN

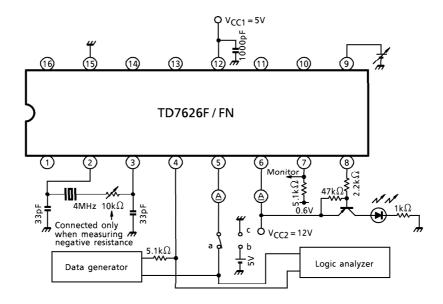

# **TEST CIRCUIT 3**

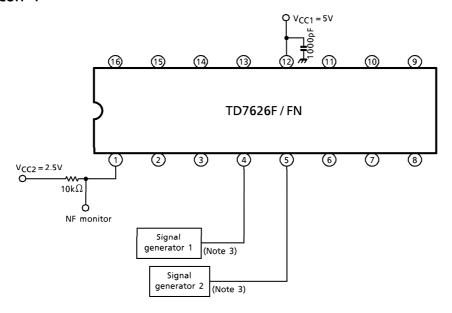

# **TEST CIRCUIT 4**

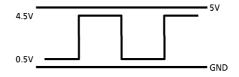

(Note 3) Phase comparator input level

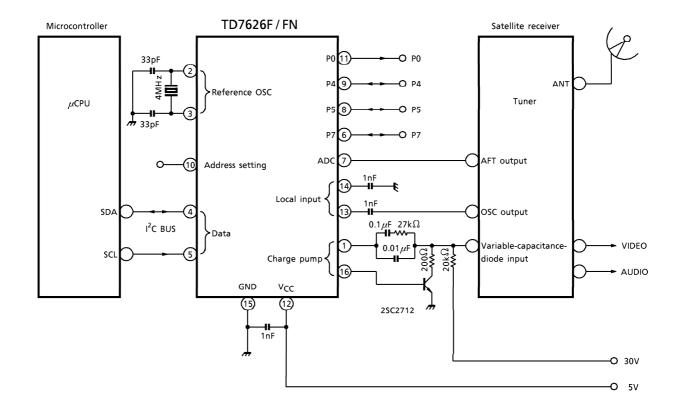

# **EXAMPLE OF FREQUENCY SYNTHESIZER APPLICATION CIRCUIT**

**TOSHIBA**

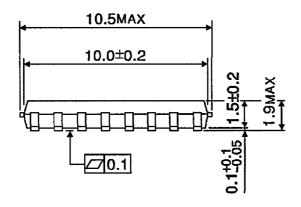

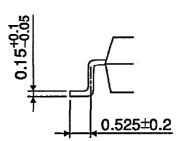

# **OUTLINE DRAWING**

SOP16-P-225-1.27

Weight: 0.16g (Typ.)

Weight: 0.07g (Typ.)

# OUTLINE DRAWING SSOP16-P-225-0.65B Unit:mm 0.23TYP 0.65 5.5MAX 5.0±0.2 0.45±0.2