### **Features**

- Supply Voltage 4.5 V to 5.5 V

- Operating Temperature Range -40°C to +85°C

- Minimal External Circuitry Requirements, No RF Components on the PC Board Except Matching to the Receiver Antenna

- . High Sensitivity, Especially at Low Data Rates

- Sensitivity Reduction Possible Even While Receiving

- Fully Integrated VCO

- Low Power Consumption Due to Configurable Self Polling with a Programmable Time Frame Check

- Single-ended RF Input for Easy Matching to  $\lambda/4$  Antenna or Printed Antenna on PCB

- Low-cost Solution Due to High Integration Level

- ESD Protection According to MIL-STD 883 (4 KV HBM) Except Pin POUT (2 KV HBM)

- High Image Frequency Suppression Due to 1 MHz IF in Conjunction with a SAW Frontend Filter. Up to 40 dB is Thereby Achievable with Newer SAWs

- Programmable Output Port for Sensitivity Selection or for Controlling External Periphery

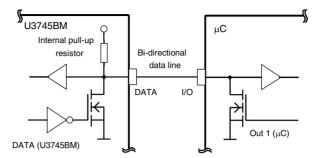

- · Communication to the Microcontroller Possible via a Single, Bi-directional Data Line

- Power Management (Polling) is also Possible by Means of a Separate Pin via the Microcontroller

## **Description**

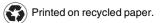

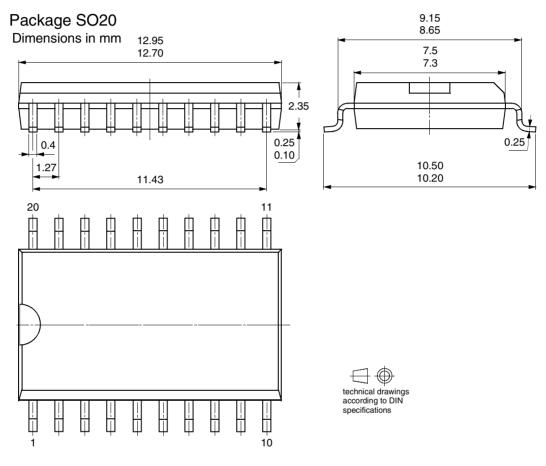

The U3745BM is a multi-chip PLL receiver device supplied in an SO20 package. It has been specially developed for the demands of RF low-cost data transmission systems with low data rates from 1 kBaud to 10 kBaud in Manchester or Bi-phase code. The receiver is well suited to operate with Atmel's PLL RF transmitter U2745B. It can be used in the frequency receiving range of  $f_0 = 310 \text{ MHz}$  to 440 MHz for ASK data transmission. All the statements made below refer to 433.92-MHz and 315-MHz applications.

The main applications of the U3745BM are in the areas of outside temperature metering, socket control, garage door opener, consumption metering, light/fan or aircondition control, jalousies, wireless keyboard and various other consumer market applications.

# UHF ASK Receiver IC

**U3745BM**

# **System Block Diagram**

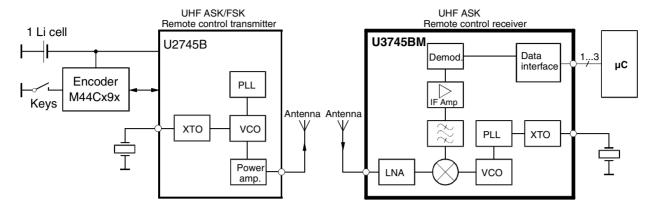

# **Pin Configuration**

Figure 1. Pinning SO20

# **Pin Description**

| Pin | Symbol | Function                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------|

| 1   | NC     | Not connected                                                                                     |

| 2   | ASK    | ASK high                                                                                          |

| 3   | CDEM   | Lower cut-off frequency data filter                                                               |

| 4   | AVCC   | Analog power supply                                                                               |

| 5   | AGND   | Analog ground                                                                                     |

| 6   | DGND   | Digital ground                                                                                    |

| 7   | MIXVCC | Power supply mixer                                                                                |

| 8   | LNAGND | High-frequency ground LNA and mixer                                                               |

| 9   | LNA_IN | RF input                                                                                          |

| 10  | NC     | Not connected                                                                                     |

| 11  | LFVCC  | Power supply VCO                                                                                  |

| 12  | LF     | Loop filter                                                                                       |

| 13  | LFGND  | Ground VCO                                                                                        |

| 14  | XTO    | Crystal oscillator                                                                                |

| 15  | DVCC   | Digital power supply                                                                              |

| 16  | MODE   | Selecting 433.92 MHz/315 MHz. Low: 4.90625 MHz (USA), High: 6.76438 (Europe)                      |

| 17  | POUT   | Programmable output port                                                                          |

| 18  | TEST   | Test pin, during operation at GND                                                                 |

| 19  | ENABLE | Enables the polling mode. Low: polling mode off (sleep mode). High: polling mode on (active mode) |

| 20  | DATA   | Data output/configuration input                                                                   |

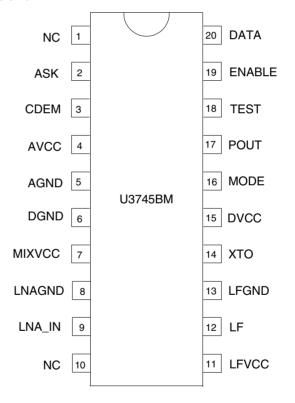

# **Block Diagram**

### **RF Front End**

The RF front end of the receiver is a heterodyne configuration that converts the input signal into a 1-MHz IF signal. According to the block diagram, the front end consists of an LNA (low noise amplifier), LO (local oscillator), a mixer and RF amplifier.

The LO generates the carrier frequency for the mixer via a PLL synthesizer. The XTO (crystal oscillator) generates the reference frequency  $f_{\rm XTO}$ . The VCO (voltage-controlled oscillator) generates the drive voltage frequency  $f_{\rm LO}$  for the mixer.  $f_{\rm LO}$  is dependent on the voltage at pin LF.  $f_{\rm LO}$  is divided by a factor of 64. The divided frequency is compared to  $f_{\rm XTO}$  by the phase frequency detector. The current output of the phase frequency detector is connected to a passive loop filter and thereby generates the control voltage  $V_{\rm LF}$  for the VCO. By means of that configuration,  $V_{\rm LF}$  is controlled in a way that  $f_{\rm LO}/64$  is equal to  $f_{\rm XTO}$ . If  $f_{\rm LO}$  is determined,  $f_{\rm XTO}$  can be calculated using the following formula:

$$f_{XTO} = \frac{f_{LO}}{64}$$

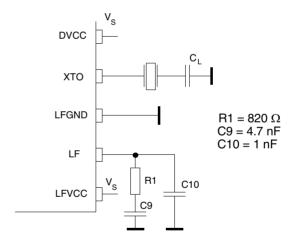

The XTO is a one-pin oscillator that operates at the series resonance of the quartz crystal. According to Figure 2, the crystal should be connected to GND via a capacitor CL. The value of that capacitor is recommended by the crystal supplier. The value of CL should be optimized for the individual board layout to achieve the exact value of  $f_{\rm XTO}$  and hereby of  $f_{\rm LO}$ . When designing the system in terms of receiving bandwidth, the accuracy of the crystal and XTO must be considered.

Figure 2. PLL Peripherals

The passive loop filter connected to Pin LF is designed for a loop bandwidth of BLoop = 100 kHz. This value for BLoop exhibits the best possible noise performance of the LO. Figure 2 shows the appropriate loop filter components to achieve the desired loop bandwidth. If the filter components are changed for any reason, please note that the maximum capacitive load at Pin LF is limited. If the capacitive load is exceeded, a bit check may no longer be possible since  $f_{LO}$  cannot settle in time before the bit check starts to evaluate the incoming data stream. Therefore, self polling also does not work in that case.

$f_{LO}$  is determined by the RF input frequency  $f_{RF}$  and the IF frequency  $f_{IF}$  using the following formula:

$$f_{IO} = f_{BF} - f_{IF}$$

To determine  $f_{LO}$ , the construction of the IF filter must be considered at this point. The nominal IF frequency is  $f_{IF} = 1$  MHz. To achieve a good accuracy of the filter's corner frequencies, the filter is tuned by the crystal frequency  $f_{XTO}$ . This means that there is a fixed relation between  $f_{IF}$  and  $f_{LO}$  that depends on the logic level at pin mode. This is described by the following formulas:

$$MODE = 0 (USA) f_{IF} = \frac{f_{LO}}{314}$$

$$MODE = 0 (Europe) f_{IF} = \frac{f_{LO}}{432.92}$$

The relation is designed to achieve the nominal IF frequency of  $f_{\rm IF}=1$  MHz for most applications. For applications where  $f_{\rm RF}=315$  MHz, the MODE must be set to '0'. In the case of  $f_{\rm RF}=433.92$  MHz, the MODE must be set to '1'. For other RF frequencies,  $f_{\rm IF}$  is not equal to 1 MHz.  $f_{\rm IF}$  is then dependent on the logical level at Pin MODE and on  $f_{\rm RF}$ . Table 1 summarizes the different conditions.

The RF input either from an antenna or from a generator must be transformed to the RF input pin LNA\_IN. The input impedance of that pin is provided in the electrical parameters. The parasitic board inductances and capacitances also influence the input matching. The RF receiver U3745BM exhibits its highest sensitivity at the best signal-tonoise ratio in the LNA. Hence, noise matching is the best choice for designing the transformation network.

A good practice when designing the network is to start with power matching. From that starting point, the values of the components can be varied to some extent to achieve the best sensitivity.

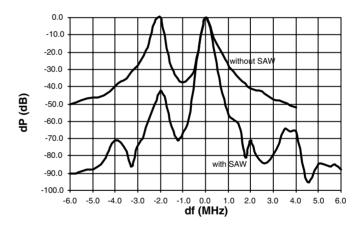

If a SAW is implemented into the input network, a mirror frequency suppression of  $\Delta P_{Ref}$  = 40 dB can be achieved. There are SAWs available that exhibit a notch at  $\Delta f$  = 2 MHz. These SAWs work best for an intermediate frequency of IF = 1 MHz. The selectivity of the receiver is also improved by using a SAW. In typical automotive applications, a SAW is used.

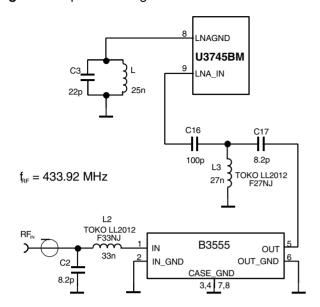

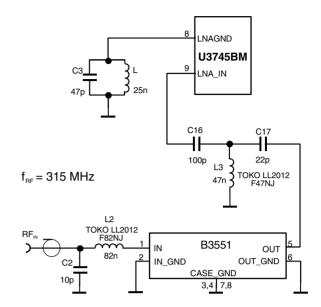

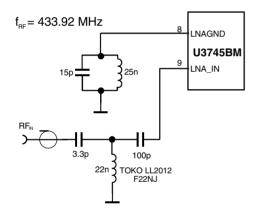

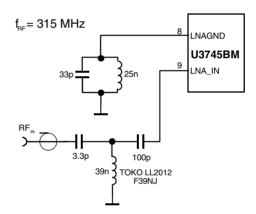

Figure 3 shows a typical input matching network for  $f_{RF} = 315$  MHz and  $f_{RF} = 433.92$  MHz using a SAW. Figure 4 illustrates an input matching to 50  $\Omega$  without a SAW. The input matching networks shown in Figure 4 are the reference networks for the parameters given in the section "Electrical Characteristics".

Table 1. Calculation of LO and IF Frequency

| Conditions                                    | Local Oscillator Frequency                     | Intermediate Frequency           |

|-----------------------------------------------|------------------------------------------------|----------------------------------|

| f <sub>RF</sub> = 315 MHz, MODE = 0           | f <sub>LO</sub> = 314 MHz                      | f <sub>IF</sub> = 1 MHz          |

| f <sub>RF</sub> = 433.92 MHz, MODE = 1        | f <sub>LO</sub> = 432.92 MHz                   | f <sub>IF</sub> = 1 MHz          |

| 300 MHz < f <sub>RF</sub> < 365 MHz, MODE = 0 | $f_{LO} = \frac{f_{RF}}{1 + \frac{1}{314}}$    | $f_{IF} = \frac{f_{LO}}{314}$    |

| 365 MHz < f <sub>RF</sub> < 450 MHz, MODE = 1 | $f_{LO} = \frac{f_{RF}}{1 + \frac{1}{432.92}}$ | $f_{IF} = \frac{f_{LO}}{432.92}$ |

7

Figure 3. Input Matching Network with SAW Filter

Figure 4. Input Matching Network without SAW Filter

4663A-RKE-06/03

Please note that for all coupling conditions (see Figure 3 and Figure 4), the bond wire inductivity of the LNA ground is compensated. C3 forms a series resonance circuit together with the bond wire. L=25~nH is a feed inductor to establish a DC path. Its value is not critical but must be large enough not to detune the series resonance circuit. For cost reduction, this inductor can be easily printed on the PCB. This configuration improves the sensitivity of the receiver by about 1 dB to 2 dB.

## **Analog Signal Processing**

### **IF Amplifier**

The signals coming from the RF front end are filtered by the fully integrated 4th-order IF filter. The IF center frequency is  $f_{\rm IF}=1$  MHz for applications where  $f_{\rm RF}=315$  MHz or  $f_{\rm RF}=433.92$  MHz is used. For other RF input frequencies, refer to Table 1 to determine the center frequency.

The receiver U3745BM employs an IF bandwidth of  $B_{\rm IF}$  = 600 kHz. This IC can be used together with the U2745B. SAW transmitters exhibit much higher transmit frequency tolerances compared to PLL transmitters. Generally, it is necessary to use  $B_{\rm IF}$  = 600 kHz together with such transmitters.

### **RSSI Amplifier**

The subsequent RSSI amplifier enhances the output signal of the IF amplifier before it is fed into the demodulator. The dynamic range of this amplifier is  $DR_{RSSI} = 60$  dB. If the RSSI amplifier is operated within its linear range, the best S/N ratio is maintained in ASK mode. If the dynamic range is exceeded by the transmitter signal, the S/N ratio is defined by the ratio of the maximum RSSI output voltage and the RSSI output voltage due to a disturber. The dynamic range of the RSSI amplifier is exceeded if the RF input signal is about 60 dB higher compared to the RF input signal at full sensitivity.

Since different RF input networks may exhibit slightly different values for the LNA gain, the sensitivity values given in the electrical characteristics refer to a specific input matching. This matching is illustrated in Figure 4 and exhibits the best possible sensitivity.

# Demodulator and Data Filter

The signal coming from the RSSI amplifier is converted into the raw data signal by the ASK demodulator.

In ASK mode, an automatic threshold control circuit (ATC) is employed to set the detection reference voltage to a value where a good signal-to-noise ratio is achieved. This circuit also implies the effective suppression of any kind of in-band noise signals or competing transmitters. If the S/N ratio exceeds 10 dB, the data signal can be detected properly.

The output signal of the demodulator is filtered by the data filter before it is fed into the digital signal processing circuit. The data filter improves the S/N ratio as its bandpass can be adopted to the characteristics of the data signal. The data filter consists of a 1st-order high-pass and a 1st-order low-pass filter.

The high-pass filter cut-off frequency is defined by an external capacitor connected to pin CDEM. The cut-off frequency of the high-pass filter is defined by the following formula:

$$f_{cu\_DF} = \frac{1}{2 \times \pi \times 30 \text{ k}\Omega \times \text{CDEM}}$$

In self-polling mode, the data filter must settle very rapidly to achieve a low current consumption. Therefore, CDEM cannot be increased to very high values if self polling is used. On the other hand, CDEM must be large enough to meet the data filter requirements according to the data signal. Recommended values for CDEM are given in the section "Electrical Characteristics".

The cut-off frequency of the low-pass filter is defined by the selected baud rate range (BR\_Range). BR\_Range is defined in the OPMODE register (refer to section "Configuration of the Receiver"). BR\_Range must be set in accordance to the used baud rate.

The U3745BM is designed to operate with data coding where the DC level of the data signal is 50%. This is valid for Manchester and Bi-phase coding. If other modulation schemes are used, the DC level should always remain within the range of  $V_{DC\_min} = 33\%$  and  $V_{DC\_max} = 66\%$ . The sensitivity may be reduced by up to 1.5 dB in that condition.

Each BR\_Range is also defined by a minimum and a maximum edge-to-edge time  $(t_{ee\_sig})$ . These limits are defined in the section "Electrical Characteristics". They should not be exceeded to maintain full sensitivity of the receiver.

# Receiving Characteristics

The RF receiver U3745BM can be operated with and without a SAW front end filter. The selectivity with and without a SAW front-end filter is illustrated in Figure 5. This example relates to ASK mode of the U3745BM. Note that the mirror frequency is reduced by 40 dB. The plots are printed relatively to the maximum sensitivity. If a SAW filter is used, an insertion loss of about 4 dB must be considered.

When designing the system in terms of receiving bandwidth, the LO deviation must be considered as it also determines the IF center frequency. The total LO deviation is calculated to be the sum of the deviation of the crystal and the XTO deviation of the U3745BM. Low-cost crystals are specified to be within  $\pm 100$  ppm. The XTO deviation of the U3745BM is an additional deviation due to the XTO circuit. This deviation is specified to be  $\pm 50$  ppm. If a crystal of  $\pm 100$  ppm is used, the total deviation is  $\pm 150$  ppm in that case. Note that the receiving bandwidth and the IF-filter bandwidth are equivalent in ASK mode.

Figure 5. Receiving Frequency Response

## **Polling Circuit and Control Logic**

The receiver is designed to consume less than 1 mA while being sensitive to signals from a corresponding transmitter. This is achieved via the polling circuit. This circuit enables the signal path periodically for a short time. During this time the bit check logic verifies the presence of a valid transmitter signal. Only if a valid signal is detected the receiver remains active and transfers the data to the connected microcontroller. If there is no valid signal present, the receiver is in sleep mode most of the time resulting in low current consumption. This condition is called polling mode. A connected microcontroller is disabled during that time.

All relevant parameters of the polling logic can be configured by the connected microcontroller. This flexibility enables the user to meet the specifications in terms of current consumption, system response time, data rate etc.

Regarding the number of connection wires to the  $\mu$ C, the receiver is very flexible. It can be either operated by a single bi-directional line to save ports to the connected microcontroller, or it can be operated by up to three uni-directional ports.

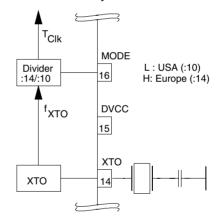

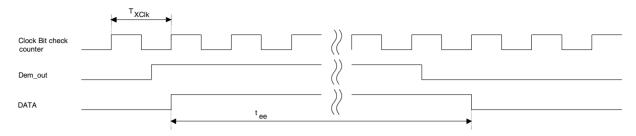

## Basic Clock Cycle of the Digital Circuitry

The complete timing of the digital circuitry and the analog filtering is derived from one clock. According to Figure 6, this clock cycle  $T_{Clk}$  is derived from the crystal oscillator (XTO) in combination with a divider. The division factor is controlled by the logical state at pin MODE. According to section "RF Front End", the frequency of the crystal oscillator ( $f_{XTO}$ ) is defined by the RF input signal ( $f_{RFin}$ ) which also defines the operating frequency of the local oscillator ( $f_{LO}$ ).

Figure 6. Generation of the Basic Clock Cycle

Pin MODE can now be set in accordance with the desired clock cycle  $T_{Clk}$ .  $T_{Clk}$  controls the following application-relevant parameters:

- Timing of the polling circuit including bit check

- Timing of analog and digital signal processing

- Timing of register programming

- Frequency of the reset marker

- F filter center frequency (f<sub>IFO</sub>)

Most applications are dominated by two transmission frequencies:  $f_{Send}$  = 315 MHz is mainly used in the USA,  $f_{Send}$  = 433.92 MHz in Europe. In order to ease the usage of all  $T_{Clk}$ -dependent parameters, the electrical characteristics display three conditions for each parameter.

**USA** Applications

$$(f_{XTO} = 4.90625 \text{ MHz}, MODE = L, T_{Clk} = 2.0383 \mu s)$$

**Europe Applications**

$$(f_{XTO} = 6.76438 \text{ MHz}, MODE = H, T_{Clk} = 2.0697 \mu s)$$

Other applications

$(T_{\text{Clk}} \text{ is dependent on } f_{\text{XTO}} \text{ and on the logical state of pin MODE.}$  The electrical characteristic is given as a function of  $T_{Clk}$ ).

The clock cycle of some function blocks depends on the selected baud rate range (BR Range) which is defined in the OPMODE register. This clock cycle  $T_{XCIk}$  is defined by the following formulas for further reference:

$$BR\_Range = BR\_Range0: T_{XClk} = 8 \times T_{Clk}$$

BR\_Range1:  $T_{XCIk} = 4 \times T_{CIk}$ BR\_Range2:  $T_{YCIL} = 2 \times T_{CIL}$

BR\_Range3:  $T_{XCIk} = 1 \times T_{CIk}$

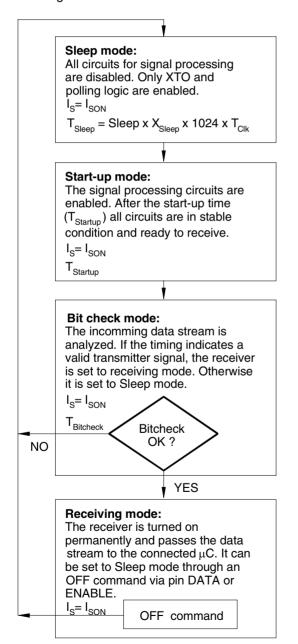

### **Polling Mode**

According to Figure 3, the receiver stays in polling mode in a continuous cycle of three different modes. In sleep mode, the signal processing circuitry is disabled for the time period  $T_{Sleep}$  while consuming low current of  $I_S = I_{Soff}$ . During the start-up period,  $T_{Startup}$ , all signal processing circuits are enabled and settled. In the following bit check mode, the incoming data stream is analyzed bit by bit contra a valid transmitter signal. If no valid signal is present, the receiver is set back to sleep mode after the period T<sub>Bitcheck</sub>. This period varies check by check as it is a statistical process. An average value for T<sub>Bitcheck</sub> is given in the section "Electrical Characteristics". During T<sub>Startup</sub> and T<sub>Bitcheck</sub> the current consumption is  $I_S = I_{Son}$ . The average current consumption in polling mode is dependent on the duty cycle of the active mode and can be calculated as:

$$I_{Spoll} = \frac{I_{Soff} \times T_{Sleep} + I_{Son} \times (T_{Startup} + T_{Bitcheck})}{T_{Sleep} + T_{Startup} + T_{Bitcheck}}$$

During T<sub>Sleep</sub> and T<sub>Startup</sub>, the receiver is not sensitive to a transmitter signal. To guarantee the reception of a transmitted command, the transmitter must start the telegram with an adequate preburst. The required length of the preburst is dependent on the polling parameters  $T_{Sleep}$ ,  $T_{Startup}$ ,  $T_{Bitcheck}$  and the startup time of a connected microcontroller  $(T_{Start, \mu C})$ .  $T_{Bitcheck}$  thus depends on the actual bit rate and the number of bits  $(N_{Bitcheck})$  to be tested.

The following formula indicates how to calculate the preburst length.

$$T_{Preburst} \ge T_{Sleep} + T_{Startup} + T_{Bitcheck} + T_{Start\_\mu C}$$

The length of period T<sub>Sleep</sub> is defined by the 5-bit word Sleep of the OPMODE register, Sleep Mode the extension factor XSleep, according to table 10, and the basic clock cycle T<sub>Clk</sub>. It is calculated to be:

$$T_{Sleep} = Sleep \times X_{Sleep} \times 1024 \times T_{Clk}$$

In US and European applications, the maximum value of  $T_{Sleep}$  is about 60 ms if XSleep is set to 1. The time resolution is about 2 ms in that case. The sleep time can be extended to almost half a second by setting XSleep to 8. XSleep can be set to 8 by bit XSleep<sub>Std</sub> or by bit XSleep<sub>Temp</sub> resulting in a different mode of action as described below:

XSleep<sub>Std</sub> = 1 implies the standard extension factor. The sleep time is always extended.

11

$XSleep_{Temp} = 1$  implies the temporary extension factor. The extended sleep time is used as long as every bit check is OK. If the bit check fails once, this bit is set back to 0 automatically resulting in a regular sleep time. This functionality can be used to save current in presence of a modulated disturber similar to an expected transmitter signal. The connected microcontroller is rarely activated in that condition. If the disturber disappears, the receiver switches back to regular polling and is again sensitive to appropriate transmitter signals.

According to Table 7, the highest register value of Sleep sets the receiver to a permanent sleep condition. The receiver remains in that condition until another value for Sleep is programmed into the OPMODE register. This function is desirable where several devices share a single data line.

Figure 7. Polling Mode Flow Chart

Sleep: 5-bit word defined by Sleep0 to

Sleep4 in OPMODE register

$X_{Sleep}$ : Extension factor defined by  $XSleep_{Temp}$

according to Table 8

$T_{Clk}$ : Basic clock cycle defined by  $f_{XTO}$

and Pin MODE

$T_{Startup}$ : Is defined by the selected baud rate

range and  $T_{\text{Clk}}$ . The baud rate range is defined by Baud0 and Baud1 in

the OPMODE register.

T<sub>Bitcheck</sub>: Depends on the result of the bitcheck

If the bitcheck is ok,  $T_{\text{Bitcheck}}$  depends on the number of bits to be checked ( $N_{\text{Bitchecked}}$ ) and on the utilized data rate.

If the bitcheck fails, the average time period for that check depends on the selected baud rate range and on T<sub>Clk</sub>. The baud rate range is defined by Baud0 and Baud1 in the OPMODE register.

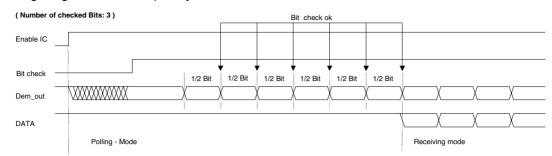

Figure 8. Timing Diagram for a Completely Successful Bit Check

### **Bit Check Mode**

In bit check mode, the incoming data stream is examined to distinguish between a valid signal from a corresponding transmitter and signals due to noise. This is done by subsequent time frame checks where the distances between 2 signal edges are continuously compared to a programmable time window. The maximum count of this edge-to-edge test, before the receiver switches to receiving, mode is also programmable.

#### Configuring the Bit Check

Assuming a modulation scheme that contains 2 edges per bit, two time frame checks are verifying one bit. This is valid for Manchester, Bi-phase and most other modulation schemes. The maximum count of bits to be checked can be set to 0, 3, 6 or 9 bits via the variable  $N_{\text{Bitcheck}}$  in the OPMODE register. This implies 0, 6, 12 and 18 edge-to-edge checks respectively. If  $N_{\text{Bitcheck}}$  is set to a higher value, the receiver is less likely to switch to the receiving mode due to noise. In the presence of a valid transmitter signal, the bit check takes less time if  $N_{\text{Bitcheck}}$  is set to a lower value. In polling mode, the bit check time is not dependent on  $N_{\text{Bitcheck}}$ . Figure 8 shows an example where 3 bits are tested successfully and the data signal is transferred to Pin DATA.

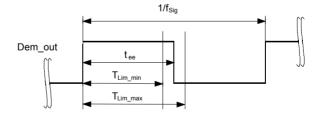

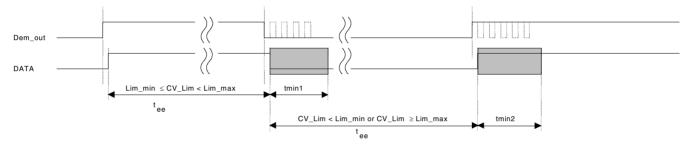

According to Figure 9, the time window for the bit check is defined by two separate time limits. If the edge-to-edge time  $t_{ee}$  is in between the lower bit check limit  $T_{Lim\_min}$  and the upper bit check limit  $T_{Lim\_max}$ , the check will be continued. If  $t_{ee}$  is smaller than  $T_{Lim\_min}$  or  $t_{ee}$  exceeds  $T_{Lim\_max}$ , the bit check will be terminated and the receiver switches to sleep mode.

Figure 9. Valid Time Window for Bit Check

For best noise immunity it is recommended to use a low span between  $T_{\text{Lim\_min}}$  and  $T_{\text{Lim\_max}}$ . This is achieved using a fixed frequency at a 50% duty cycle for the transmitter preburst. A '11111...' or a '10101...' sequence in Manchester or Bi-phase is a good choice in this regard. A good compromise between receiver sensitivity and susceptibility to noise is a time window of  $\pm$  25% regarding the expected edge-to-edge time  $t_{ee}$ . Using preburst patterns that contain various edge-to-edge time periods, the bit check limits must be programmed according to the required span.

The bit check limits are determined by means of the formula below:

$$\begin{split} T_{\text{Lim\_min}} &= \text{Lim\_min} \times T_{\text{XClk}} \\ T_{\text{Lim\_max}} &= (\text{Lim\_max} - 1) \times T_{\text{XClk}} \end{split}$$

Lim\_min and Lim\_max are defined by a 5-bit word each within the LIMIT register.

Using the above formulas, Lim\_min and Lim\_max can be determined according to the required  $T_{\text{Lim\_min}}$ ,  $T_{\text{Lim\_max}}$  and  $T_{\text{XClk}}$ . The time resolution when defining  $T_{\text{Lim\_min}}$  and  $T_{\text{Lim\_max}}$  is  $T_{\text{XClk}}$ . The minimum edge-to-edge time  $t_{\text{ee}}$  ( $t_{\text{DATA\_L\_min}}$ ,  $t_{\text{DATA\_H\_min}}$ ) is defined according to the section "Receiving Mode". Due to this, the lower limit should be set to Lim\_min  $\geq 10$ . The maximum value of the upper limit is Lim\_max = 63.

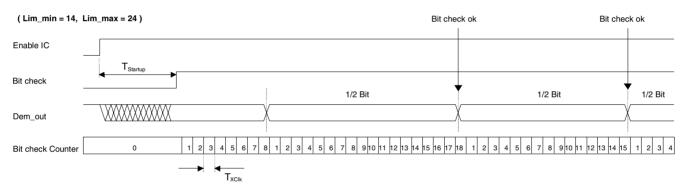

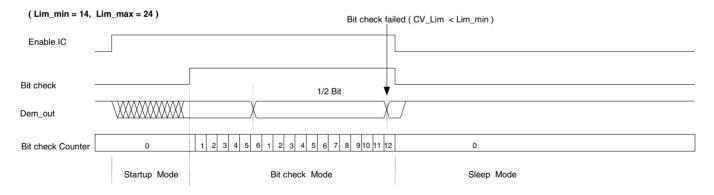

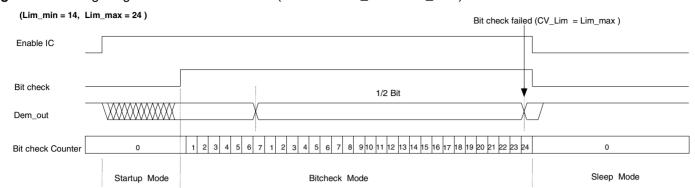

Figure 10, Figure 11 and Figure 12 illustrate the bit check for the default bit check limits  $Lim_min = 14$  and  $Lim_max = 24$ . When the IC is enabled, the signal processing circuits are enabled during  $T_{Startup}$ . The output of the demodulator (Dem\_out) is undefined during that period. When the bit check becomes active, the bit check counter is clocked with the cycle  $T_{XClk}$ .

Figure 10 shows how the bit check proceeds if the bit-check counter value CV\_Lim is within the limits defined by Lim\_min and Lim\_max at the occurrence of a signal edge. In Figure 12, the bit check fails as the value CV\_lim is lower than the limit Lim\_min. The bit check also fails if CV\_Lim reaches Lim\_max. This is illustrated in Figure 13.

Figure 10. Timing Diagram During Bit Check

Figure 11. Timing Diagram for Failed Bit Check (Condition: CV\_Lim < Lim\_min)

Figure 12. Timing Diagram for Failed Bit Check (condition: CV Lim ≥ Lim max)

#### **Duration of the Bit Check**

If no transmitter signal is present during the bit check, the output of the demodulator delivers random signals. The bit check is a statistical process and  $T_{Bitcheck}$  varies for each check. Therefore, an average value for  $T_{Bitcheck}$  is given in the section "Electrical Characteristics".  $T_{Bitcheck}$  depends on the selected baud rate range and on  $T_{Clk}$ . A higher baudrate range causes a lower value for  $T_{Bitcheck}$  resulting in lower current consumption in polling mode.

In the presence of a valid transmitter signal,  $T_{Bitcheck}$  is dependant on the frequency of that signal,  $f_{Sig}$  and the count of the checked bits,  $N_{Bitcheck}$ . A higher value for  $N_{Bitcheck}$  thereby results in a longer period for  $T_{Bitcheck}$  requiring a higher value for the transmitter preburst  $T_{Preburst}$ .

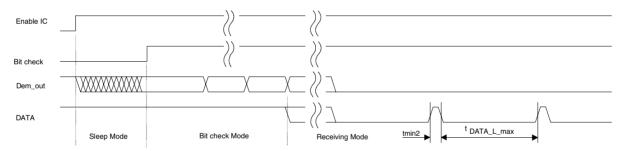

### **Receiving Mode**

If the bit check has been successful for all bits specified by  $N_{Bitcheck}$ , the receiver switches to receiving mode. According to Figure 9, the internal data signal is switched to pin DATA in that case. A connected microcontroller can be woken up by the negative edge at pin DATA. The receiver stays in that condition until it is switched back to polling mode explicitly.

#### **Digital Signal Processing**

The data from the demodulator (Dem\_out) is digitally processed in different ways and as a result converted into the output signal data. This processing depends on the selected baud rate range (BR\_Range). Figure 13 illustrates how Dem\_out is synchronized by the extended clock cycle  $T_{XClk}$ . This clock is also used for the bit check counter. Data can change its state only after  $T_{XClk}$  elapsed. The edge-to-edge time period  $t_{ee}$  of the Data signal as a result is always an integral multiple of  $T_{XClk}$ .

The minimum time period between two edges of the data signal is limited to  $t_{ee} \geq T_{DATA\_min}.$  This implies an efficient suppression of spikes at the DATA output. At the same time, it limits the maximum frequency of edges at DATA. This eases the interrupt handling of a connected microcontroller.  $T_{DATA\_min}$  is to some extent affected by the preceding edge-to-edge time interval  $t_{ee}$  as illustrated in Figure 14. If  $t_{ee}$  is in between the specified bit check limits, the following level is frozen for the time period  $T_{DATA\_min} = tmin1$ , in case of  $t_{ee}$  being outside that bit check limits  $T_{DATA\_min} = tmin2$  is the relevant stable time period.

The maximum time period for DATA to be low is limited to  $T_{DATA\_L\_max}$ . This function ensures a finite response time during programming or switching off the receiver via pin DATA.  $T_{DATA\_L\_max}$  is thereby longer than the maximum time period indicated by the transmitter data stream. Figure 15 gives an example where Dem\_out remains low after the receiver has switched to receiving mode.

Figure 13. Synchronization of the Demodulator Output

Figure 14. Debouncing of the Demodulator Output

Figure 15. Steady L State Limited DATA Output Pattern after Transmission

After the end of a data transmission, the receiver remains active and random noise pulses appear at pin DATA. The edge-to-edge time period  $t_{ee}$  of the majority of these noise pulses is equal to or slightly higher than  $T_{DATA\ min}$ .

# Switching the Receiver Back to Sleep Mode

The receiver can be set back to polling mode via pin DATA or via pin ENABLE.

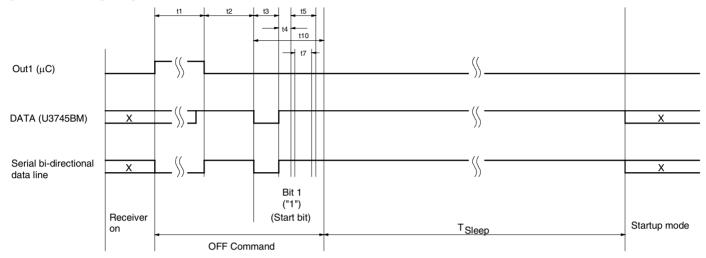

When using pin DATA, this pin must be pulled to Low for the period t1 by the connected microcontroller. Figure 16 illustrates the timing of the OFF command (see also Figure 20). The minimum value of t1 depends on the BR\_Range. The maximum value for t1 is not limited but it is recommended not to exceed the specified value to prevent erasing the reset marker. This item is explained in more detail in the section "Configuration of the Receiver". Setting the receiver to sleep mode via DATA is achieved by programming bit 1 of the OPMODE register to 1. Only one sync pulse (t3) is issued.

The duration of the OFF command is determined by the sum of t1, t2 and t10. After the OFF command, the sleep time  $T_{Sleep}$  elapses. Note that the capacitive load at Pin DATA is limited. The resulting time constant t together with an optional external pull-up resistor may not be exceeded to ensure proper operation.

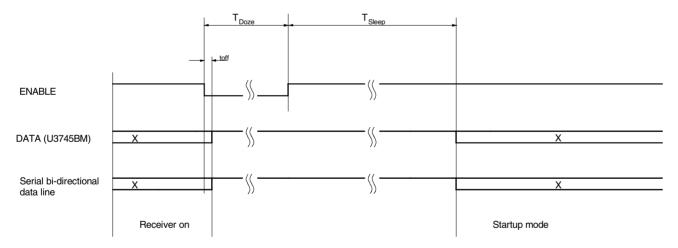

If the receiver is set to polling mode via pin ENABLE, an 'L' pulse  $(T_{Doze})$  must be issued at that pin. Figure 17 illustrates the timing of that command. After the positive edge of

this pulse, the sleep time  $T_{Sleep}$  elapses. The receiver remains in sleep mode as long as ENABLE is held to 'L'. If the receiver is polled exclusively by a microcontroller,  $T_{Sleep}$  can be programmed to 0 to enable a instantaneous response time. This command is the faster option than via pin DATA at the cost of an additional connection to the microcontroller.

Figure 16. Timing Diagram of the OFF Command Via Pin DATA

Figure 17. Timing Diagram of the OFF Command Via Pin ENABLE

### Configuration of the Receiver

The U3745BM receiver is configured via two 12-bit RAM registers called OPMODE and LIMIT. The registers can be programmed by means of the bi-directional DATA port. If the register contents have changed due to a voltage drop, this condition is indicated by a certain output pattern called reset marker (RM). The receiver must be reprogrammed in that case. After a power-on reset (POR), the registers are set to default mode. If the receiver is operated in default mode, there is no need to program the registers.

Table 3 shows the structure of the registers. According to Table 2, bit 1 defines if the receiver is set back to polling mode via the OFF command, (see section "Receiving Mode") or if it is programmed. Bit 2 represents the register address. It selects the appropriate register to be programmed.

Table 2. Effect of Bit 1 and Bit 2 in Programming the Registers

| Bit 1 | Bit 2 | Action                                                 |

|-------|-------|--------------------------------------------------------|

| 1     | x     | The receiver is set back to polling mode (OFF command) |

| 0     | 1     | The OPMODE register is programmed                      |

| 0     | 0     | The LIMIT register is programmed                       |

Table 4 and the following illustrate the effect of the individual configuration words. The default configuration is highlighted for each word.

BR\_Range sets the appropriate baud rate range. At the same time it defines XLim. XLim is used to define the bit check limits  $T_{Lim\_min}$  and  $T_{Lim\_max}$  as shown in Table 4.

POUT can be used to control the sensitivity of the receiver. In that application, POUT is set to 1 to reduce the sensitivity. This implies that the receiver operates with full sensitivity after a POR.

**Table 3.** Effect of the Configuration Words within the Registers

| Bit1  | Bit2        | Bit2     | Bit4     | Bit5             | Bit6     | Bit7              | Bit8     | Bit9     | Bit10    | Bit11    | Bit12    | Bit13                  | Bit14                   |

|-------|-------------|----------|----------|------------------|----------|-------------------|----------|----------|----------|----------|----------|------------------------|-------------------------|

| OFF ( | OFF Command |          |          |                  |          |                   |          |          |          |          |          |                        |                         |

| 1     |             |          |          |                  |          |                   |          |          |          |          |          |                        |                         |

| ОРМО  | DDE R       | egister  |          |                  |          |                   |          |          |          |          |          |                        |                         |

| 0     | 1           | BR_F     | Range    | N <sub>Bit</sub> | check    | V <sub>POUT</sub> |          |          | Sleep    |          |          | XS                     | leep                    |

| 0     | 1           | Baud1    | Baud0    | BitChk1          | BitChk0  | POUT              | Sleep4   | Sleep3   | Sleep2   | Sleep1   | Sleep0   | X <sub>Sleep Std</sub> | X <sub>Sleep Temp</sub> |

| (De   | fault)      | 0        | 0        | 1                | 0        | 0                 | 0        | 1        | 0        | 1        | 1        | 0                      | 0                       |

| LIMIT | Regis       | ster     |          |                  |          |                   |          |          |          |          |          |                        | 1                       |

| 0     | 0           |          |          | Lim              | _min     |                   |          | Lim_max  |          |          |          |                        |                         |

| 0     | 0           | Lim_min5 | Lim_min4 | Lim_min3         | Lim_min2 | Lim_min1          | Lim_min0 | Lim_max5 | Lim_max4 | Lim_max3 | Lim_max2 | Lim_max1               | Lim_max0                |

| (De   | fault)      | 0        | 0        | 1                | 1        | 1                 | 0        | 0        | 1        | 1        | 0        | 0                      | 0                       |

Table 4. Effect of the Configuration Word BR\_Range

| BR_F  | lange |                                                                                                     |

|-------|-------|-----------------------------------------------------------------------------------------------------|

| Baud1 | Baud0 | Baudrate Range/Extension Factor for Bit Check Limits (XLim)                                         |

| 0     | 0     | BR_Range0 (application USA/Europe: BR_Range0 = 1.0 kBaud to 1.8 kBaud) (Default) XLim = 8 (Default) |

| 0     | 1     | BR_Range1 (application USA/Europe: BR_Range1 = 1.8 kBaud to 3.2 kBaud) XLim = 4                     |

| 1     | 0     | BR_Range2 (application USA/Europe: BR_Range2 = 3.2 kBaud to 5.6 kBaud) XLim = 2                     |

| 1     | 1     | BR_Range3 (Application USA/Europe: BR_Range3 = 5.6 kBaud to 10 kBaud) XLim = 1                      |

Table 5. Effect of the Configuration Word N<sub>Bitcheck</sub>

| N <sub>Bi</sub> | check   |                              |

|-----------------|---------|------------------------------|

| BitChk1         | BitChk0 | Number of Bits to be Checked |

| 0               | 0       | 0                            |

| 0               | 1       | 3                            |

| 1               | 0       | 6 (Default)                  |

| 1               | 1       | 9                            |

Table 6. Effect of the Configuration Bit VPOUT

| VPOUT | Level of the Multi-purpose Output Port POUT |

|-------|---------------------------------------------|

| POUT  |                                             |

| 0     | 0 (Default)                                 |

| 1     | 1                                           |

Table 7. Effect of the Configuration Word Sleep

|        |        | Sleep  |        |        |                                                                                   |

|--------|--------|--------|--------|--------|-----------------------------------------------------------------------------------|

| Sleep4 | Sleep3 | Sleep2 | Sleep1 | Sleep0 | Start Value for Sleep Counter ( $T_{Sleep}$ = Sleep × Xsleep × 1024 × $T_{Clk}$ ) |

| 0      | 0      | 0      | 0      | 0      | 0 (Receiver is continuously polling until a valid signal occurs)                  |

| 0      | 0      | 0      | 0      | 1      | 1 ( $T_{Sleep} \approx 2ms$ for XSleep = 1 in US-/European applications)          |

| 0      | 0      | 0      | 1      | 0      | 2                                                                                 |

| 0      | 0      | 0      | 1      | 1      | 3                                                                                 |

|        |        |        |        |        |                                                                                   |

| -      | •      | -      | •      |        |                                                                                   |

| •      | •      | •      |        |        |                                                                                   |

| 0      | 1      | 0      | 1      | 1      | 11 (USA: $T_{Sleep}$ = 22.96 ms, Europe: $T_{Sleep}$ = 23.31 ms) (Default)        |

|        |        |        |        |        |                                                                                   |

|        |        | -      |        |        |                                                                                   |

|        |        |        |        |        |                                                                                   |

| 1      | 1      | 1      | 0      | 1      | 29                                                                                |

| 1      | 1      | 1      | 1      | 0      | 30                                                                                |

| 1      | 1      | 1      | 1      | 1      | 31 (Permanent sleep mode)                                                         |

Table 8. Effect of the Configuration Word XSleep

| XS                    | leep                   |                                                                                     |  |  |  |

|-----------------------|------------------------|-------------------------------------------------------------------------------------|--|--|--|

| XSleep <sub>Std</sub> | XSIeep <sub>Temp</sub> | Extension Factor for Sleep Time ( $T_{Sleep}$ = Sleep × Xsleep × 1024 × $T_{Clk}$ ) |  |  |  |

| 0                     | 0                      | 1 (Default)                                                                         |  |  |  |

| 0                     | 1                      | 8 (XSleep is reset to 1 if bit check fails once)                                    |  |  |  |

| 1                     | 0                      | 8 (XSleep is set permanently)                                                       |  |  |  |

| 1                     | 1                      | 8 (XSleep is set permanently)                                                       |  |  |  |

Table 9. Effect of the Configuration Word Lim\_min

|   |                                | Lim | _min |   |   | Lower Limit Value for Bit Check                                                    |

|---|--------------------------------|-----|------|---|---|------------------------------------------------------------------------------------|

|   | Lim_min < 10 is not applicable |     |      |   |   | $(T_{\text{Lim\_min}} = \text{Lim\_min} \times \text{XLim} \times T_{\text{Clk}})$ |

| 0 | 0                              | 1   | 0    | 1 | 0 | 10                                                                                 |

| 0 | 0                              | 1   | 0    | 1 | 1 | 11                                                                                 |

| 0 | 0                              | 1   | 1    | 0 | 0 | 12                                                                                 |

| 0 | 0                              | 1   | 1    | 0 | 1 | 13                                                                                 |

| 0 | 0                              | 1   | 1    | 1 | 0 | 14 (Default)                                                                       |

|   |                                |     |      |   |   | (USA: $T_{Lim\_min} = 228 \mu s$ , Europe: $T_{Lim\_min} = 232 \mu s$ )            |

|   |                                |     |      |   |   |                                                                                    |

| • |                                |     |      |   |   |                                                                                    |

|   |                                |     |      |   |   |                                                                                    |

| 1 | 1                              | 1   | 1    | 0 | 1 | 61                                                                                 |

| 1 | 1                              | 1   | 1    | 1 | 0 | 62                                                                                 |

| 1 | 1                              | 1   | 1    | 1 | 1 | 63                                                                                 |

Table 10. Effect of the Configuration Word Lim max

|   |                                | Lim_ | _max |   |   | Upper Limit Value for Bit Check                                         |  |  |

|---|--------------------------------|------|------|---|---|-------------------------------------------------------------------------|--|--|

|   | Lim_max < 12 is not applicable |      |      |   |   | $(T_{Lim\_max} = (Lim\_max - 1) \times XLim \times T_{Clk})$            |  |  |

| 0 | 0                              | 1    | 1    | 0 | 0 | 12                                                                      |  |  |

| 0 | 0                              | 1    | 1    | 0 | 1 | 13                                                                      |  |  |

| 0 | 0                              | 1    | 1    | 1 | 0 | 14                                                                      |  |  |

|   |                                |      |      |   |   |                                                                         |  |  |

|   | -                              | -    |      | - |   |                                                                         |  |  |

| • | •                              |      |      |   |   |                                                                         |  |  |

| 0 | 1                              | 1    | 0    | 0 | 0 | 24 (Default)                                                            |  |  |

|   |                                |      |      |   |   | (USA: $T_{Lim\_max} = 375 \mu s$ , Europe: $T_{Lim\_max} = 381 \mu s$ ) |  |  |

|   |                                |      |      |   |   |                                                                         |  |  |

|   | •                              | •    |      | • |   |                                                                         |  |  |

|   |                                |      |      |   |   |                                                                         |  |  |

| 1 | 1                              | 1    | 1    | 0 | 1 | 61                                                                      |  |  |

| 1 | 1                              | 1    | 1    | 1 | 0 | 62                                                                      |  |  |

| 1 | 1                              | 1    | 1    | 1 | 1 | 63                                                                      |  |  |

# Conservation of the Register Information

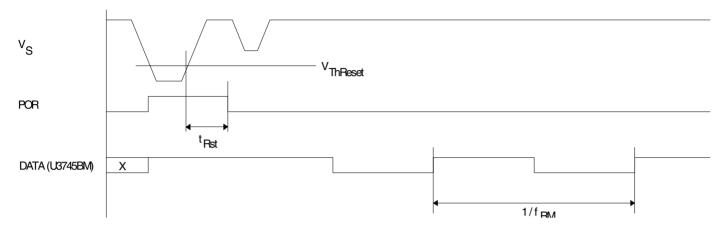

The U3745BM has an integrated power-on reset and brown-out detection circuitry to provide a mechanism to preserve the RAM register information.

According to Figure 18, a power-on reset (POR) is generated if the supply voltage  $V_S$  drops below the threshold voltage  $V_{ThReset}$ . The default parameters are programmed into the configuration registers in that condition. Once  $V_S$  exceeds  $V_{ThReset}$ , the POR is canceled after the minimum reset period  $t_{Rst}$ . A POR is also generated when the supply voltage of the receiver is turned on.

To indicate that condition, the receiver displays a reset marker (RM) at pin DATA after a reset. The RM is represented by the fixed frequency  $f_{RM}$  at a 50% duty cycle. RM can be canceled via an 'L' pulse t1 at pin DATA. The RM implies the following characteristics:

f<sub>RM</sub> is lower than the lowest feasible frequency of a data signal. By this means, RM cannot be misinterpreted by the connected microcontroller.

• If the receiver is set back to polling mode via pin DATA, RM cannot be canceled by accident if t1 is applied according to the proposal in the section "Programming the Configuration Registers".

By means of that mechanism, the receiver cannot lose its register information without communicating that condition via the reset marker RM.

Figure 18. Generation of the Power-on Reset

Figure 19. Timing of the Register Programming

Programming the Configuration Register

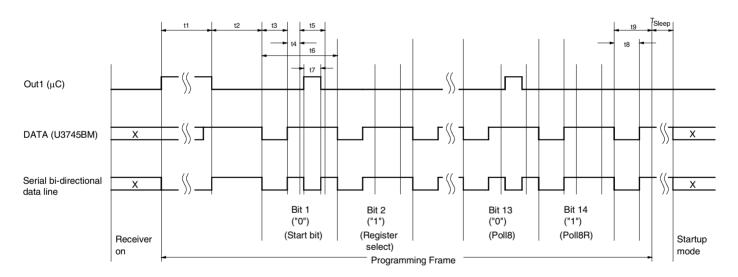

The configuration registers are programmed serially via the bi-directional data line according to Figure 19 and Figure 20.

Figure 20. One-wire Connection to a Microcontroller

To start programming, the serial data line DATA is pulled to 'L' for the time period t1 by the microcontroller. When DATA has been released, the receiver becomes the master device. When the programming delay period t2 has elapsed, it emits 14 subsequent synchronization pulses with the pulse length t3. After each of these pulses, a programming window occurs. The delay until the program window starts is determined by t4, the duration is defined by t5. Within the programming window, the individual bits are set. If the microcontroller pulls down pin DATA for the time period t7 during t5, the according bit is set to '0'. If no programming pulse t7 is issued, this bit is set to '1'. All 14 bits are subsequently programmed in this way. The time frame to program a bit is defined by t6.

Bit 14 is followed by the equivalent time window t9. During this window, the equivalent acknowledge pulse t8 (E\_Ack) occurs if the mode word just programmed is equivalent to the mode word that was already stored in that register. E\_Ack should be used to verify that the mode word was correctly transferred to the register. The register must be programmed twice in that case.

Programming of a register is possible both during sleep and active mode of the receiver.

During programming, the LNA, LO, lowpass filter, IF-amplifier and the demodulator are disabled.

The programming start pulse t1 initiates the programming of the configuration registers. If bit 1 is set to '1', it represents the OFF command to set the receiver back to polling mode at the same time. For the length of the programming start pulse t1, the following convention should be considered:

•  $t1(min) < t1 < 1535 \times T_{Clk}$ : [t1(min) is the minimum specified value for the relevant BR\_Range]

Programming (respectively OFF command) is initiated if the receiver is not in reset mode. If the receiver is in reset mode, programming (respectively Off command) is not initiated, and the reset marker RM is still present at pin DATA.

This period is generally used to switch the receiver to polling mode. In a reset condition, RM is not canceled by accident.

•  $t1 > 5632 \times T_{Clk}$

Programming (respectively OFF command) is initiated in any case. RM is cancelled if present. This period is used if the connected microcontroller detected RM. If a configuration register is programmed, this time period for t1 can generally be used.

Note that the capacitive load at pin DATA is limited. The resulting time constant t together with an optional external pull-up resistor may not be exceeded to ensure proper operation.

# **Absolute Maximum Ratings**

| Parameters                                        | Symbol              | Min. | Max. | Unit |

|---------------------------------------------------|---------------------|------|------|------|

| Supply voltage                                    | V <sub>S</sub>      |      | 6    | V    |

| Power dissipation                                 | P <sub>tot</sub>    |      | 450  | mW   |

| Junction temperature                              | T <sub>j</sub>      |      | 150  | °C   |

| Storage temperature                               | T <sub>stg</sub>    | -55  | +125 | °C   |

| Ambient temperature                               | T <sub>amb</sub>    | -40  | +85  | °C   |

| Maximum input level, input matched to 50 $\Omega$ | P <sub>in_max</sub> |      | 10   | dBm  |

### **Thermal Resistance**

| Parameters       | Symbol     | Value | Unit |

|------------------|------------|-------|------|

| Junction ambient | $R_{thJA}$ | 100   | K/W  |

## **Electrical Characteristics**

| Parameters                                        | Test Conditions                                                                                                       | Symbol               | Min. | Тур.                      | Max. | Unit                                             |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------|---------------------------|------|--------------------------------------------------|

|                                                   | Sleep mode<br>(XTO and polling logic active)                                                                          | IS <sub>off</sub>    |      | 190                       | 350  | μΑ                                               |

| Current consumption                               | IC active (startup-, bit check-, receiving mode) Pin DATA = H                                                         | IS <sub>on</sub>     |      | 7.0                       | 8.6  | mA                                               |

| LNA Mixer                                         |                                                                                                                       |                      |      |                           |      |                                                  |

| Third-order intercept point                       | LNA/mixer/IF amplifier input matched according to Figure 4                                                            | IIP3                 |      | -28                       |      | dBm                                              |

| LO spurious emission at RF <sub>In</sub>          | Input matched according to Figure 4, required according to I-ETS 300220                                               | IS <sub>LORF</sub>   |      | -73                       | -57  | dBm                                              |

| Noise figure LNA and mixer (DSB)                  | Input matching according to Figure 4                                                                                  | NF                   |      | 7                         |      | dB                                               |

| LNA_IN input impedance                            | at 433.92 MHz<br>at 315 MHz                                                                                           | Zi <sub>LNA_IN</sub> |      | 1.0    1.56<br>1.3    1.0 |      | $k\Omega \parallel pF$<br>$k\Omega \parallel pF$ |

| 1 dB compression point (LNA, mixer, IF amplifier) | Input matched according to Figure 4, referred to RF <sub>in</sub>                                                     | IP <sub>1db</sub>    |      | -40                       |      | dBm                                              |

| Maximum input level                               | Input matched according to Figure 4, BER $\leq 10^{-3}$ , ASK mode                                                    | P <sub>in_max</sub>  |      |                           | -23  | dBm                                              |

| Local Oscillator                                  |                                                                                                                       |                      |      |                           |      |                                                  |

| Operating frequency range VCO                     |                                                                                                                       | f <sub>vco</sub>     | 309  |                           | 439  | MHz                                              |

| Loop bandwidth of the PLL                         | For best LO noise (design parameter) R1 = 820 $\Omega$ C9 = 4.7 nF C10 = 1 nF                                         | B <sub>Loop</sub>    |      | 100                       |      | kHz                                              |

| Capacitive load at Pin LF                         | The capacitive load at pin LF is limited if bit check is used. The limitation therefore also applies to self polling. | $C_{LF\_tot}$        |      |                           | 10   | nF                                               |

# **Electrical Characteristics (Continued)**

| Parameters                                                                                                                 | Test Conditions                                                                                                                                                                                                                                                                                                                               | Symbol              | Min.                                      | Тур.                  | Max.                                      | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------|-----------------------|-------------------------------------------|----------------------|

| XTO operating frequency                                                                                                    | XTO crystal frequency,<br>appropriate load capacitance must be<br>connected to XTAL<br>6.764375 MHz<br>4.90625 MHz                                                                                                                                                                                                                            | f <sub>xTO</sub>    | 6.764375<br>-50 ppm<br>4.90625<br>-50 ppm | 6.764375<br>4.90625   | 6.764375<br>+50 ppm<br>4.90625<br>+50 ppm | MHz<br>MHz           |

| Series resonance resistor of the crystal                                                                                   | f <sub>XTO</sub> = 6.764 MHz<br>4.906 MHz                                                                                                                                                                                                                                                                                                     | $R_S$               |                                           |                       | 150<br>220                                | Ω                    |

| Static capacitance at Pin XT0                                                                                              |                                                                                                                                                                                                                                                                                                                                               | C <sub>XT0</sub>    |                                           |                       | 6.5                                       | pF                   |

| Analog Signal Processing                                                                                                   |                                                                                                                                                                                                                                                                                                                                               | -                   | - L                                       |                       |                                           |                      |

| Input sensitivity ASK 600-kHz IF filter                                                                                    | Input matched according to figure 6 ASK (level of carrier) BER $\leq 10^{-3}$ , B = 600 kHz $f_{in} = 433.92$ MHz/315 MHz T = 25°C, $V_S = 5$ V $f_{IF} = 1$ MHz                                                                                                                                                                              | $P_{Ref\_ASK}$      |                                           |                       |                                           |                      |

|                                                                                                                            | BR_Range0                                                                                                                                                                                                                                                                                                                                     |                     | -106                                      | -110                  | -113.5                                    | dBm                  |

|                                                                                                                            | BR_Range1                                                                                                                                                                                                                                                                                                                                     |                     | -104.5                                    | -108.5                | -112                                      | dBm                  |

|                                                                                                                            | BR_Range2                                                                                                                                                                                                                                                                                                                                     |                     | -104                                      | -108                  | -111.5                                    | dBm                  |

|                                                                                                                            | BR_Range3                                                                                                                                                                                                                                                                                                                                     |                     | -102                                      | -106                  | -109.5                                    | dBm                  |

| Sensitivity variation ASK for full operating range including IF filter compared to $T_{amb} = 25^{\circ}C$ , $V_{S} = 5$ V | $\begin{array}{l} \textrm{600-kHz version} \\ \textrm{f}_{\textrm{in}} = 433.92 \textrm{ MHz/315 MHz} \\ \textrm{f}_{\textrm{IF}} = 0.81 \textrm{ MHz to 1.19 MHz} \\ \textrm{f}_{\textrm{IF}} = 0.75 \textrm{ MHz to 1.25 MHz} \\ \textrm{P}_{\textrm{ASK}} = \textrm{P}_{\textrm{Ref\_ASK}} + \Delta \textrm{P}_{\textrm{Ref}} \end{array}$ | $\Delta P_{Ref}$    | +3<br>+5                                  |                       |                                           | dB<br>dB             |

| S/N ratio to suppress inband noise signals                                                                                 | ASK mode                                                                                                                                                                                                                                                                                                                                      | SNR <sub>ASK</sub>  |                                           | 11                    |                                           | dB                   |

| Dynamic range RSSI ampl.                                                                                                   |                                                                                                                                                                                                                                                                                                                                               | DR <sub>RSSI</sub>  |                                           | 60                    |                                           | dB                   |

| Lower cut-off frequency of the data filter                                                                                 | $f_{cu\_DF} = \frac{1}{2 \times \pi \times 30 \text{k}\Omega \times \text{CDEM}}$ $CDEM = 33 \text{ nF}$                                                                                                                                                                                                                                      | f <sub>cu_DF</sub>  | 0.11                                      | 0.16                  | 0.20                                      | kHz                  |

| Recommended CDEM for best performance                                                                                      | ASK mode<br>BR_Range0 (Default)<br>BR_Range1<br>BR_Range2<br>BR_Range3                                                                                                                                                                                                                                                                        | CDEM                |                                           | 39<br>22<br>12<br>8.2 |                                           | nF<br>nF<br>nF       |

| Maximum edge-to-edge time period of the input data signal for full sensitivity                                             | BR_Range0 (Default) BR_Range1 BR_Range2 BR_Range3                                                                                                                                                                                                                                                                                             | t <sub>ee_sig</sub> |                                           |                       | 1000<br>560<br>320<br>180                 | μs<br>μs<br>μs<br>μs |

| Minimum edge-to-edge time period of the input data signal for full sensitivity                                             | BR_Range0 (Default) BR_Range1 BR_Range2 BR_Range3                                                                                                                                                                                                                                                                                             | t <sub>ee_sig</sub> |                                           |                       | 270<br>156<br>89<br>50                    | μs<br>μs<br>μs<br>μs |

# **Electrical Characteristics (Continued)**

All parameters refer to GND,  $V_S = 5$  V,  $T_{amb} = 25$ °C,  $f_0 = 433.92$  MHz and  $f_0 = 315$  MHz, unless otherwise specified. The possible operating range refer to different circuit conditions:  $V_S = 4.5$  V to 5.5 V,  $T_{amb} = -40$ °C to +85°C

| Parameters                                                                                                         | Test Conditions                                                                                                                                                    | Symbol                                                                                                            | Min.                 | Тур.                          | Max.                          | Unit                      |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------|-------------------------------|---------------------------|

| Threshold voltage for reset                                                                                        |                                                                                                                                                                    | $V_{ThRESET}$                                                                                                     | 1.95                 | 2.8                           | 3.75                          | V                         |

| Digital Ports                                                                                                      |                                                                                                                                                                    |                                                                                                                   |                      |                               |                               |                           |

| Data output - Saturation voltage LOW - Internal pull-up resistor - Maximum time constant - Maximum capacitive load | $\begin{split} I_{ol} &= 1 \text{ mA} \\ \tau &= C_L \ (R_{pup} /\!/ R_{Ext}) \\ \text{without ext. pull-up resistor} \\ R_{ext} &= 5 \text{ k}\Omega \end{split}$ | $egin{array}{c} {\sf V}_{\sf Ol} \ {\sf R}_{\sf Pup} \ {\sf 	au} \ {\sf C}_{\sf L} \ {\sf C}_{\sf L} \end{array}$ | 39                   | 0.08<br>50                    | 0.3<br>61<br>2.5<br>41<br>540 | V<br>kΩ<br>μs<br>pF<br>pF |

| POUT output - Saturation voltage LOW - Saturation voltage HIGH                                                     | I <sub>POUT</sub> = 1 mA<br>I <sub>POUT</sub> = -1 mA                                                                                                              | $egin{array}{c} V_{Ol} \ V_{Oh} \end{array}$                                                                      | V <sub>S</sub> -0.3V | 0.08<br>V <sub>S</sub> -0.14V | 0.3                           | V<br>V                    |

| ASK input - High-level input voltage                                                                               | ASK                                                                                                                                                                | $V_{lh}$                                                                                                          | 0.8 × V <sub>S</sub> |                               |                               | V                         |

| ENABLE input - Low-level input voltage - High-level input voltage                                                  | Idle mode<br>Active mode                                                                                                                                           | V <sub>II</sub><br>V <sub>Ih</sub>                                                                                | 0.8 × V <sub>S</sub> |                               | 0.2 × V <sub>S</sub>          | V<br>V                    |

| MODE input - Low-level input voltage - High-level input voltage                                                    | Division factor = 10<br>Division factor = 14                                                                                                                       | V <sub>II</sub><br>V <sub>Ih</sub>                                                                                | 0.8 × V <sub>S</sub> |                               | 0.2 × V <sub>S</sub>          | V<br>V                    |

| TEST input<br>- Low-level input voltage                                                                            | Test input must always be set to LOW                                                                                                                               | V <sub>II</sub>                                                                                                   |                      |                               | 0.2 × V <sub>S</sub>          | V                         |

### **Electrical Characteristics**

|                                  |                                                           |                      | 6.76438-Mhz Osc.<br>(Mode 1) |                                                          | 4.9  | 0625-Mhz<br>(Mode 0) |                                                          | V    | ariable Oscillat | or                                                                                                                               |      |                |

|----------------------------------|-----------------------------------------------------------|----------------------|------------------------------|----------------------------------------------------------|------|----------------------|----------------------------------------------------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------|------|----------------|

| Parameter                        | Test Condition                                            | Symbol               | Min.                         | Тур.                                                     | Max. | Min.                 | Тур.                                                     | Max. | Min.             | Тур.                                                                                                                             | Max. | Unit           |

| Basic Clock C                    | ycle of the Digital Cir                                   | rcuitry              |                              |                                                          |      |                      | *                                                        |      |                  |                                                                                                                                  |      | *              |

| Basic clock<br>cycle             | MODE = 0 (USA)<br>MODE = 1<br>(Europe)                    | T <sub>Clk</sub>     |                              | 2.0697                                                   |      |                      | 2.0383                                                   |      |                  | 1/(f <sub>XTO</sub> /10)<br>1/(f <sub>XTO</sub> /14)                                                                             |      | µs<br>µs       |

| Extended<br>basic clock<br>cycle | BR_Range0<br>BR_Range1<br>BR_Range2<br>BR_Range3          | T <sub>XClk</sub>    |                              | 16.6<br>8.3<br>4.1<br>2.1                                |      |                      | 16.3<br>8.2<br>4.1<br>2.0                                |      |                  | $8 \times T_{Clk} \\ 4 \times T_{Clk} \\ 2 \times T_{Clk} \\ 1 \times T_{Clk}$                                                   |      | hs<br>hs<br>hs |

| Polling Mode                     |                                                           |                      | 1                            |                                                          |      |                      | 1                                                        |      |                  |                                                                                                                                  |      | ·L             |

| Sleep time                       | Sleep and XSleep<br>are defined in the<br>OPMODE register | T <sub>Sleep</sub>   |                              | Sleep $\times$ $X_{Sleep} \times$ $1024 \times$ $2.0697$ |      |                      | Sleep $\times$ $X_{Sleep} \times$ $1024 \times$ $2.0383$ |      |                  | $\begin{array}{c} \text{Sleep} \times \\ \text{X}_{\text{Sleep}} \times \\ \text{1024} \times \text{T}_{\text{Clk}} \end{array}$ |      | ms             |

| Start-up time                    | BR_Range0<br>BR_Range1<br>BR_Range2<br>BR_Range3          | T <sub>Startup</sub> |                              | 1855<br>1061<br>1061<br>663                              |      |                      | 1827<br>1045<br>1045<br>653                              |      |                  | 896.5<br>512.5<br>512.5<br>320.5<br>× T <sub>Clk</sub>                                                                           |      | hs<br>hs<br>hs |

# **Electrical Characteristics**