# **TS4985**

## 2x1.2w Stereo Audio Power Amplifier with Dedicated Standby Pins PRODUCT PREVIEW

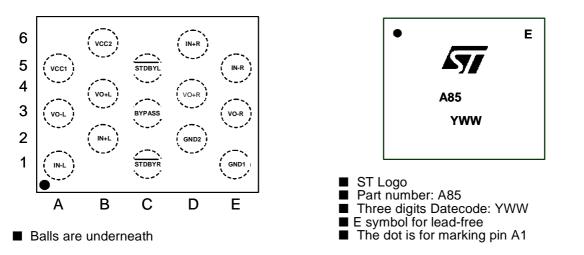

**Pin Connections (top view)**

- Operating from V<sub>CC</sub>=2.2V to 5.5V

- 1.2W output power per channel @ V<sub>CC</sub>=5V, THD+N=1%, RL=8Ω

- 10nA standby current

- 62dB PSRR @ 217Hz with Grounded inputs

- High SNR: 106dB(A) typ.

- Near Zero Pop & Click

- Lead-free 15 bumps flip-chip package

#### Description

The TS4985 has been designed for top of the class stereo audio applications. Thanks to its compact and power dissipation efficient flip-chip package, it suits various applications.

With a BTL configuration, this audio power amplifier is capable of delivering 1.2W per channel of continuous RMS Output Power into an  $8\Omega$  load @ 5V.

Each output channel (Left and Right), has an external controlled standby mode pin (STDBYL&STDBYR) to reduce the supply current to less than 10nA per channel. The device also features an internal thermal shutdown protection.

The gain of each channel can be configured by external gain setting resistors.

#### Applications

- Cellular mobile phones

- Notebook & PDA computers

- LCD monitors & TVs

- Portable audio devices

#### **Order Codes**

|                  | Flip-0  | Chip 15 bi | umps     |  |

|------------------|---------|------------|----------|--|

| (vcc1)<br>(vo-L) | Pin Con | nection (t | op view) |  |

| Part Number              | Temperature Range      | Package   | Packaging   | Marking |

|--------------------------|------------------------|-----------|-------------|---------|

| TS4985EIJT <sup>1</sup>  | -40. +85°C             | Flip-Chip | Tape & Reel |         |

| TS4985EIKJT <sup>2</sup> | -40, <del>1</del> 65 C | Flip-Chip | Tape & Reel |         |

1) **E** = Lead-free Flip-Chip

2)  $K = Back \ coating \ option$

#### November 2004

#### Revision 1

This is preliminary information on a new product now in development. Details are subject to change without notice.

57

## TS4985

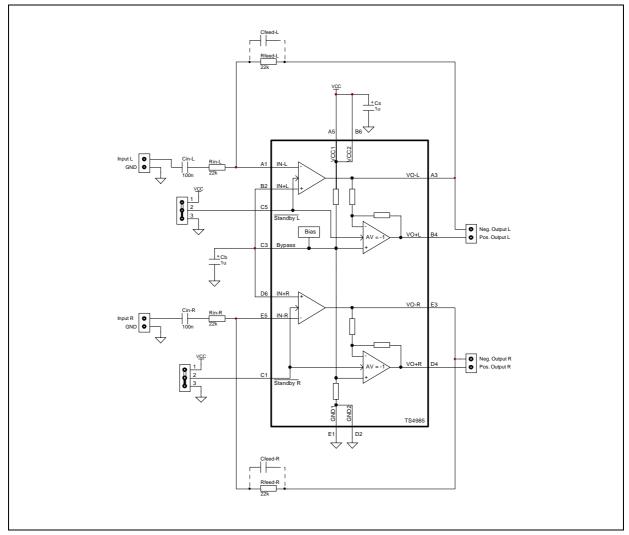

# 1 Application Diagram

## Figure 1 : Typical application schematics

## **Table 1: External Component Descriptions**

| Components                                                                                                                                                                                                | Functional Description                                                                                                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R <sub>IN L,R</sub>                                                                                                                                                                                       | Inverting input resistors which sets the closed loop gain in conjunction with Rfeed. These resistors also form a high pass filter with $C_{IN}$ (fc = 1 / (2 x Pi x $R_{IN} \times C_{IN}$ )) |  |

| C <sub>IN L,R</sub> Input coupling capacitors which blocks the DC voltage at the amplifier input terminal                                                                                                 |                                                                                                                                                                                               |  |

| R <sub>FEED L,R</sub> Feedback resistors which sets the closed loop gain in conjunction with R <sub>IN</sub>                                                                                              |                                                                                                                                                                                               |  |

| C <sub>S</sub>                                                                                                                                                                                            | Supply Bypass capacitor which provides power supply filtering                                                                                                                                 |  |

| C <sub>B</sub> Bypass pin capacitor which provides half supply filtering           A <sub>V L, R</sub> Closed loop gain in BTL configuration = 2 x (R <sub>FEED</sub> / R <sub>IN</sub> ) on each channel |                                                                                                                                                                                               |  |

## 2 Absolute Maximum Ratings

#### Table 2: Key parameters and their absolute maximum ratings

| Symbol            | Parameter                              | Value                              | Unit |

|-------------------|----------------------------------------|------------------------------------|------|

| VCC               | Supply voltage <sup>1</sup>            | 6                                  | V    |

| Vi                | Input Voltage <sup>2</sup>             | G <sub>ND</sub> to V <sub>CC</sub> | V    |

| T <sub>oper</sub> | Operating Free Air Temperature Range   | -40 to + 85                        | °C   |

| T <sub>stg</sub>  | Storage Temperature                    | -65 to +150                        | °C   |

| Тj                | Maximum Junction Temperature           | 150                                | °C   |

| R <sub>thja</sub> | Thermal Resistance Junction to Ambient | tba                                | °C/W |

| Pd                | Power Dissipation                      | Internally Limited                 |      |

| ESD               | Human Body Model <sup>3</sup>          | 2                                  | kV   |

| ESD               | Machine Model                          | 200                                | V    |

|                   | Latch-up Immunity                      | 200mA                              |      |

1) All voltages values are measured with respect to the ground pin.

2) The magnitude of input signal must never exceed V\_{CC} + 0.3V / G\_{ND} - 0.3V.

3) All Voltage values are measured from each pin with respect to supplies.

#### **Table 3: Operating Conditions**

| Symbol           | Parameter                                                        | Value                                                      | Unit |

|------------------|------------------------------------------------------------------|------------------------------------------------------------|------|

| VCC              | Supply Voltage                                                   | 2.2 to 5.5                                                 | V    |

| V <sub>ICM</sub> | Common Mode Input Voltage Range                                  | 1.2V to V <sub>CC</sub>                                    | V    |

| VSTB             | Standby Voltage Input:<br>Device ON<br>Device OFF                | $1.35 \le V_{STB} \le V_{CC}$<br>GND $\le V_{STB} \le 0.4$ | V    |

| RL               | Load Resistor                                                    | ≥ 4                                                        | Ω    |

| ROUT-<br>GND     | Resistor Output to GND (V <sub>STB</sub> = GND)                  | ≥ 1                                                        | MΩ   |

| TSD              | Thermal Shutdown Temperature                                     | 150                                                        | °C   |

| RTHJA            | Thermal Resistance Junction to Ambient<br>Flip Chip <sup>1</sup> | tba                                                        | °C/W |

1) When mounted on a 4-layer PCB.

## TS4985

## **3** Electrical Characteristics

Table 4:  $V_{CC}$  = +5V, GND = 0V,  $T_{amb}$  = 25°C (unless otherwise specified)

| Symbol               | Parameter                                                                                            | Min. | Тур.       | Max. | Unit |

|----------------------|------------------------------------------------------------------------------------------------------|------|------------|------|------|

| I <sub>CC</sub>      | Supply Current<br>No input signal, no load                                                           |      | 7.4        | 12   | mA   |

| I <sub>STANDBY</sub> | Standby Current <sup>1</sup><br>No input signal, Vstdby = $G_{ND}$ , RL = 8 $\Omega$                 |      | 10         | 1000 | nA   |

| Voo                  | Output Offset Voltage<br>No input signal, $RL = 8\Omega$ 110                                         |      | mV         |      |      |

| Po                   | Output Power<br>THD = 1% Max, F = 1kHz, RL = $8\Omega$ 0.91.2                                        |      | W          |      |      |

| THD + N              | Total Harmonic Distortion + Noise<br>Po = 1Wrms, Av = 2, 20Hz $\leq$ F $\leq$ 20kHz, RL = 8 $\Omega$ |      | 0.2        |      | %    |

| PSRR                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                |      | -          |      | dB   |

| Crosstalk            | Channel Separation, $R_L = 8\Omega$<br>F = 1 kHz<br>F = 20 Hz to 20 kHz                              |      | tba<br>tba |      | dB   |

| Τ <sub>WU</sub>      | Wake-Up Time (Cb = 1µF)                                                                              |      | 90         | 130  | ms   |

| T <sub>STDB</sub>    | Standby Time (Cb = 1µF)                                                                              |      | 10         |      | μs   |

| V <sub>STDBH</sub>   | Standby Voltage Level High                                                                           |      |            | 1.3  | V    |

| V <sub>STDBL</sub>   | V <sub>STDBL</sub> Standby Voltage Level Low                                                         |      |            | 0.4  | V    |

| $\Phi_{M}$           | $\stackrel{\text{Phase Margin at Unity Gain}}{R_{L} = 8\Omega, C_{L} = 500 \text{pF}}$ 65            |      | Degrees    |      |      |

| GM                   | Gain Margin<br>$R_L = 8\Omega, C_L = 500 pF$ 15                                                      |      | dB         |      |      |

| GBP                  | Gain Bandwidth Product<br>$R_L = 8\Omega$                                                            |      | 1.5        |      | MHz  |

1) Standby mode is activated when Vstdby is tied to Gnd.

All PSRR data limits are guaranteed by production sampling tests Dynamic measurements - 20\*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoidal signal superimposed upon Vcc.

| Table 5: V <sub>CC</sub> = +3.3V, GND = 0V, T <sub>amb</sub> = 25°C (unless otherwise specified) | ID = 0V, T <sub>amb</sub> = 25°C (unless otherwise specified) |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Symbol               | Parameter                                                                                                                        | Min.          | Тур.     | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------|----------|------|------|

| I <sub>CC</sub>      | Supply Current<br>No input signal, no load                                                                                       |               | 6.6      | 12   | mA   |

| I <sub>STANDBY</sub> | Standby Current <sup>1</sup><br>No input signal, Vstdby = $G_{ND}$ , RL = 8 $\Omega$                                             |               | 10       | 1000 | nA   |

| Voo                  | Output Offset Voltage<br>No input signal, $RL = 8\Omega$ 110                                                                     |               | mV       |      |      |

| Po                   | Output Power<br>THD = 1% Max, F = 1kHz, RL = $8\Omega$                                                                           | 375           | 5 500 mW |      | mW   |

| THD + N              | N Total Harmonic Distortion + Noise<br>Po = 400mWrms, Av = 2, 20Hz $\leq$ F $\leq$ 20kHz, RL = 8Ω 0.1                            |               |          | %    |      |

| PSRR                 | Power Supply Rejection Ratio <sup>2</sup><br>RL = $8\Omega$ , Av = 2, Vripple = 200mVpp, Input Grounded<br>F = 217Hz<br>F = 1kHz | 55<br>55      | 61<br>63 |      | dB   |

| Crosstalk            | Channel Separation, $R_L = 8\Omega$<br>F = 1kHz<br>F = 20Hz to 20kHz                                                             | tba dB<br>tba |          |      |      |

| Τ <sub>WU</sub>      | Wake-Up Time (Cb = 1µF)                                                                                                          |               | 110      | 140  | ms   |

| T <sub>STDB</sub>    | Standby Time (Cb = 1µF)                                                                                                          |               | 10       |      | μs   |

| V <sub>STDBH</sub>   | Standby Voltage Level High                                                                                                       |               |          | 1.2  | V    |

| V <sub>STDBL</sub>   | Standby Voltage Level Low                                                                                                        |               |          | 0.4  | V    |

| $\Phi_{M}$           | Phase Margin at Unity Gain<br>$R_L = 8\Omega, C_L = 500 pF$ 65                                                                   |               | Degrees  |      |      |

| GM                   | $\begin{array}{c c} Gain Margin \\ R_L = 8\Omega, C_L = 500 pF \end{array} \begin{array}{c} 15 \end{array}$                      |               | dB       |      |      |

| GBP                  | Gain Bandwidth Product<br>$R_L = 8\Omega$                                                                                        | 1.5 MHz       |          |      |      |

| GBP                  | Gain Bandwidth Product<br>$R_L = 8\Omega$                                                                                        |               | 1.5      |      | MHz  |

1) Standby mode is activated when Vstdby is tied to Gnd.

All PSRR data limits are guaranteed by production sampling tests Dynamic measurements - 20\*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoidal signal superimposed upon Vcc.

57

57

## TS4985

| Symbol               | Parameter                                                                                                                                                                                                                                                                                                            |  | Тур.       | Max.    | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------|---------|------|

| I <sub>cc</sub>      | Supply Current<br>No input signal, no load6.2                                                                                                                                                                                                                                                                        |  | 6.2        | 12      | mA   |

| I <sub>STANDBY</sub> | Standby Current <sup>1</sup><br>No input signal, Vstdby = $G_{ND}$ , RL = 8 $\Omega$                                                                                                                                                                                                                                 |  | 10         | 1000    | nA   |

| Voo                  | Output Offset Voltage<br>No input signal, $RL = 8\Omega$ 110                                                                                                                                                                                                                                                         |  | mV         |         |      |

| Po                   | Output Power<br>THD = 1% Max, F = 1kHz, RL = $8\Omega$ 220300                                                                                                                                                                                                                                                        |  |            | mW      |      |

| THD + N              | $\label{eq:relation} \begin{split} & N  \begin{array}{l} Total \ Harmonic \ Distortion \ + \ Noise \\ & Po = 200 mWrms, \ Av = 2, \ 20Hz \le F \le 20kHz, \ RL = 8\Omega \end{split} \qquad $ |  |            | %       |      |

| PSRR                 | $ \begin{array}{c c} \mbox{Power Supply Rejection Ratio}^2 \\ \mbox{RL} = 8\Omega, \mbox{Av} = 2, \mbox{Vripple} = 200 \mbox{mVpp, Input Grounded} \\ \mbox{F} = 217 \mbox{Hz} \\ \mbox{F} = 1 \mbox{Hz} \\ \mbox{F} = 1 \mbox{Hz} \\ \end{array} $                                                                  |  |            | dB      |      |

| Crosstalk            | Channel Separation, $R_L = 8\Omega$<br>F = 1kHz<br>F = 20Hz to 20kHz                                                                                                                                                                                                                                                 |  | tba<br>tba |         | dB   |

| T <sub>WU</sub>      | Wake-Up Time (Cb = $1\mu$ F)                                                                                                                                                                                                                                                                                         |  | 125        | 150     | ms   |

| T <sub>STDB</sub>    | Standby Time (Cb = 1µF)                                                                                                                                                                                                                                                                                              |  | 10         |         | μs   |

| V <sub>STDBH</sub>   | Standby Voltage Level High                                                                                                                                                                                                                                                                                           |  |            | 1.2     | V    |

| V <sub>STDBL</sub>   | Standby Voltage Level Low                                                                                                                                                                                                                                                                                            |  |            | 0.4     | V    |

| $\Phi_{M}$           | Phase Margin at Unity Gain<br>$R_L = 8\Omega$ , $C_L = 500 pF$<br>65                                                                                                                                                                                                                                                 |  |            | Degrees |      |

| GM                   | Gain Margin<br>$R_L = 8\Omega$ , $C_L = 500pF$                                                                                                                                                                                                                                                                       |  | 15         |         | dB   |

| GBP                  | Gain Bandwidth Product $R_L = 8\Omega$                                                                                                                                                                                                                                                                               |  | 1.5        |         | MHz  |

## Table 6: $V_{CC}$ = +2.6V, GND = 0V, $T_{amb}$ = 25°C (unless otherwise specified)

1) Standby mode is activated when Vstdby is tied to Gnd.

All PSRR data limits are guaranteed by production sampling tests Dynamic measurements - 20\*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoidal signal superimposed upon Vcc.

4.1 TS4985EIJT Pinout and Package Mechanical Data

#### 4.1.1 Pinout (top view)

4.1.2 Marking (top view)

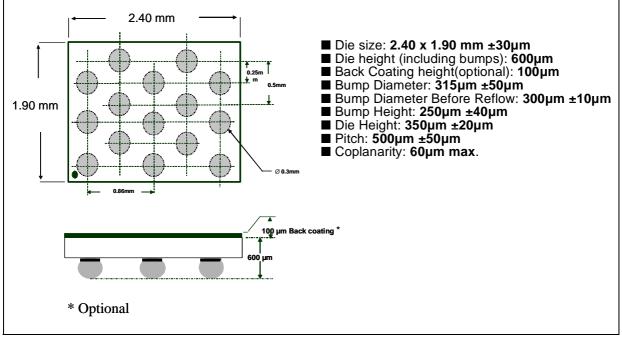

#### 4.1.3 Package mechanical data for 15-bump flip-chip

**\_\_\_**

57

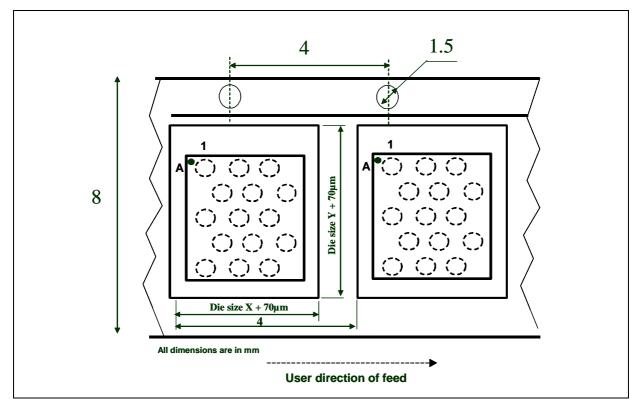

## 4.1.4 Tape & reel specification (top view)

#### 5 Revision History

| Date        | Revision | Description of Changes |

|-------------|----------|------------------------|

| 01 Nov 2004 | 1        | First Release          |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com

57