# RITOKO

#### **FEATURES**

- 35 mA (typ.) Output Current

- Operating Range 3.5 to 7 V

- Reference and Error Amplifier for Regulation

- External Shutdown

- External Oscillator Synch

#### **DESCRIPTION**

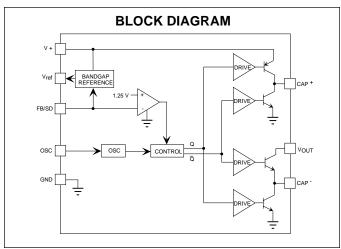

The TK75018 is a monolithic switched capacitor converter with feedback control. With just two capacitors, the TK75018 can create a negative voltage supply which tracks a positive supply. As an alternative, the feedback pin can be used to establish regulation at a desired voltage, and it can also be used as a shutdown signal input. A single TK75018 can also be configured as a non-inverting step-up converter or dual output voltage doubler.

With no external timing elements, the converter will self-oscillate at 25 kHz, nominal. This frequency can also be user adjusted with a small capacitor or synchronized to another oscillator.

Quiescent current is typically 2.5 mA. Standby current is guaranteed less than 200  $\mu$ A over the full operating temperature and input voltage ranges.

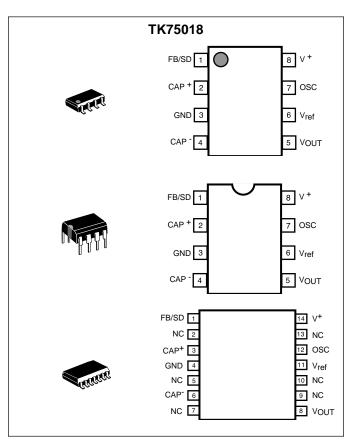

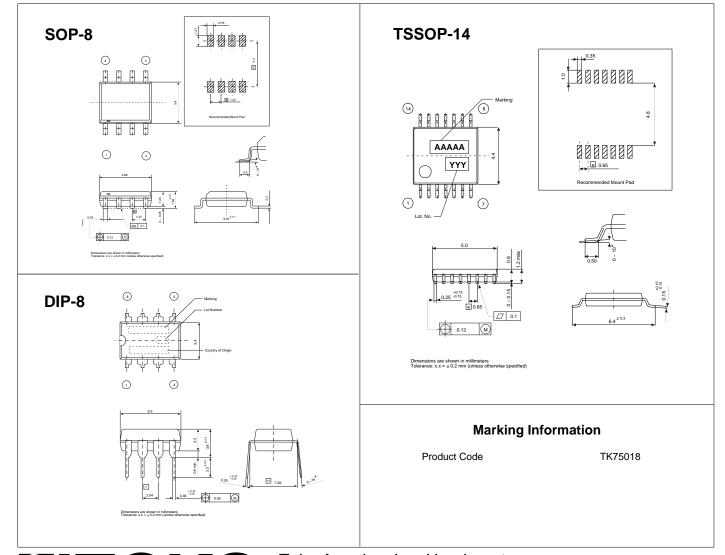

# PACKAGE CODE D: DIP-8 N: SOP-8 V: TSSOP-14

## SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR APPLICATIONS

- **■** Voltage Inverter

- Negative Voltage Doubler

- Voltage Regulator

- Positive Voltage Doubler

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage V <sub>IN</sub> For Doubler Conf 7 V    | Storage Temperature Range55 to +150 °C   |

|--------------------------------------------------------|------------------------------------------|

| Supply Voltage V <sub>IN</sub> For Regulating Conf 8 V | Operating Temperature Range20 to 80 °C   |

| Power Dissipation TK75018M (Note 1) 600 mW             | Junction Temperature 150 °C              |

| Power Dissipation TK75018D (Note 2) 1000 mW            | Lead Soldering Temperature (10 s) 235 °C |

| Power Dissipation TK75018V (Note 3) 950 mW             |                                          |

#### TK75018 ELECTRICAL CHARACTERISTICS

$Test \ conditions: \ V_{IN} = 5.0 \ V, \ T_A = T_j = Operating \ Temperature \ Range, \ Note \ 6 \ Configuration, \ unless \ otherwise \ specified.$

| SYMBOL                | PARAMETER                                          | TEST CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNITS |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>CC(Reg)</sub>  | Supply Current Regulating                          | I <sub>LOAD</sub> = 0 mA, (Note 6)                                                                      |      | 2.5  | 3.5  | mA    |

| I <sub>CC(Inv)</sub>  | Supply Current Inverting<br>Mode                   | I <sub>LOAD</sub> = 0 mA                                                                                |      | 3.5  | 4.5  | mA    |

| V <sub>cc</sub>       | Supply Voltage Range                               | Under Note 6 Conditions                                                                                 | 3.5  |      | 7    | V     |

| V <sub>LOSS</sub>     | Voltage Loss (V <sub>IN</sub> - V <sub>OUT</sub> ) | I <sub>OUT</sub> = 1 mA, (Note 4)                                                                       |      | 0.35 | 0.55 | V     |

|                       |                                                    | I <sub>OUT</sub> = 20 mA, (Note 4)                                                                      |      | 1    | 1.5  | V     |

| R <sub>OUT</sub>      | Output Resistance                                  | $\Delta I_{OUT} = 1$ mA to 20 mA, (Notes 4,5)                                                           |      | 32   | 54   | Ω     |

| f <sub>osc</sub>      | Oscillator Frequency                               | $3.5 \text{ V} \le \text{V}_{IN} \le 7 \text{ V}, \text{ (Note 6)}$                                     | 15   | 25   | 35   | kHz   |

| V <sub>ref</sub> R    | Reference Voltage                                  | $T_A = T_j = 25  ^{\circ}C$                                                                             | 2.35 | 2.50 | 2.65 | V     |

|                       |                                                    | $T_A = T_j = Operating Temp. Range$                                                                     | 2.25 |      | 2.75 | V     |

| V <sub>out</sub>      | Regulated Voltage                                  | $T_{j} = 25  ^{\circ}\text{C}, \ I_{L} = 1  \text{mA}, \ (\text{Note 6})$                               | -2.8 | -3.0 | -3.2 | V     |

| Line Reg              | Line Regulation                                    | $3.5 \text{ V} \le \text{V}_{\text{IN}} \le 7 \text{ V}, \text{ I}_{\text{L}} = 1 \text{ mA},$ (Note 6) |      | 15   | 80   | mV    |

| LoadReg₁              | Load Regulation @ 20 mA                            | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 20 mA, (Note 6)                                                     |      | 20   | 150  | mV    |

| LoadReg <sub>2</sub>  | Load Regulation @ 35 mA                            | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 35 mA, (Note 6)                                                     |      | 60   | 300  | mV    |

| I <sub>STBY</sub>     | Standby Current                                    | V <sub>PIN1</sub> = 0 V, (Note 6)                                                                       |      | 60   | 200  | μΑ    |

| $R_{\text{OUT(Ref)}}$ | Reference Output<br>Resistance                     | $V_{ref} \leq 80 \mu A$                                                                                 |      | 350  |      | Ω     |

Note 1: Power dissipation is 600 mW when mounted as recommended. Derate at 4.8 mW/°C for operation above 25 °C.

Note 2: Power dissipation is 1000 mW when mounted as recommended. Derate at 8 mW/°C for operation above 25 °C

Note 3: Power dissipation is 950 mW when mounted as recommended. Derate at 7.6 mW/ °C for operation above 25 °C.

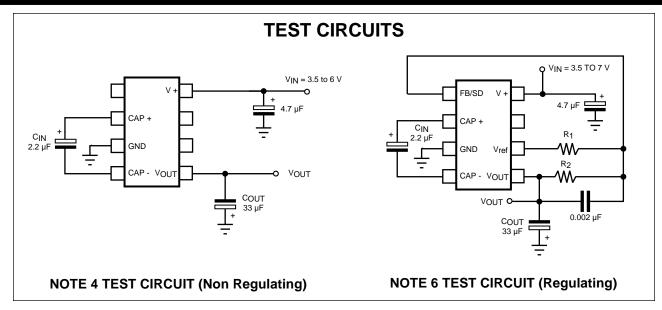

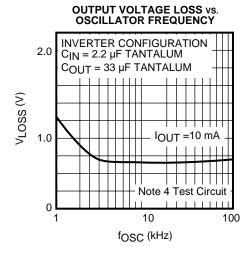

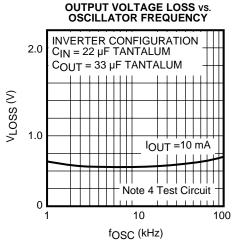

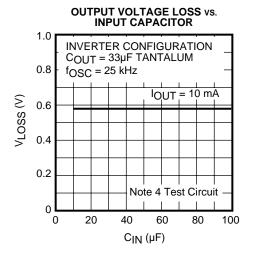

Note 4: Device is connected as an inverter, with pins 1, 6, and 7 unconnected;  $C_{IN} = 2.2 \,\mu\text{F}$  tantalum,  $C_{OUT} = 33 \,\mu\text{F}$  tantalum. Note 5: Output resistance means the slope of the  $\Delta V_{OUT}$  vs.  $\Delta I_{OUT}$  curve, for output currents of 1 to 20 mA. This represents a linear approximation

Note 6: Device is connected as a positive to negative converter/regulator with  $R_1 = 44.2$  k,  $R_2 = 154$  k,  $C_1 = 4.7$  nF,  $C_{VIN} = 4.7$   $\mu$ F tantalum,  $C_{\text{IN}}$  = 2.2  $\mu\text{F}$  tantalum,  $C_{\text{OUT}}$  = 33  $\mu\text{F}$  tantalum.

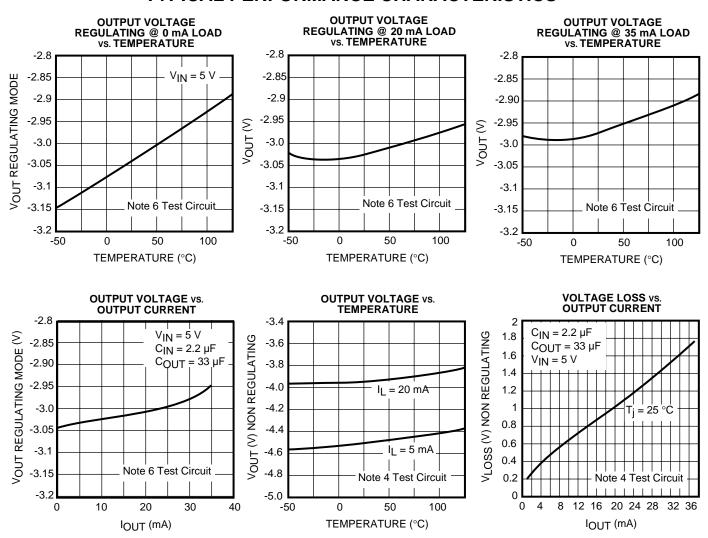

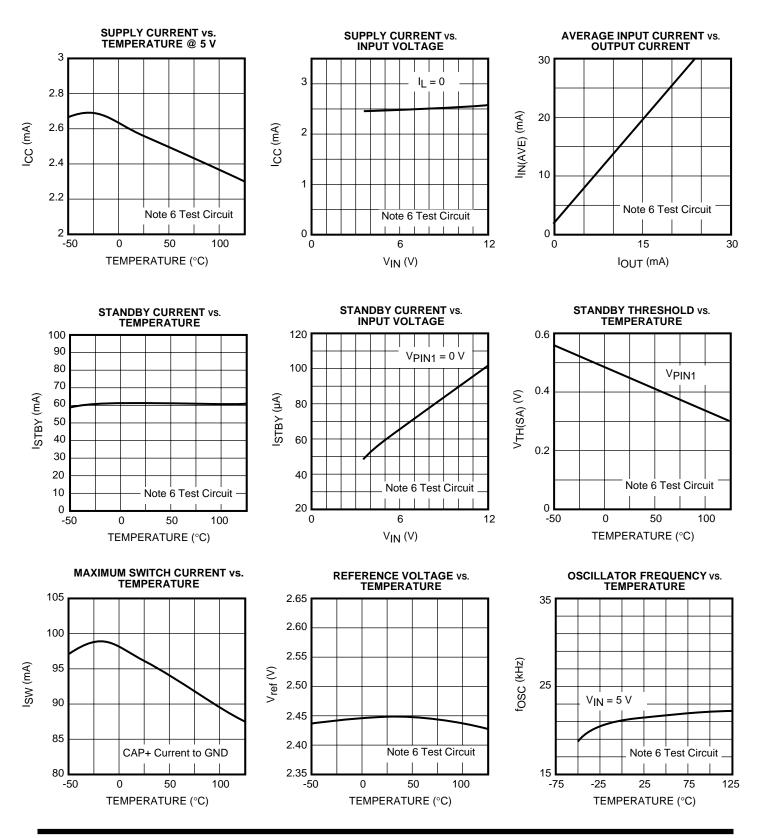

#### TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS (CONT.)**

Page 4 May 1999 TOKO, Inc.

## **TYPICAL PERFORMANCE CHARACTERISTICS (CONT.)**

#### THEORY OF OPERATION

As in any switched capacitor converter, the means of conveying energy from input to output is done by charging a capacitor between two potentials and then switching one end of the capacitor to a different potential. By some means of rectification, the other end of the capacitor is then forced to dump charge into another capacitor at the converter output, thereby conveying energy.

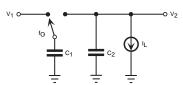

In a simple example shown in Figure 1, a capacitor  $C_1$  has one side tied to ground and another side charged by a voltage source of potential  $V_1$ . The non-grounded side of  $C_1$  is then switched over to be connected to one side of a capacitor  $C_2$ , which is at potential  $V_2$  and referenced to ground.  $V_2$  represents the output of the converter. The initial charge on  $C_1$  is:

$$q_1 = C_1 \times V_1$$

When the switch changes over to the  $V_2$  side,  $C_1$  is discharged from potential  $V_1$  to potential  $V_2$ . After discharge has occurred the charge on  $C_1$  is then:

$$q_2 = C_1 \times V_2$$

This means that the net transfer of charge which has occurred is:

$$\Delta q = q_1 - q_2 = C_1 (V_1 - V_2)$$

FIGURE 1: SWITCHED CAPACITOR CIRCUIT

If the potential  $V_2$  is sourcing a current  $I_L$ , the charge will have to be delivered at a rate:

$$f_O = I_L / \Delta q = I_L / C_1 (V_1 - V_2)$$

Thus, the higher the frequency, the more current that can be supported by the converter output.

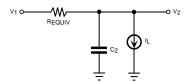

All else being ideal, the effective losses in the converter in the energy conveyance process is identical to that of a circuit consisting of a resistor between the potentials  $V_1$  and  $V_2$ , with the same load at the output side. This equivalent resistor is simply:

$$R_{EQUIV} = (V_1 - V_2) / I_L = 1 / (f_0 \times C_1)$$

# THEORY OF OPERATION (CONT.)

The illustration in Figure 2 represents an equivalent circuit to the basic example of a switched capacitor circuit in Figure 1.

FIGURE 2: SWITCHED CAPACITOR EQUIVALENT CIRCUIT

The efficiency of the ideal converter is given by the output power divided by the input power. Since the same current flows out of each potential, the efficiency,  $\eta$ , is equal to the ratio of  $V_2$  to  $V_1$ .

Using equalities established above we find:

$$\eta = V_2 / V_1 = \left\{ V_1 - \left[ I_L / \left( f_O \times C_1 \right) \right] \right\} / V_1 = 1 - \left[ I_L / \left( f_O \times C_1 \times V_1 \right) \right]$$

The last term in the equality string shows that efficiency can be improved by increasing frequency or the value of  $C_1$ . Limitations of the circuit and components tend to cause losses which increase with increasing frequency. Therefore, at some point in the frequency spectrum losses will be minimized. Hence, the oscillator of the TK75018 is designed to run in the frequency band where losses are minimized. Since the user will primarily be interested in maintaining a given output voltage, losses are characterized in terms of the voltage loss.

#### PIN DESCRIPTIONS

#### FEEDBACK AND SHUTDOWN (FB/SD)

By configuring an error voltage divider into the FB/SD pin, the TK75018 can be used to regulate the output voltage. It is recommended that the parallel combination of the divider resistors be greater than approximately 16 k $\Omega$  due to the limited current available from the reference. The Error Amplifier compares the FB/SD pin against an internal 1.25 V reference and limits the charge rate of C<sub>IN</sub>, thereby limiting its peak charged voltage over a given clock period and, thus, lowering the charge delivery rate to the output. The characteristic frequency response of the converter can be tailored by adjusting the ratio of C<sub>OUT</sub>:C<sub>IN</sub>, but it is recommended to keep it around 10:1. A "lead" capacitor from the negative output to the feedback input is required to maintain good light-load regulation; 2000 pF is recommended, regardless of output voltage. For standard configurations, the magnitude of the regulated voltage must be less than that which can be achieved without regulation,  $|V_{OUT}| - V_{LOSS}$ . Higher regulated output voltages can be achieved by configuring a voltage doubler, at the expense of maximum available output current.

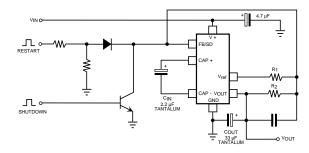

When the FB/SD pin is pulled below the shutdown threshold of ~0.45 V (e.g., via an open collector of an NPN transistor), the reference is shut off and the switching action is terminated. The drivers are set to allow both  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  to discharge into the output load. The quiescent supply current will drop to ~ 60  $\mu A$ . If an error voltage divider is not

being used, the TK75018 will automatically restart when the shutdown signal is removed. If such a divider is being used, the current through the divider may be sufficient to keep the device in shutdown until  $C_{\text{OUT}}$  is fully discharged, since the reference to the amplifier has collapsed during the shutdown. Although  $C_{\text{OUT}}$  is discharged fairly quickly (allowing a quick restart), this recycling delay may not be acceptable in some applications. This recycling delay can be bypassed by injecting a positive start-up pulse into the SD/FB pin (see Figure 3). This might be readily configured, for example, as a TTL level signal which is diode coupled into the divider. A resistor should be chosen to limit the voltage pulse injection magnitude to 0.7 to 1.1 V. A pulse width of  $\geq$  100  $\mu s$  is required to guarantee a successfully coupled start-up signal.

FIGURE 3: FEEDBACK AND SHUTDOWN

Page 6 May 1999 TOKO, Inc.

# **PIN DESCRIPTIONS (CONT.)**

#### INPUT CAPACITOR CHARGING PINS (CAP+/CAP-)

The positive driving pin of  $C_{IN}$  (CAP+) charges the positive node of the capacitor to  $V_{IN}$  during  $t_{CH}$  and pulls it down to ground during  $t_{DIS}$ . The negative driving pin of  $C_{IN}$  (CAP-) pulls the negative node of the capacitor to ground during  $t_{CH}$  and is driven into the output during  $t_{DIS}$ .

#### **CIRCUIT GROUND (GND)**

All potentials are referenced to this ground unless otherwise noted.

#### **OUTPUT VOLTAGE (V<sub>OUT</sub>)**

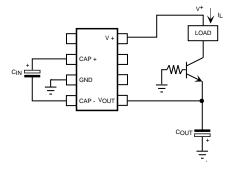

In most applications, a capacitor must be placed from this pin to ground to integrate the charge pulses delivered by  $C_{\rm IN}$ . A minimum of ten times  $C_{\rm IN}$  is recommended. Since the output voltage serves as the substrate inside the IC, the design must ensure that this pin is never raised to a higher potential than ground. This phenomenon will tend to occur when a positive-supply-to-negative-supply load is present at the converter output. A circuit, such as the one shown in Figure 4, is recommended. Under normal operation, the transistor will appear as a short circuit. But the sink current will be cut off from the output pin if the voltage starts to approach ground. The resistor is chosen to keep the transistor saturated under all steady-state operating conditions.

FIGURE 4: POSITIVE REFERENCED LOAD

The equation below can be used to calculate the values of the feedback resistors (R1 and R2) needed to achieve a desired output voltage.

$$R^{}_2 = R^{}_1 \left( \frac{|V^{}_{OUT}|}{1.2 \; V^{}} + 1 \right) \; \text{where} \; R^{}_1 \geq 24 \; k\Omega$$

#### REFERENCE VOLTAGE (V<sub>ref</sub>)

This pin provides a nominal 2.5 V buffered reference for external use. Normal output current should be kept below  $\sim 160 \, \mu A$ .

#### **OSCILLATOR PROGRAMMING (OSC)**

This pin can be used to alter the nominal 25 kHz frequency of the internal oscillator. An internal timing capacitor of ~150 pF is alternately charged during  $t_{\rm CH}$  and discharged during  $t_{\rm DIS}$  with a 7  $\mu$ A current source to fixed threshold levels. Adding an external capacitor from the OSC pin to ground will parallel the 150 pF capacitor to slow down the clock period. Adding a small external capacitor from the OSC pin to the CAP+ pin will source/sink extra charge into/out-of the internal timing capacitor to speed up the transition between thresholds and thereby raise the oscillator frequency. It is recommended that, in the latter configuration, the capacitor be kept below ~30 pF.

Synchronization of multiple TK75018s can be accomplished by adding pull-up resistors from the OSC pin to the reference voltage and using an open collector from an NPN transistor to provide the discharge. The NPN is then driven by a clocking pulse, and the same pulse can be used to drive multiple devices in the same configuration. It is not recommended to pull the OSC pin high with a low-impedance source. To synchronize and regulate with multiple devices, an external reference can be used as the reference point for the error voltage divider, thus allowing the internal reference to be used as the pull-up point for the OSC pin.

#### INPUT VOLTAGE (V+)

The input voltage is used to charge  $C_{\text{IN}}$  during the time  $t_{\text{CH}}$  during each clock period.  $C_{\text{IN}}$  is then discharged into the output capacitor during time  $t_{\text{DIS}}$ . During  $t_{\text{CH}}$ , the input current will be approximately 2.2 times the output current. During  $t_{\text{DIS}}$ , the input current will be approximately 0.2 times the output current. A low ESR bypass capacitor will average out the varying current seen by the input supply-yielding an average input current of approximately 1.1 times the output current. The bypass capacitor should be placed as near to the TK75018 as possible to disallow inductive spikes on the supply rail of the IC. A minimum of 2  $\mu$ F is recommended.

#### PACKAGE OUTLINE

Toko America, Inc. Headquarters 1250 Feehanville Drive, Mount Prospect, Illinois 60056 Tel: (847) 297-0070 Fax: (847) 699-7864

#### **TOKO AMERICA REGIONAL OFFICES**

Midwest Regional Office Toko America, Inc. 1250 Feehanville Drive Mount Prospect, IL 60056 Tel: (847) 297-0070 Fax: (847) 699-7864 Western Regional Office Toko America, Inc. 2480 North First Street , Suite 260 San Jose, CA 95131 Tel: (408) 432-8281

107 Mill Plain Road Danbury, CT 06811 Tel: (203) 748-6871 Fax: (203) 797-1223

Toko America, Inc.

Eastern Regional Office

Semiconductor Technical Support Toko Design Center 4755 Forge Road Colorado Springs, CO 80907 Tel: (719) 528-2200 Fax: (719) 528-2375

#### Visit our Internet site at http://www.tokoam.com

Fax: (408) 943-9790

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of its products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.