## VISION VV5402 Monolithic Sensor

Multi-standard Monochrome CMOS Image Sensor.

#### PRODUCT DATASHEET

#### DISTINCTIVE CHARACTERISTICS

- · Complete Video Camera on a single chip

- EIA/CCIR standard compatible

- Low power operation (250mW Typical)

- Integral 75Ω driver

- · Control options pin selectable for ease of use

- Low light operation to 0.5 lux

- Automatic Exposure and Gain Control

- · Automatic Black Level Calibration

- Linear or Gamma corrected output option

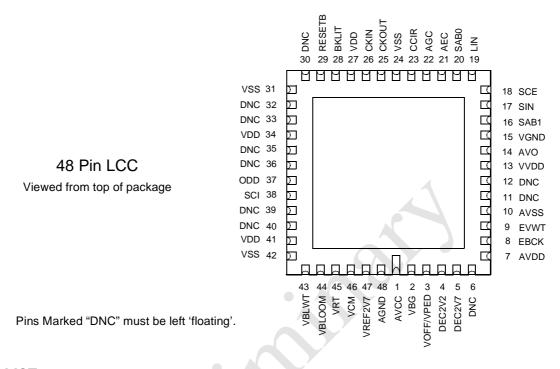

- Industry standard 48 pin LCC package

#### **GENERAL DESCRIPTION**

The VV5402 is a highly-integrated VLSI camera device based on VISION's unique CMOS sensor technology. It is suitable for applications requiring a composite video output with minimum external circuitry.

The device incorporates a 388 x 295 pixel image sensor and all the necessary support circuits to generate fully formatted composite video into a  $75\Omega$  load.

level allow use of a single fixed-aperture lens over a wide range of operating conditions. Normal and Backlit modes further enhance difficult scene types.

All major control functions are pin selectable giving maximum flexibility with ease of use. The VV5402 offers a complete camera system with only a few external components.

Automatic control of exposure, gain and black

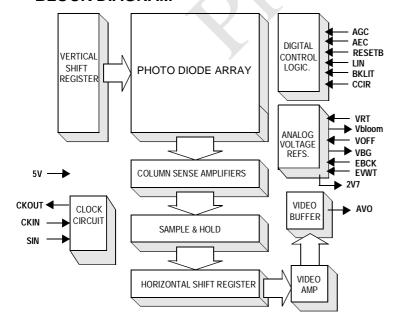

#### **BLOCK DIAGRAM**

| Pixel Format      | 384 x 287 (CCIR)<br>320 x 243 (EIA) |

|-------------------|-------------------------------------|

| Pixel Size        | 12μm x 12μm                         |

| Array Size        | 4.66mm x 3.54mm                     |

| Min. illumination | 0.5 lux (Standard Clock)            |

| S/N               | Typically 52dB                      |

| Exposure control  | Automatic (to 146000:1)             |

| Gain Control      | Automatic (to +20dB)                |

| Power Supply      | 5v ±5%                              |

| Power             | < 300 mW                            |

| Temperature       | 0°C - 40°C                          |

# Contents

|                         | page |

|-------------------------|------|

| Main Features           | 3    |

| Specifications          | 5    |

| Pin List                | 9    |

| √ideo Standards         | 12   |

| Example Support Circuit | 15   |

### **Video Output**

The VV5402 delivers a fully-formatted composite monochrome video signal. Standards options include EIA (320 x 244) and CCIR (384 x 287). On chip signal conditioning allows user-selection of linear or gamma-corrected output.

The integrated  $75\Omega$  driver eliminates the need for additional active components to drive standard loads, including double terminated lines.

### **Automatic Exposure and Gain Control**

Automatic exposure and gain control are enabled with AEC=1 (pin 21) and AGC=1 (pin22). However, If AEC is inhibited by pin 21, AGC is also inhibited. Inhibiting AEC or AGC by taking pin 21 or 22 low freezes the current value(s) for these.

#### **Automatic Exposure Control (AEC)**

The VV5402 controls exposure over a range of 99,000:1 in EIA mode and 146,000:1 in CCIR mode, and operates at illumination levels as low as 0.5 lux at standard clock frequencies. (The system clock frequency can be reduced to provide increased sensitivity.)

Automatic exposure control is achieved by varying pixel current integration time according to the average light level on the sensor. This integration time can vary from one pixel clock period to one frame period.

Pixels above a threshold white level are counted every frame, and the number at the end of the frame defines the image exposure. If the image is other than correctly exposed, a new value for integration time is calculated and applied for the next frame. Corrections are either  $\pm 1/8$  or  $\pm 1/64$ , depending upon the degree of over or under exposure.

### **Automatic Gain Control (AGC)**

The VV5402 automatically increases the system gain of its output stage if with the current gain setting and maximum exposure the image is too dark. Gain can be varied from x1 to x16 in times-two steps, giving five different gain settings.

If the scene is too dark and the integration period has almost reached its maximum value, the gain value is incremented by one step (times two). In the same frame period the exposure value is divided by two, halving the integration period. The exposure controller then increases the exposure value as necessary. Similarly if the image is too bright and the integration period is short then gain will be reduced by one step (divide by two) and the exposure value will be doubled. The exposure controller can then adjust the exposure value as necessary to provide a correctly exposed image.

#### **Backlit Mode**

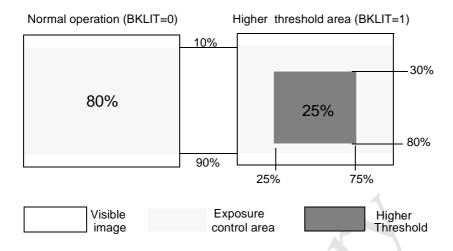

The VV5402 can be configured to operate in two auto-exposure modes, selected by the BKLIT pin (pin28) state. The default mode (BKLIT = 0) provides exposure control for normally illuminated scenes. For scenes where a bright background can cause the foreground subject to be severely under exposed, the 'Backlit' mode (BKLIT = 1) offers superior performance.

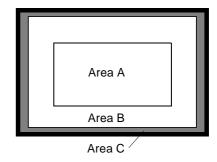

'Backlit Mode' (BKLIT=1) operates by using a higher threshold level for the exposure control comparator over the central area of an image, which is therefore exposed for longer and so enhanced. The area in which the higher comparator threshold is used when BKLIT=1 is illustrated below:

### **Backlit Mode Threshold Area:**

**Note**: The threshold level used for the central area is a preset mutiple of the normal mode reference level, and is not alterable.

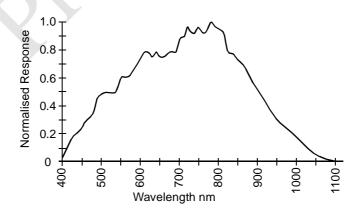

# **Spectral Response**

### **SPECIFICATIONS**

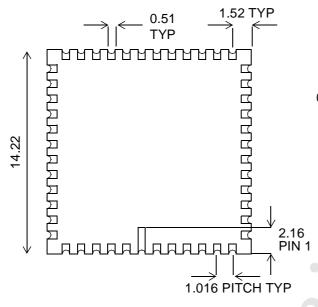

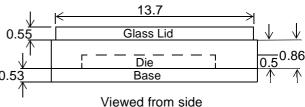

## **Package Details**

The optical array is centred within the package to a tolerance of  $\pm$  0.2 mm, and rotated no more than  $\pm$  0.5°

Tolerances on package dimensions ±10%

Glass lid placement is controlled so that no package overhang exists.

All dimensions in millimetres

Viewed from below

## **Absolute Maximum Ratings**

| Parameter                               | Value                                         |

|-----------------------------------------|-----------------------------------------------|

| Supply Voltage                          | -0.5 to +7.0 volts                            |

| Voltage on other input pins             | -0.5 to V <sub>DD</sub> + 0.5 volts           |

| Temperature under bias                  | -15°C to 85°C                                 |

| Storage Temperature                     | -30°C to 125°C                                |

| Maximum DC TTL output Current Magnitude | 10mA (per o/p, one at a time, 1sec. duration) |

Note: Stresses exceeding the Absolute Maximum Ratings may induce failure. Exposure to absolute maximum ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

09/04/97 5

# **DC Operating Conditions**

| Symbol          | Parameter                     | Min. | Тур. | Max.                 | Units | Notes     |

|-----------------|-------------------------------|------|------|----------------------|-------|-----------|

| V <sub>DD</sub> | Operating supply voltage      | 4.75 | 5.0  | 5.25                 | Volts |           |

| V <sub>IH</sub> | Input Voltage Logic "1"       | 2.4  |      | V <sub>DD</sub> +0.5 | Volts |           |

| V <sub>IL</sub> | Input Voltage Logic "0"       | -0.5 |      | 0.8                  | Volts |           |

| T <sub>A</sub>  | Ambient Operating Temperature | 0    |      | 70                   | οС    | Still air |

# **AC Operating Conditions**

| Symbol | Parameter              | Min. | Тур.    | Max. | Units | Notes |

|--------|------------------------|------|---------|------|-------|-------|

| CKIN   | EIA Crystal frequency  |      | 12.0000 |      | MHz   | 1     |

| CKIN   | CCIR Crystal frequency |      | 14.7456 |      | MHz   | 1     |

1. Pixel Clock =  $\frac{CKIN}{2}$

## **Electrical Characteristics**

| Symbol              | Parameter                  | Min. | Тур.  | Max. | Units | Notes                    |

|---------------------|----------------------------|------|-------|------|-------|--------------------------|

| I <sub>DCC</sub>    | Digital supply current     | ,    | 10    |      | mA    | 1                        |

| I <sub>ADD</sub>    | Analog supply current      |      | 25    |      | mA    | 1                        |

| I <sub>DD</sub>     | Overall supply current     |      | 35    |      | mA    | 1                        |

| V <sub>REF2V7</sub> | Internal voltage reference |      | 2.700 |      | Volts |                          |

| V <sub>BG</sub>     | Internal bandgap reference |      | 1.22  |      | Volts |                          |

| V <sub>OH</sub>     | Output Voltage Logic "1"   | 2.4  |       |      | Volts | I <sub>OH</sub> = 2mA    |

| V <sub>OL</sub>     | Output Voltage Logic "0"   |      |       | 0.6  | Volts | $I_{OL} = -2mA$          |

| I <sub>ILK</sub>    | Input Leakage current      | -1   |       |      | μΑ    | V <sub>IH</sub> on input |

|                     |                            |      |       | 1    | μΑ    | V <sub>IL</sub> on input |

Typical conditions,  $V_{DD}$  = 5.0 V,  $T_A$  = 27°C

1. Digital and Analogue outputs unloaded - add output current.

## **Operating Characteristics**

| Parameter           | min. | typ. | max. | units     | Note                                                                                                                                                                                     |

|---------------------|------|------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dark Current Signal |      | 50   |      | mV/Sec    | Modal pixel voltage due to photodiode leakage under zero illumination with Gain=1 (V <sub>dark</sub> = (V <sub>t1</sub> - V <sub>t2</sub> )/(t1-t2), averaged over two different frames) |

| Sensitivity         |      | 6    |      | V/Lux-Sec | V <sub>Ave</sub> /Lux⋅10ms, where Lux gives 50% saturation with Gain=1 and Exposure=10ms                                                                                                 |

| Min. Illumination   |      | 0.5  |      | Lux       | Standard CCIR clock                                                                                                                                                                      |

| Shading             |      | ТВА  |      | %         | Variance of V <sub>ave</sub> over eight equal blocks at 50% saturation level illumination                                                                                                |

| Random Noise        |      | -52  |      | dB        | RMS variance of all pixels, at 66% saturation, over four frames                                                                                                                          |

| Smear               |      | TBA  |      | %         | Ratio of V <sub>ave</sub> of the area outside a rectangle 25 lines high illuminated at 500xV <sub>50%</sub> level to V <sub>Ave</sub> of the rectangle                                   |

| Flicker             |      | ТВА  |      | %         | Variation of V <sub>ave</sub> of one line from field to field at 66% saturation level illumination                                                                                       |

| Lag                 |      | ТВА  | •    | %         | Average residual signal with no illumination in the field following one field of 66% sat. illumination                                                                                   |

| Blooming            |      | ТВА  |      |           | Ratio of spot illumination level that produces 0.1xV <sub>sat</sub> output from immediately around the spot to the V <sub>sat</sub> spot illumination level (pinhole target)             |

**Note:** Devices are normaly not 100% tested for the above characterisation parameters, other than Dark Current Signal (see Blemish Specification below).

All voltage ( $V_A$ ,  $V_{ave}$ ,  $V_{sat}$ ,  $V_{xx\%}$ ) measurements are referenced to the black level,  $V_{black}$ , and spot blemishes are excluded (see Blemish Specification below).  $V_{xx\%}$  refers to the output that is xx% of saturation, that is peak white.

### **Test Conditions**

The sensor is tested using the example support circuit illustrated later in this document. Standard imaging conditions used for optical tests employ a tungsten halogen lamp to uniformly illuminate the sensor (to better than 0.5%), or to illuminate specific areas. A neutral density filter is used to control the level of llumination where required.

| Illumination Colour Temp. | 3200° K   |

|---------------------------|-----------|

| Clock Frequency           | Std. CCIR |

| Exposure                  | Maximum   |

| Gain                      | x1        |

| Auto. Gain Control (AGC)  | Off       |

| Correction mode           | Linear    |

09/04/97 7

## **Blemish Specification**

A Blemish is an area of pixels that produces output significantly different from its surrounding pixels for the same illumination level. The definition of a Blemish Pixel varies according to testing conditions as follows:

| Test                | Exposure  | Illumination | Blemish Pixel output definition                                                                                                               |

|---------------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1 - Black Frame     | Minimum   | Black        | Differing more than ± 100mV. from modal value.                                                                                                |

| 2 - Dark Current    | Maximum   | Black        | Output more than three times the modal value (see Dark Current Signal above).                                                                 |

| 3 - Pixel Variation | Mid range | 66% Sat.     | Differing more than ±35mV from modal value.  Note: The mode of pixel values must be within ±70 mV of 66% of V <sub>sat</sub> for all devices. |

**Note:** Gain is set to Minimum and Correction set to Linear for all tests; measurement of blemishes for Test 3 is conducted under standard illumination (see above), set to produce average output of 66% saturation level.

The pixel area of the sensor is divided into the following areas to qualify the blemish specification:

Area A is the central area of the array as defined by the box with sides 50% of the linear height and 50% of the linear width of the array.

Area C is 10 vertical pixels by 10 horizontal pixels around the edge of the array.

Area B is the remaining area of the array.

The blemish specification is then defined as follows:

| Image Area | Max. No. of Blemishes | Notes                                                                                                                                        |

|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Area A     | 0                     | This is the most critical image area                                                                                                         |

| Area B     | 4                     | Unconnected single pixels                                                                                                                    |

| Alea D     | 1                     | Of up to four connected pixels (2x2 max.)                                                                                                    |

| Area C     | Any number            | Blemishes in this area are not significant, but the device shall, however, have no row or column (>50% of row or column) faults in any area. |

# **Pinout Diagram**

## **PIN LIST**

| Pin            | Name | Туре | Description                                    |  |  |  |

|----------------|------|------|------------------------------------------------|--|--|--|

| POWER SUPPLIES |      |      |                                                |  |  |  |

| 1              | AVCC | PWR  | Core analogue power and reference supplies.    |  |  |  |

| 7              | AVDD | PWR  | output stage power. AVDD3 output stage logic.  |  |  |  |

| 10             | AVSS | GND  | Output stage ground. AVSS3 output stage logic. |  |  |  |

| 13             | VVDD | PWR  | 75ohm buffer supply.                           |  |  |  |

| 15             | VGND | GND  | 75ohm buffer ground.                           |  |  |  |

| 24,31          | VSS  | GND  | Digital padring & logic ground.                |  |  |  |

| 27,34          | VDD  | PWR  | Digital padring & logic power.                 |  |  |  |

| 41             | DVDD | PWR  | Core digital power.                            |  |  |  |

| 42             | DVSS | GND  | Core digital ground.                           |  |  |  |

| 48             | AGND | GND  | Core analogue ground and reference supplies.   |  |  |  |

| Pin                         | Name          | Туре  | Description                                                                            |  |  |  |

|-----------------------------|---------------|-------|----------------------------------------------------------------------------------------|--|--|--|

| ANALOGUE VOLTAGE REFERENCES |               |       |                                                                                        |  |  |  |

| 2                           | VBG           | OA    | Internal bandgap reference voltage (1.22V nominal). Requires external 0.1uF capacitor. |  |  |  |

| 3                           | VOFF/<br>VPED | IA    | Pedestal DAC & Offset Comp. DAC bias. Connect to VBG or external reference.            |  |  |  |

| 4                           | DEC2V2        | OA    | Decouple 2.2V reference. Requires external 0.1uF capacitor.                            |  |  |  |

| 5                           | DEC2V7        | OA    | Decouple 2.7V reference. Requires external 0.1uF capacitor.                            |  |  |  |

| 8                           | EBCK          | IA    | External black level bias. Internally generated. Decouple to VGND                      |  |  |  |

| 9                           | EVWT          | IA    | External white pixel threshold for exposure control. Decouple to VGND                  |  |  |  |

| 43                          | VBLWT         | IA    | Defines white level for clamp circuitry. Requires external 0.1uF capacitor.            |  |  |  |

| 44                          | VBLOOM        | OA    | Anti-blooming voltage reference. Requires external 0.1uF capacitor.                    |  |  |  |

| 45                          | VRT           | IA    | Pixel reset voltage. Connect to VREF2V7 or external reference.                         |  |  |  |

| 46                          | VCM           | IA    | Offset DAC common mode input. Connect to VREF2V7.                                      |  |  |  |

| 47                          | VREF2V7       | OA    | Internally generated 2.7V reference. Requires external 4.7uF capacitor.                |  |  |  |

| ANALO                       | GUE OUTPL     | JTS   |                                                                                        |  |  |  |

| 14                          | AVO           | ОА    | Buffered Analogue video out. Can drive a doubly terminated 75ohm load.                 |  |  |  |

| SYSTE                       | M CLOCKS      |       |                                                                                        |  |  |  |

| 25                          | СКОИТ         | OD    | Oscillator output. Connect Crystal for standard timing.                                |  |  |  |

| 26                          | CKIN          | ID    | Oscillator input. Connect Crystal for standard timing.                                 |  |  |  |

| IMAGE                       | TIMING SIG    | SNALS |                                                                                        |  |  |  |

| 37                          | ODD           | OD    | Odd/even field signal. (ODD = 1 for odd fields, ODD = 0 for even)                      |  |  |  |

| Pin                                      | Name                    | Туре | Description                                                                                                                                    |  |  |

|------------------------------------------|-------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIGITA                                   | DIGITAL CONTROL SIGNALS |      |                                                                                                                                                |  |  |

| 16                                       | SAB1                    | ID↓  | Chip Address, Bit 1                                                                                                                            |  |  |

| 17                                       | SIN                     | ID↓  | Used to reset video timing control logic without resetting any other part of VV5402. Resets video logic on the falling edge of the SIN pulse.  |  |  |

| 18                                       | SCE                     | ID↓  | Scan Mode Enable - only relevant to test mode.                                                                                                 |  |  |

| 19                                       | LIN                     | ID↓  | Gamma corrected or Linear output. LIN = 0, gamma corrected output, LIN = 1, linear output. Default is gamma.                                   |  |  |

| 20                                       | SAB0                    | ID↓  | Chip Address, Bit 0                                                                                                                            |  |  |

| 21                                       | AEC                     | ID↑  | Automatic exposure control. AEC = 1, auto exposure is enabled; AEC = 0 auto exposure and auto gain control are disabled.                       |  |  |

| 22                                       | AGC                     | ID↑  | Automatic gain control enable. AGC = 1, auto-gain is enabled (if AEC = 1); AGC = 0, auto-gain is disabled.                                     |  |  |

| 23                                       | CCIR                    | ID↑  | Select default video mode for power-on. CCIR = 1 for CCIR video. EIA video mode is selected when CCIR = 0. Default is CCIR if unconnected      |  |  |

| 28                                       | BKLIT                   | ID↓  | Normal or Backlit exposure control mode. BKLIT = 0, normal mode; BKLIT = 1, backlit mode. Default is normal. See Exposure Control for details. |  |  |

| 29                                       | RESETB                  | ID↑  | Active low camera reset. All camera systems are reset to power-on state.                                                                       |  |  |

| 38                                       | SCI                     | ID↓  | Scan Chain Input - only relevant to test mode.                                                                                                 |  |  |

| OTHER PINS                               |                         |      |                                                                                                                                                |  |  |

| 6, 11, 12, 30, 32,<br>33, 35, 36, 39, 40 |                         | DNC  | DO NOT CONNECT. These pins must be left 'floating' for correct operation.                                                                      |  |  |

### Key:

IA - Analogue input ID - Digital input ID↑ - Digital input with OA -OD -OD↓ -Analogue output Digital output

ID↑ - Digital input with internal pull-up DNC- Do Not Connect Digital output with internal pull-down

Bidirectional BI -

### **VIDEO STANDARDS**

The VV5402 has 2 different video format modes, producing CCIR or EIA standard composite Monochrome video output. Line standards and frequencies are as follows:

| Video Mode | Format | Image (Pixels) | Crystal Frequency | CCIR pin |

|------------|--------|----------------|-------------------|----------|

| CCIR       | 4:3    | 384 x 287      | 14.7456 MHz       | 1        |

| EIA        | 4:3    | 320 x 243      | 12.0000 MHz       | 0        |

**VV5402 Video Modes**

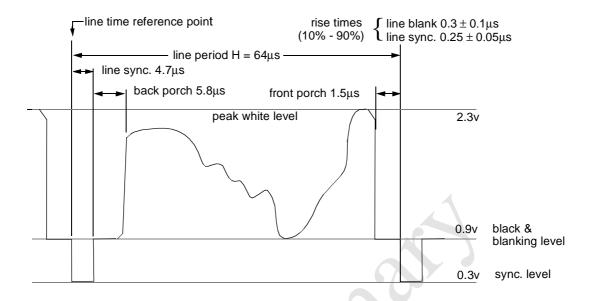

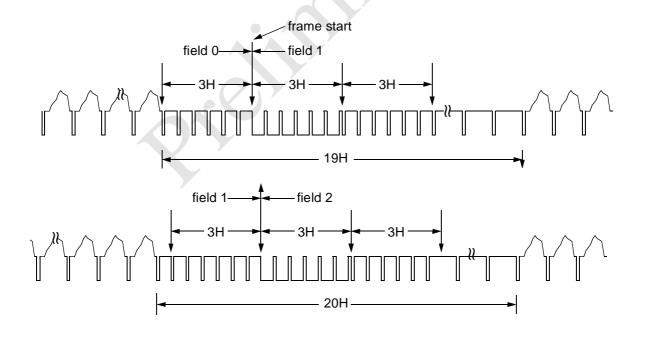

## **Video signal Characteristics**

The following table summarises the composite video output levels (AVO) for the two standards, which are graphically illustrated on the following pages:

| Symbol             | Parameter                | Min. | Тур. | Max. | Units | Notes                     |

|--------------------|--------------------------|------|------|------|-------|---------------------------|

| V <sub>Sync</sub>  | CCIR, EIA Sync. level    |      | 0.3  |      | V     |                           |

| V <sub>blank</sub> | CCIR, EIA Blanking level |      | 0.9  |      | V     | DC reference<br>level     |

| V <sub>black</sub> | CCIR Black level         |      | 0.9  |      | V     |                           |

|                    | EIA Black level          |      | 1.0  |      | V     |                           |

| V <sub>Sat</sub>   | CCIR Saturation level    |      | 2.3  |      | V     | Peak White;               |

|                    | EIA Saturation level     |      | 2.4  |      | V     | AVO clipped at this level |

Note: All measurements are made with AVO driving one 75 $\Omega$  load.

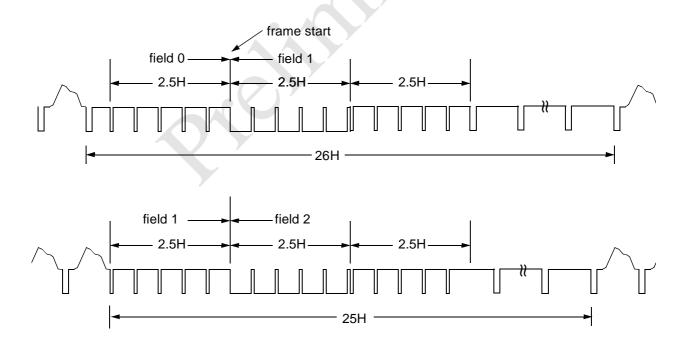

# **CCIR Timing Diagram**

### CCIR composite video signal - line level timing

CCIR composite video signal - field level timing

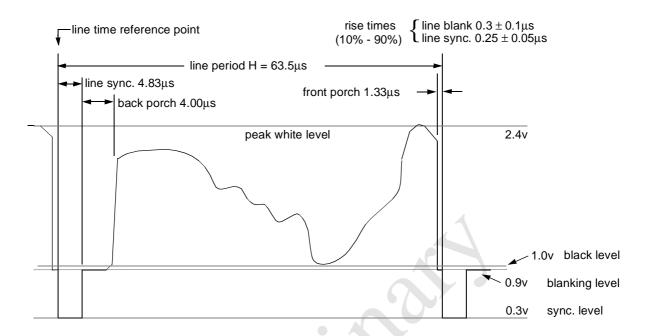

# **EIA Timing Diagrams**

EIA composite video signal - line level timing

EIA composite video signal - field level timing

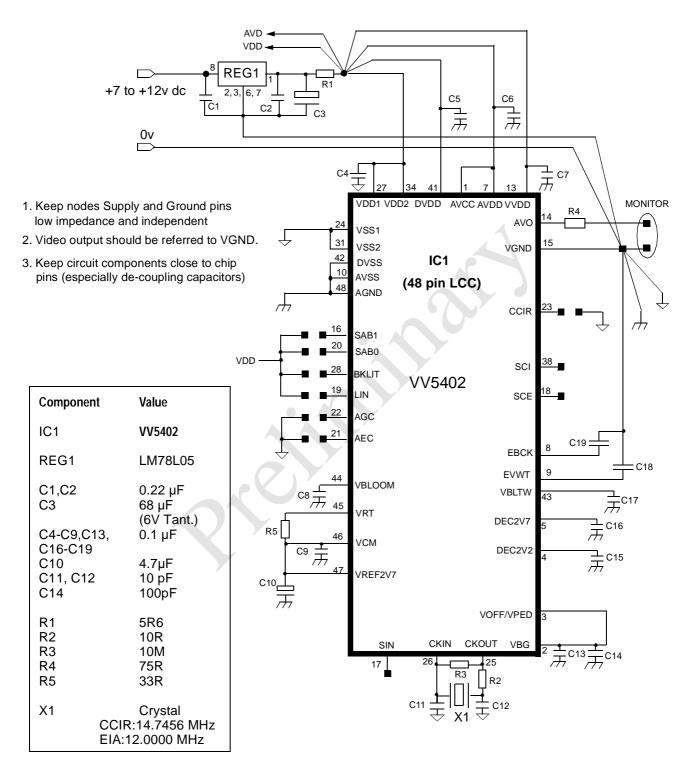

### **EXAMPLE SUPPORT CIRCUIT**

Use Surface Mount components throughout.

## **VLSI VISION LIMITED**

UK Office Aviation House, 31 Plnkhill, Edinburgh, UK EH12 7BF

Tel: +44 (0)131 539 7111 Fax: +44 (0)131 539 7140

Email: info@vvl.co.uk

**USA West Office** 18805 Cox Avenue,

Suite 260, Saratoga,

California 95070, USA Tel: +1 408 374 5323 Fax: +1 408 374 4722

Email: info@vvl.co.uk

**USA East Office**

2517 Highway 35 Bldg F, Suite 202 Manasquan

New Jersey 08736 Tel: +1 908 528 2222 Fax: +1 908 528 9305

Email: info@vvl.co.uk

VLSI Vision Ltd. reserves the right to make changes to its products and specifications at any time. Information furnished by VISION is believed to be accurate, but no responsibility is assumed by VISION for the use of said information, nor any infringements of patents or of any other third party rights which may result from said use. No license is granted by implication or otherwise under any patent or patent rights of any VISION group company.

© Copyright 1996, VLSI VISION

| VLSI Vision agent or distributor |  |

|----------------------------------|--|

|                                  |  |

|                                  |  |

|                                  |  |

| /                                |  |