# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90560 Series HARDWARE MANUAL

## **PREFACE**

## **■** Objectives and Intended Reader

Thank you for purchasing Fujitsu semiconductor products.

The MB90560 series was developed as a group of general-purpose models in the F<sup>2</sup>MC-16 LX series, which is a family of original 16-bit single-chip microcontrollers that can be used for application specific ICs (ASICs).

This manual is intended for engineers who design products using the MB90560 series of microcontrollers. The manual describes the functions and operation of the MB90560 series.

## **■** Trademarks

F<sup>2</sup>MC is a registered trademark of Fujitsu Limited and stands for FUJITSU Flexible Microcontroller.

- 1. The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- 2. The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

- 3. The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

- 4. FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

#### **CAUTION:**

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

- 5. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- 6. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

© 1998 FUJITSU LIMITED Printed in Japan

# **CONTENTS**

| CHAPT | TER 1 OVERVIEW                                            | 1  |

|-------|-----------------------------------------------------------|----|

| 1.1   | Features                                                  | 2  |

| 1.2   | Product Lineup                                            | 4  |

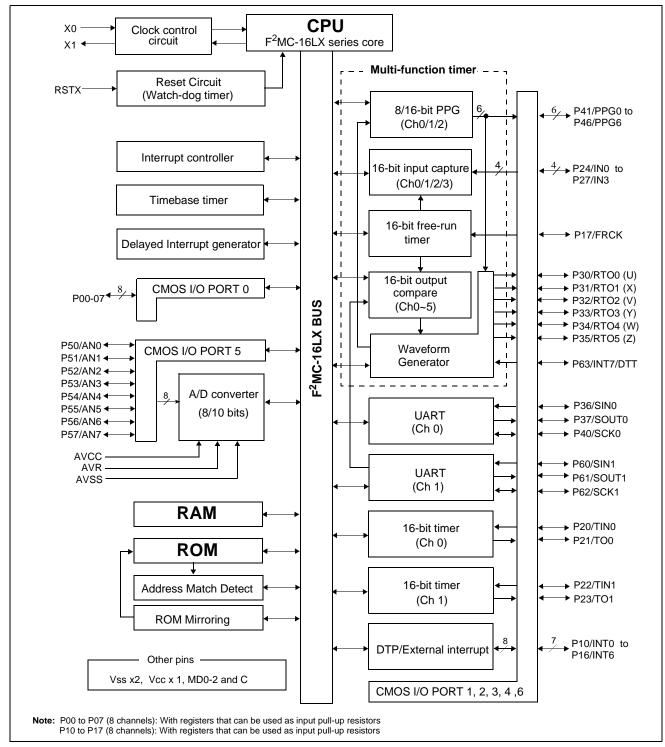

| 1.3   | Block Diagram                                             | 5  |

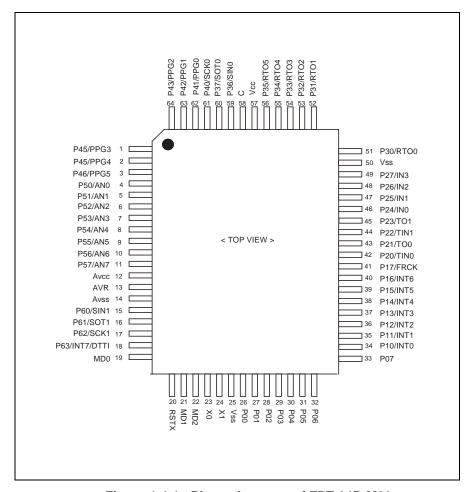

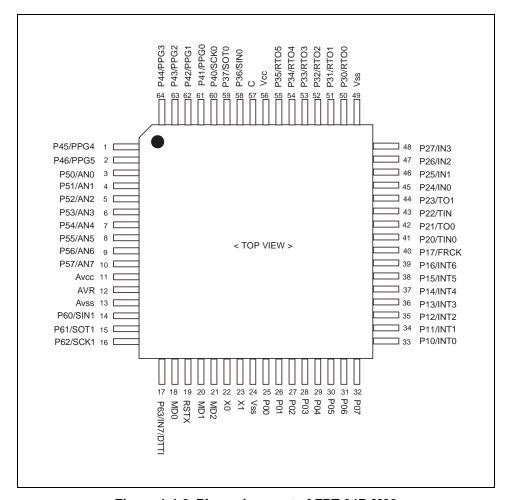

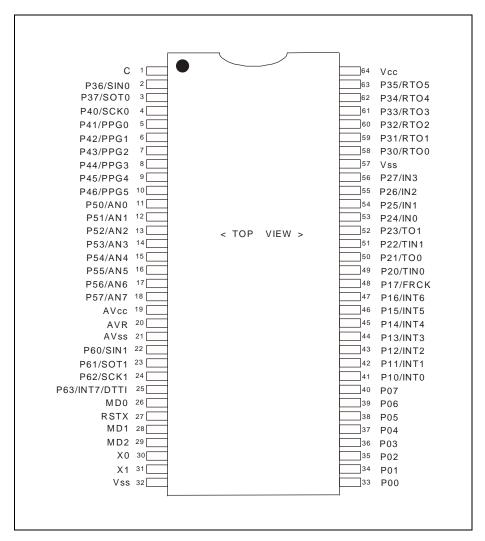

| 1.4   | Pin Assignments                                           | 6  |

| 1.5   | Package Dimensions                                        | 10 |

| 1.6   | Pin Functions                                             | 14 |

| 1.7   | I/O Circuit Types                                         | 18 |

| 1.8   | Notes on Handling Devices                                 | 20 |

| CHAPT | TER 2 CPU                                                 | 23 |

| 2.1   | CPU                                                       | 24 |

| 2.2   | Memory Space                                              | 26 |

| 2.3   | Memory Maps                                               | 28 |

| 2.4   | Addressing                                                | 29 |

| 2.4.1 | 3                                                         |    |

| 2.4.2 |                                                           |    |

| 2.5   | Memory Location of Multibyte Data                         |    |

| 2.6   | Registers                                                 |    |

| 2.7   | Dedicated Registers                                       |    |

| 2.7.1 |                                                           |    |

| 2.7.2 |                                                           |    |

| 2.7.3 | ,                                                         |    |

| 2.7.4 | 9 ( ,                                                     |    |

| 2.7.5 |                                                           |    |

| 2.7.6 | ,                                                         |    |

| 2.7.7 | 9                                                         |    |

| 2.7.8 |                                                           |    |

| 2.7.9 |                                                           |    |

| 2.8   | General-Purpose Registers                                 |    |

| 2.9   | Prefix Codes                                              |    |

|       | Bank select prefix (PCB, DTB, ADB, SPB)                   |    |

| 2.9.2 |                                                           |    |

| 2.9.3 |                                                           |    |

| 2.9.4 | Restrictions on Prefix Codes                              | 64 |

| CHAPT |                                                           |    |

| 3.1   | Resets                                                    |    |

| 3.2   | Reset Causes and Oscillation Stabilization Wait Intervals |    |

| 3.3   | External Reset Pin                                        |    |

| 3.4   | Reset Operation                                           |    |

| 3.5   | Reset Cause Bits                                          |    |

| 3.6   | Status of Pins in a Reset                                 | 78 |

| CHAP        | PTER 4 CLOCKS                                                                              | 81                                |

|-------------|--------------------------------------------------------------------------------------------|-----------------------------------|

| 4.1         | Clocks                                                                                     | 82                                |

| 4.2         | Block Diagram of the Clock Generator                                                       | 84                                |

| 4.3         | Clock Selection Register (CKSCR)                                                           | 86                                |

| 4.4         | Clock Mode                                                                                 | 88                                |

| 4.5         | Oscillation Stabilization Wait Interval                                                    | 90                                |

| 4.6         | Connection of an Oscillator or an External Clock                                           | 91                                |

| СНАР        | TER 5 LOW POWER CONSUMPTION MODE                                                           | 93                                |

| 5.1         | Low Power Consumption Mode                                                                 | 94                                |

| 5.2         | Block Diagram of the Low Power Consumption Control Circuit                                 | 96                                |

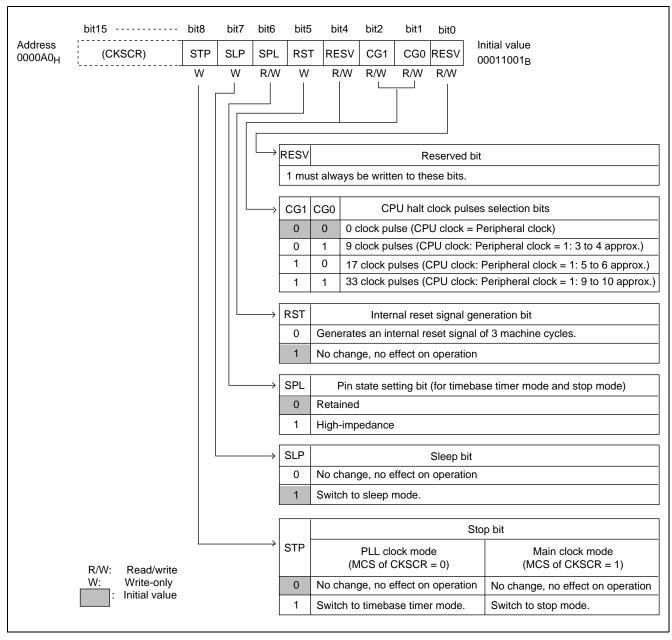

| 5.3         | Low Power Mode Control Register (LPMCR)                                                    | 98                                |

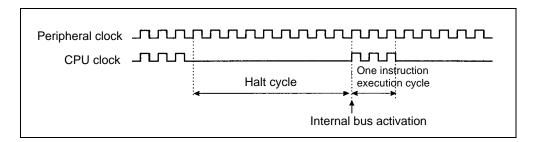

| 5.4         | CPU Intermittent Operation Mode                                                            | 102                               |

| 5.5         | Standby Mode                                                                               | 103                               |

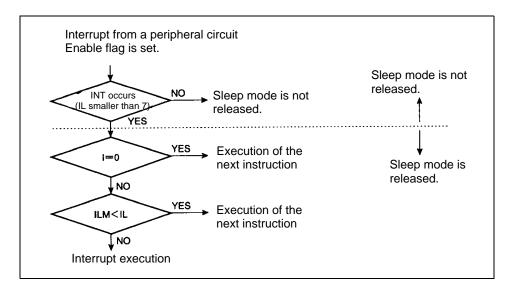

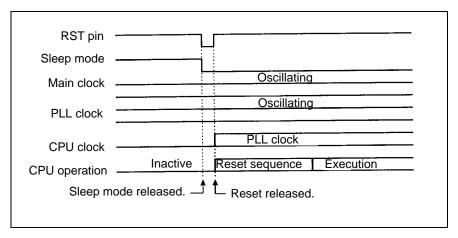

| 5.5.        | .1 Sleep mode                                                                              | 104                               |

| 5.5.        |                                                                                            |                                   |

| 5.5.        | •                                                                                          |                                   |

| 5.6         | Status Change Diagram                                                                      |                                   |

| 5.7         | Status of Pins in Standby Mode and Reset                                                   |                                   |

| 5.8         | Notes on Using Low Power Consumption Mode                                                  | 116                               |

| CHAP        | TER 6 INTERRUPTS                                                                           | 119                               |

| 6.1         | Interrupts                                                                                 |                                   |

| 6.2         | Interrupt Causes and Interrupt Vectors                                                     | 122                               |

| 6.3         | Interrupt Control Registers and Peripheral Functions                                       |                                   |

| 6.3.        | ,                                                                                          |                                   |

| 6.3         | , ,                                                                                        |                                   |

| 6.4         | Hardware Interrupts                                                                        |                                   |

| 6.4.        | ,                                                                                          |                                   |

| 6.4.        |                                                                                            |                                   |

| 6.4.        |                                                                                            |                                   |

| 6.4.        |                                                                                            |                                   |

| 6.4.        |                                                                                            |                                   |

| 6.5         | Software Interrupts                                                                        |                                   |

| 6.6         | Interrupt of Extended Intelligent I/O Service (El <sup>2</sup> OS)                         |                                   |

| 6.6         |                                                                                            |                                   |

| 6.6.<br>6.7 | .2 Registers of the extended intelligent I/O service (EI <sup>2</sup> OS) descriptor (ISD) |                                   |

| 6.7<br>6.7. | ·                                                                                          |                                   |

| 6.7.        |                                                                                            |                                   |

| 6.8         | Exception Processing Interrupt                                                             |                                   |

| 6.9         | Stack Operations for Interrupt Processing                                                  |                                   |

| 6.10        | Sample Programs for Interrupt Processing                                                   |                                   |

| CHVD        | PTER 7 SETTING A MODE                                                                      | 167                               |

|             |                                                                                            |                                   |

| 7.1<br>7.2  | Setting a Mode  Mode Pins (MD2 to MD0)                                                     |                                   |

| 1.4         | IVIOUE FIND (IVIDA 10 IVIDA)                                                               | ווווווווווווווווווווווווווווווווו |

| 7.3   | Mode Data                                     | 170 |

|-------|-----------------------------------------------|-----|

| CHAP1 | TER 8 I/O PORTS                               | 173 |

| 8.1   | Overview of I/O Ports                         | 174 |

| 8.2   | Port Register                                 | 175 |

| 8.3   | Port 0                                        | 176 |

| 8.3.1 | Port 0 Registers (PDR0, DDR0, and RDR0)       | 178 |

| 8.3.2 | Operation of Port 0                           | 180 |

| 8.4   | Port 1                                        | 182 |

| 8.4.1 | Port 1 Registers (PDR1, DDR1, and RDR1)       | 184 |

| 8.4.2 | Operation of Port 1                           | 186 |

| 8.5   | Port 2                                        |     |

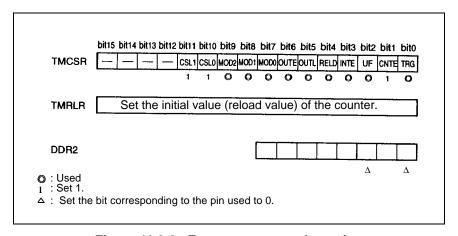

| 8.5.1 | Port 2 Registers (PDR2 and DDR2)              | 190 |

| 8.5.2 | '                                             |     |

| 8.6   | Port 3                                        |     |

| 8.6.1 | 9 (                                           |     |

| 8.6.2 | •                                             |     |

| 8.7   | Port 4                                        |     |

| 8.7.1 |                                               |     |

| 8.7.2 | '                                             |     |

| 8.8   | Port 5                                        |     |

| 8.8.1 | 9 ( , , , , , , , , , , , , , , , , , ,       |     |

| 8.8.2 |                                               |     |

| 8.9   | Port 6                                        |     |

| 8.9.1 | ,                                             |     |

| 8.9.2 | '                                             |     |

| 8.10  | Sample I/O Port Program                       | 218 |

| СНАРТ | TER 9 TIMEBASE TIMER                          | 221 |

| 9.1   | Overview of the Timebase Timer                | 222 |

| 9.2   | Configuration of the Timebase Timer           | 224 |

| 9.3   | Timebase Timer Control Register (TBTC)        | 226 |

| 9.4   | Timebase Timer Interrupts                     | 228 |

| 9.5   | Operation of the Timebase Timer               | 230 |

| 9.6   | Usage Notes on the Timebase Timer             | 232 |

| 9.7   | Sample Program for the Timebase Timer Program | 234 |

| CHAPT | TER 10 WATCHDOG TIMER                         | 237 |

| 10.1  | Overview of the Watchdog Timer                | 238 |

| 10.2  | Configuration of the Watchdog Timer           |     |

| 10.3  | Watchdog Timer Control Register (WDTC)        |     |

| 10.4  | Operation of the Watchdog Timer               |     |

| 10.5  | Usage Notes on the Watchdog Timer             |     |

| 10.6  | Sample Program for the Watchdog Timer         |     |

| CHAPI | TER 11 16-BIT RELOAD TIMER                    | 247 |

| 11.1  | Overview of the 16-Bit Reload Timer           | 248 |

|       |                                               |     |

| 11.2 | Configuration of the 16-Bit Reload Timer                          | 252 |

|------|-------------------------------------------------------------------|-----|

| 11.3 | 16-Bit Reload Timer Pins                                          | 254 |

| 11.4 | 16-Bit Reload Timer Registers                                     | 255 |

| 11.  | 4.1 Timer control status register, upper part (TMCSR0, TMCSR1: H) | 256 |

| 11.  | 4.2 Timer control status register, lower part (TMCSR0, TMCSR1: L) | 258 |

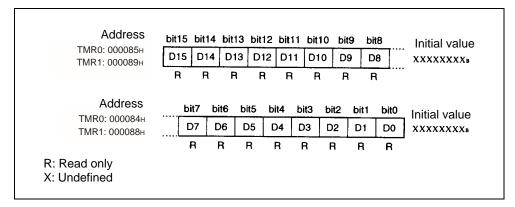

| 11.  | 4.3 16-bit timer register (TMR0, TMR1)                            | 260 |

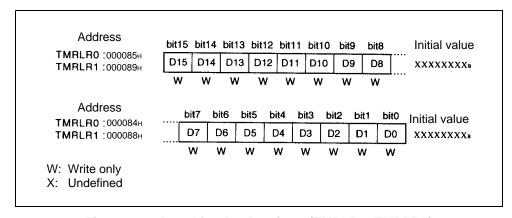

| 11.  | 4.4 16-bit reload register (TMRLR0, TMRLR1)                       | 261 |

| 11.5 | 16-Bit Reload Timer Interrupts                                    | 262 |

| 11.6 | Operation of the 16-Bit Reload Timer                              | 264 |

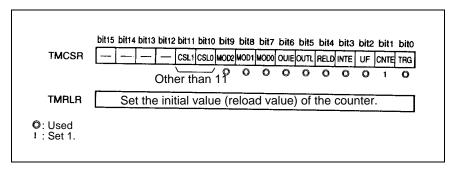

| 11.  | 6.1 Reload Mode (Internal Clock Mode)                             | 266 |

| 11.  | 6.2 Single-shot Mode (Internal Clock Mode)                        | 268 |

| 11.  | 6.3 Event count mode                                              | 270 |

| 11.7 | Usage Notes on the 16-Bit Reload Timer                            | 272 |

| 11.8 | Sample Programs for the 16-Bit Reload Timer                       | 273 |

| СНАЕ | PTER 12 MULTI-FUNCTION TIMER                                      | 277 |

| 12.1 | Overview of Multi-function Timer                                  |     |

| 12.2 | Block Diagram of Multi-function Timer                             |     |

| 12.3 | Register of Multi-Function Timer                                  |     |

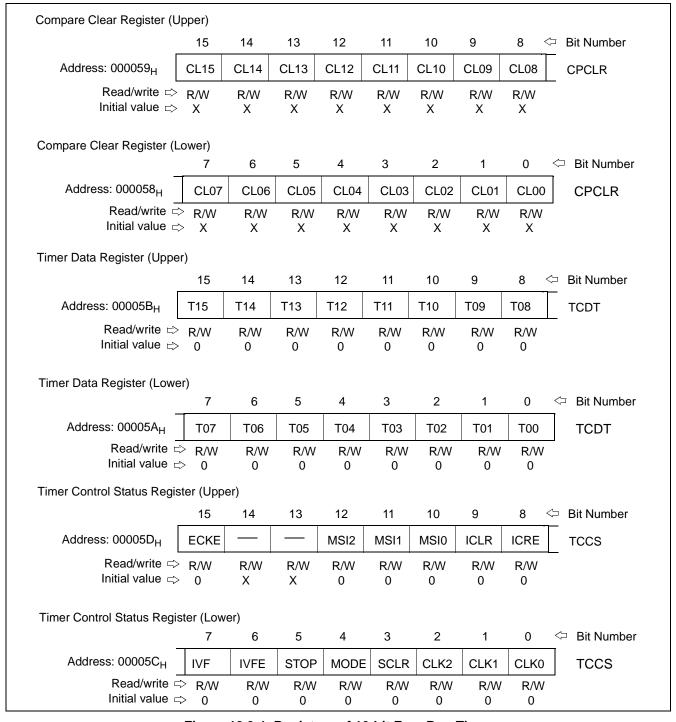

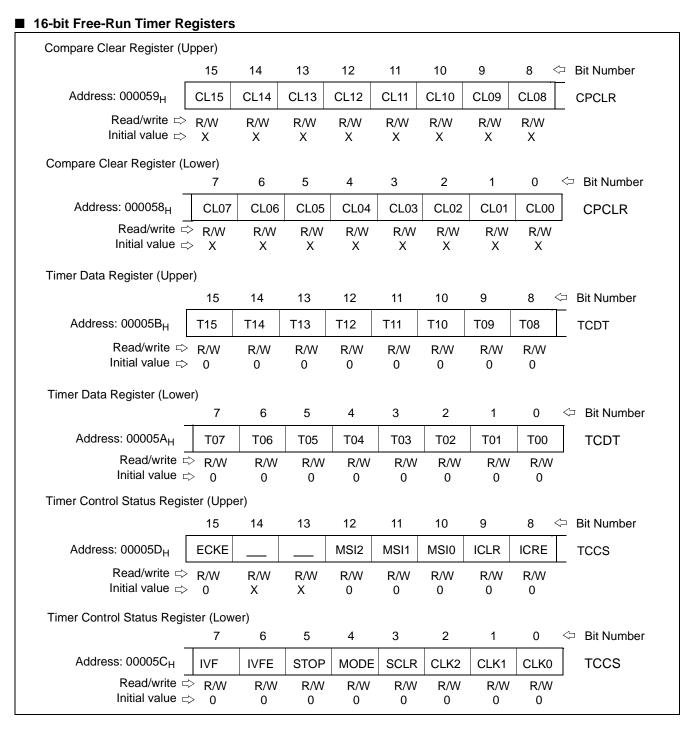

|      | 3.1 Registers of 16-bit Free-Run Timer                            |     |

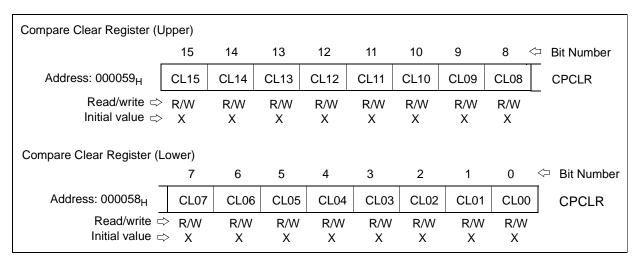

|      | 12.3.1.1 Compare Clear Register (CPCLR)                           |     |

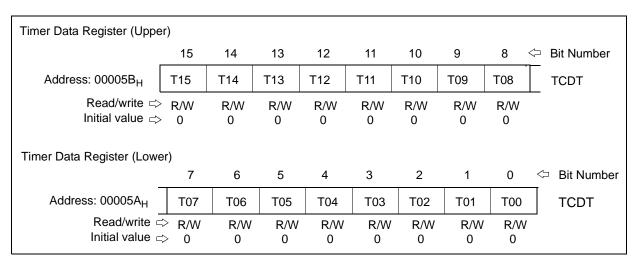

|      | 12.3.1.2 Timer Data Register (TCDT)                               |     |

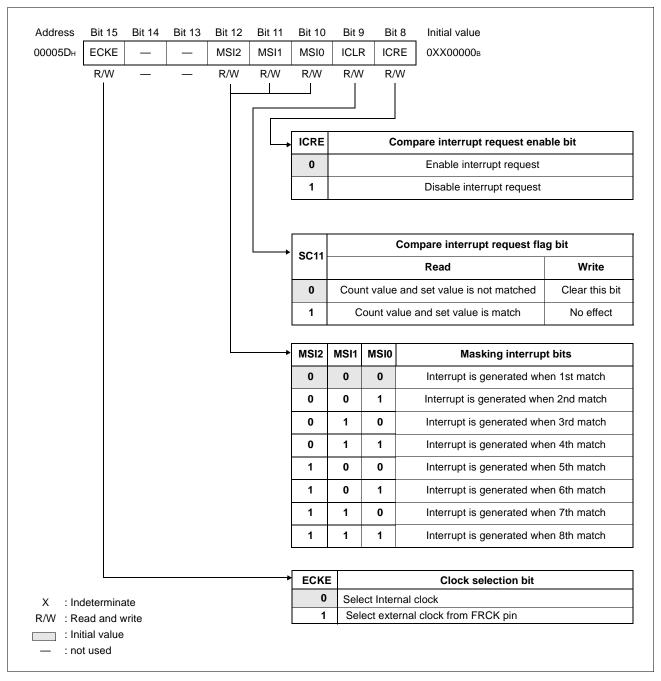

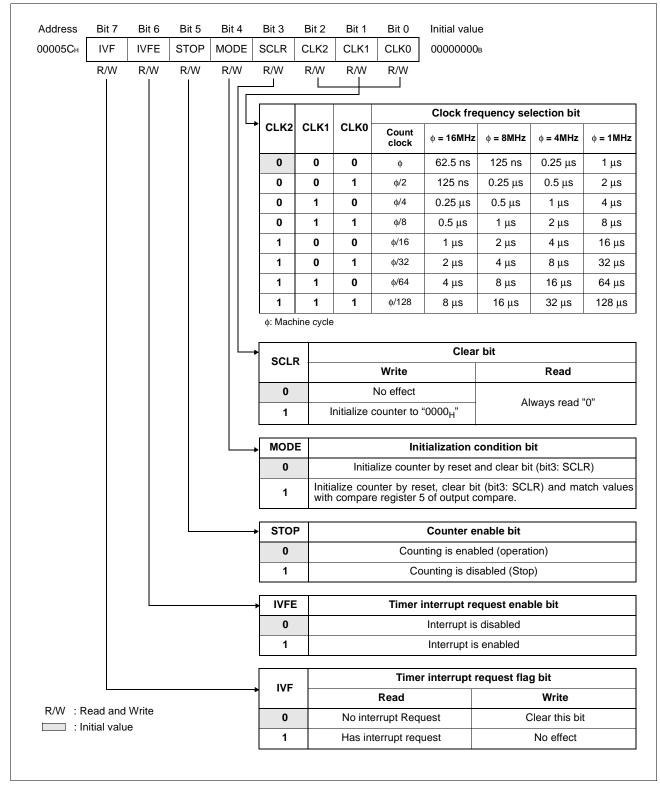

|      | 12.3.1.3 Timer Control Status Register (TCCS)                     | 294 |

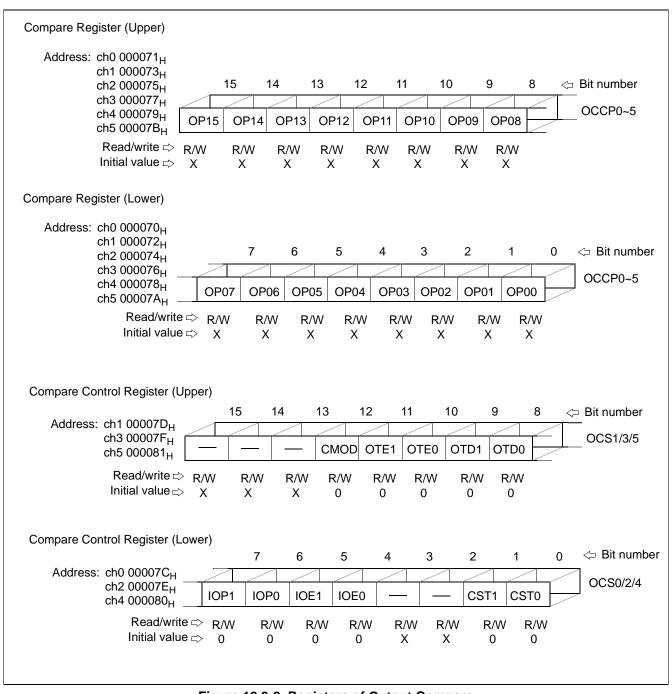

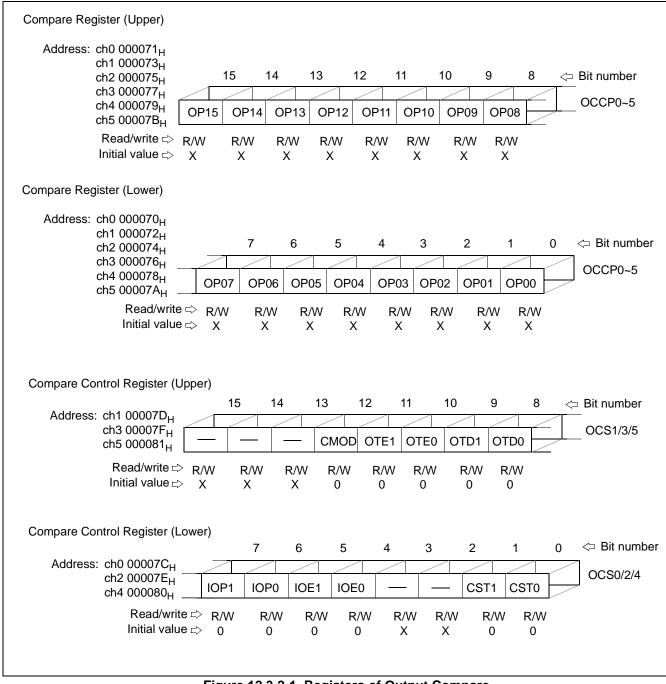

| 12.  | 3.2 Registers of 16-bit Output Compare                            |     |

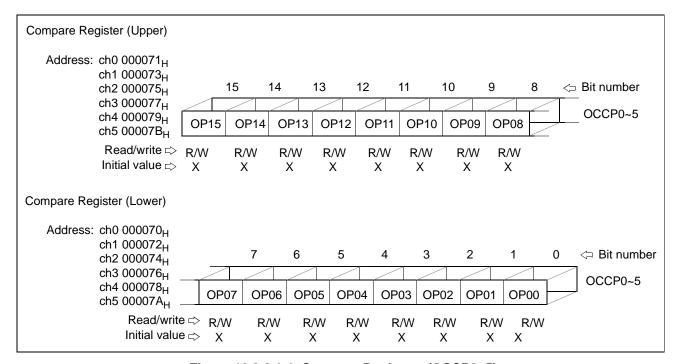

|      | 12.3.2.1 Compare Registers (OCCP0~5)                              |     |

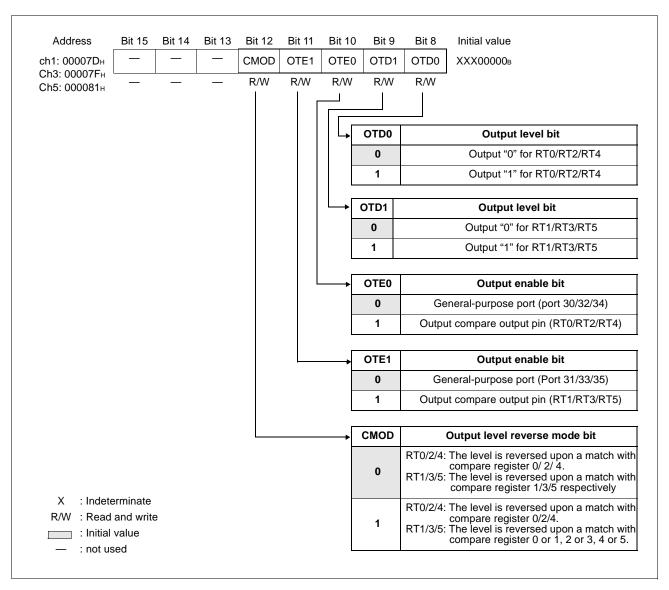

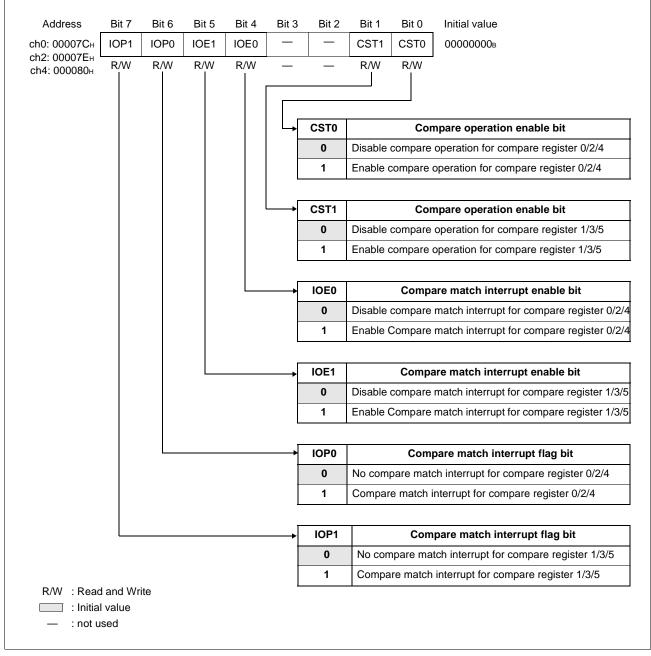

|      | 12.3.2.2 Compare Control Registers (OSC0/1/2/3/4/5)               |     |

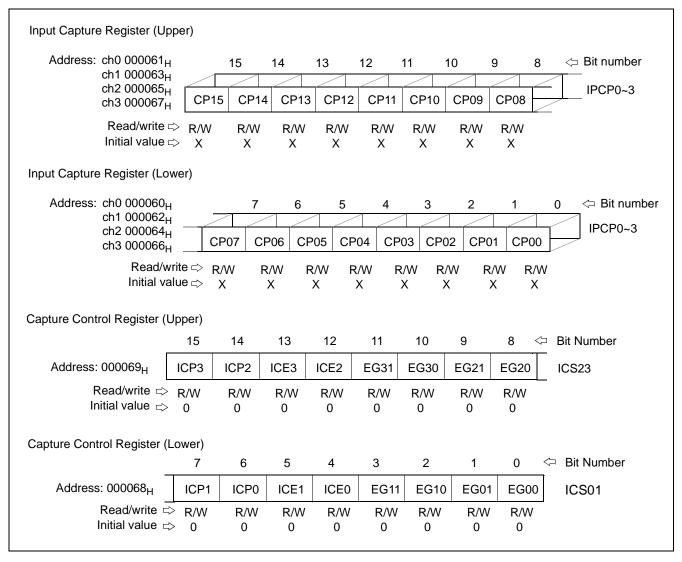

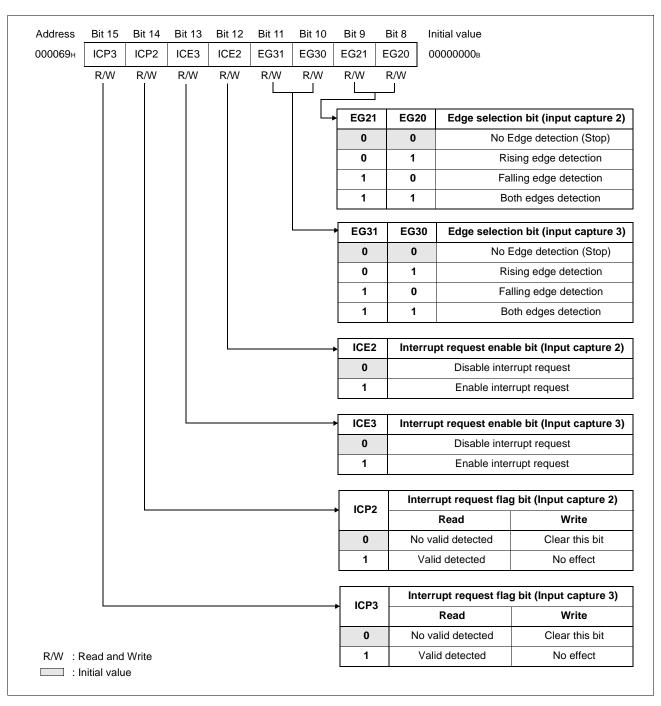

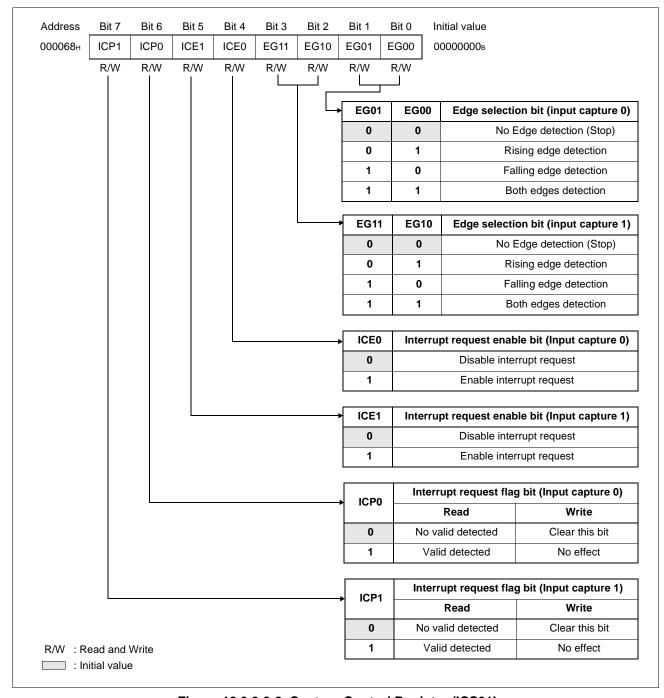

| 12.  | 3.3 Registers of 16-bit Input Capture                             |     |

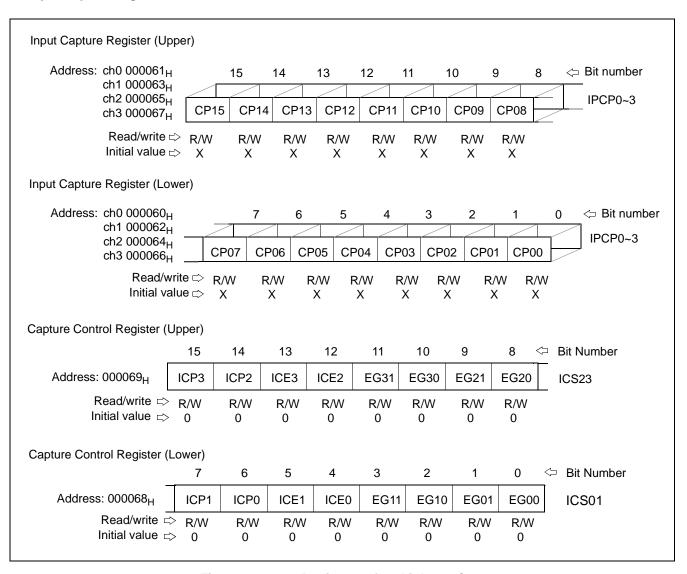

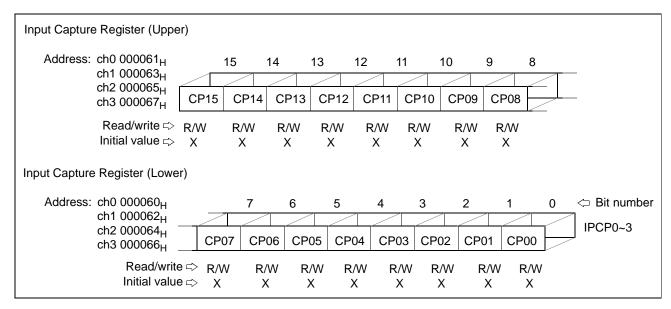

|      | 12.3.3.1 Input Capture Register (IPCP0~3)                         |     |

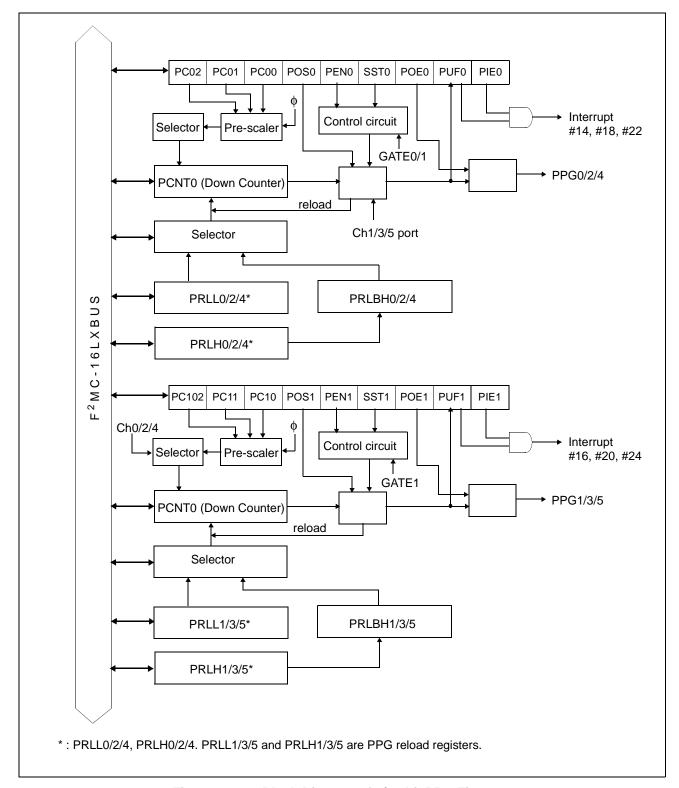

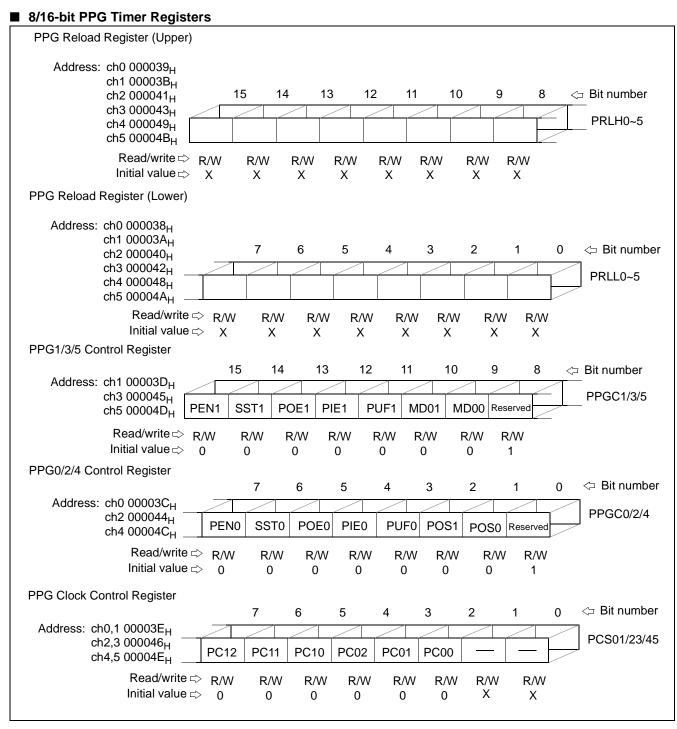

| 10   | 3.4 Register of 8/16-bit PPG Timer                                |     |

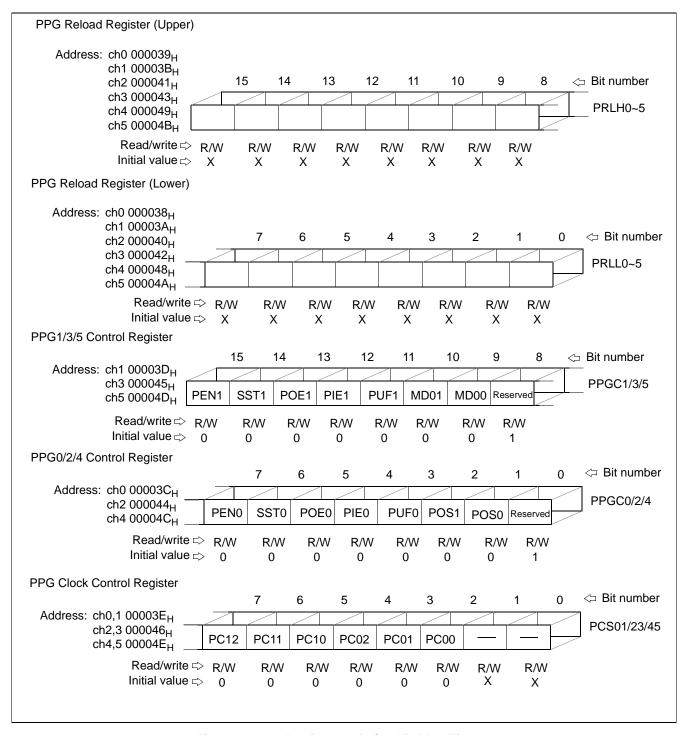

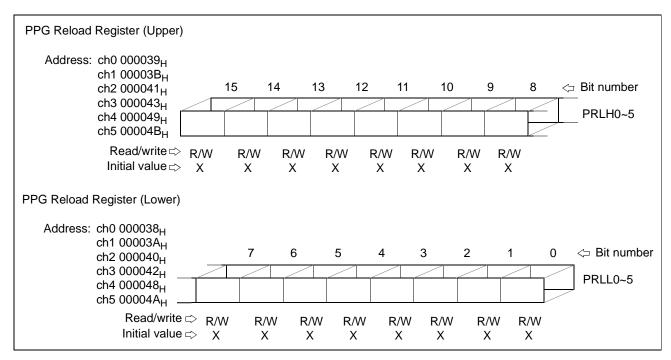

| 12.  | 12.3.4.1 PPG Reload Register (PRLH0~5, PRLL0~5)                   |     |

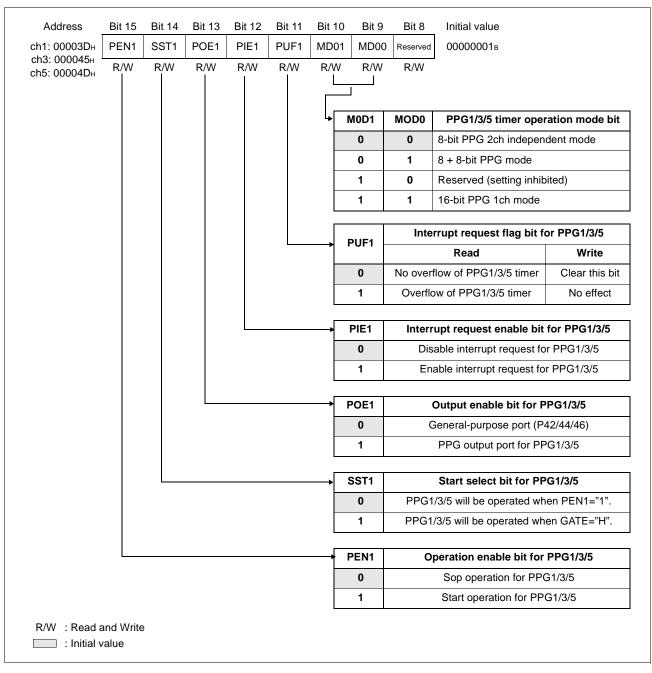

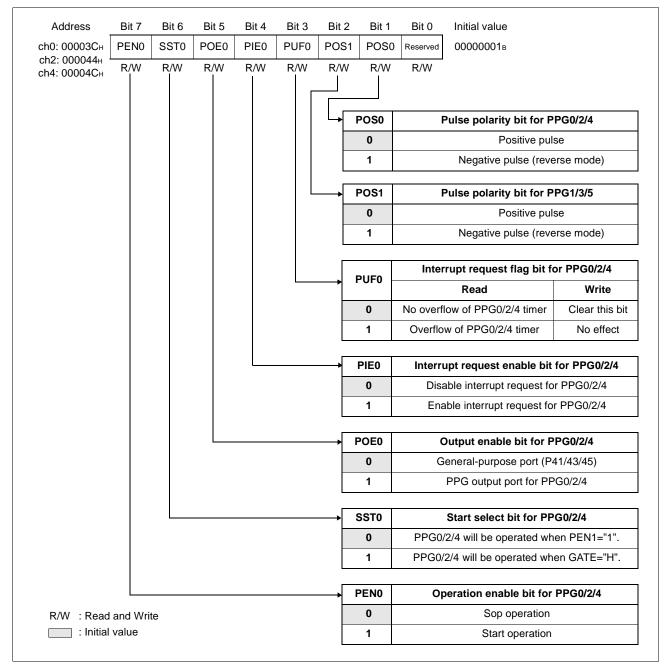

|      | 12.3.4.2 PPG Control Register (PPGC0~5)                           |     |

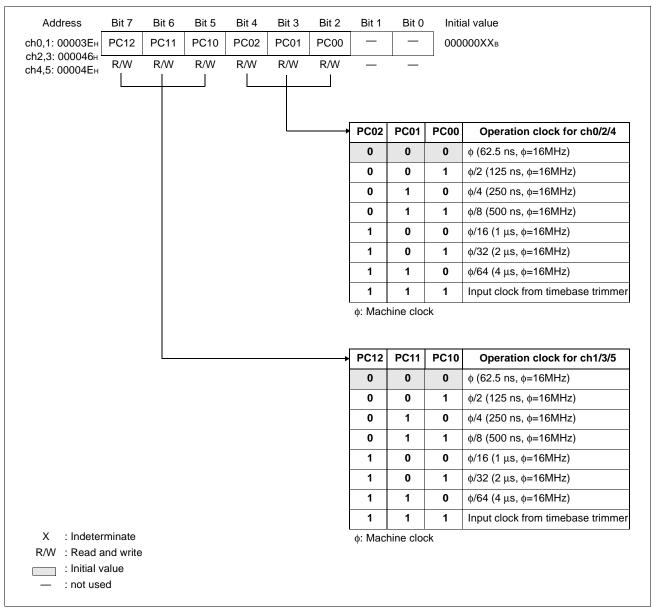

|      | 12.3.4.3 PPG Clock Control Register (PCS01/23/45)                 |     |

| 12.  | 3.5 Registers of Waveform Generator                               | 318 |

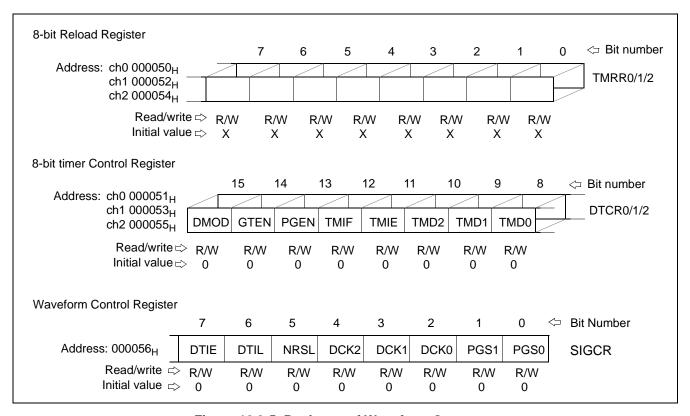

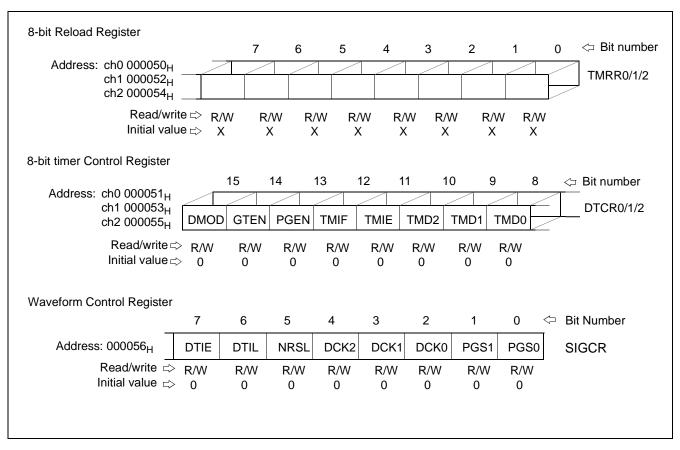

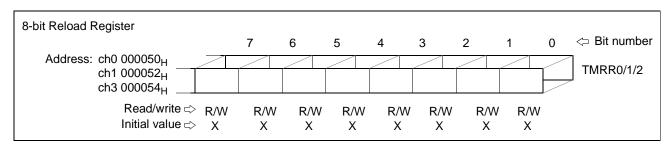

|      | 12.3.5.1 8-bit Reload Register (TMRR0/1/2)                        |     |

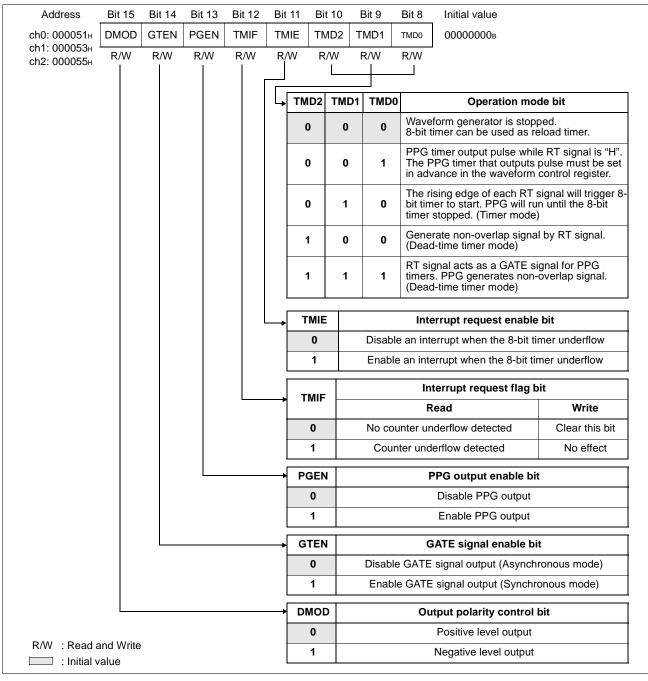

|      | 12.3.5.2 8-bit Timer Control Register (DTCR0/1/2)                 |     |

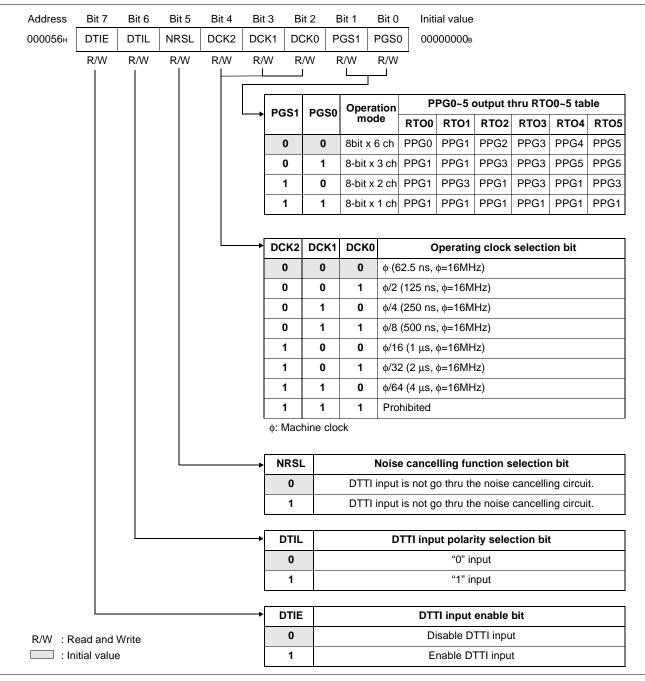

|      | 12.3.5.3 Waveform Control Register (SIGCR)                        |     |

| 12.4 | Operation of Multi-Function Timer                                 |     |

| 12.  | -1                                                                |     |

| 12.  | , ,                                                               |     |

| 12.  | ·                                                                 |     |

| 12.  | '                                                                 |     |

| 12.  | '                                                                 |     |

|      | 12.4.5.1 Operation of Dead-timer Control Circuit                  |     |

|      | 12.4.5.2 Operation of PPG Output and GATE Signal Control Circuit  |     |

|      | 12.4.0.0 Operation of DTTT Fill Control                           | 348 |

| CHAF | PTER 13 UART                                                      | 351 |

| 13.1 | Overview of UART                                                  | 352 |

| 13.2 | Configuration of UART                                             | 354 |

|      |                                                                   |     |

| 13.3         | UART Pins                                                                                | 358 |

|--------------|------------------------------------------------------------------------------------------|-----|

| 13.4         | UART Registers                                                                           | 360 |

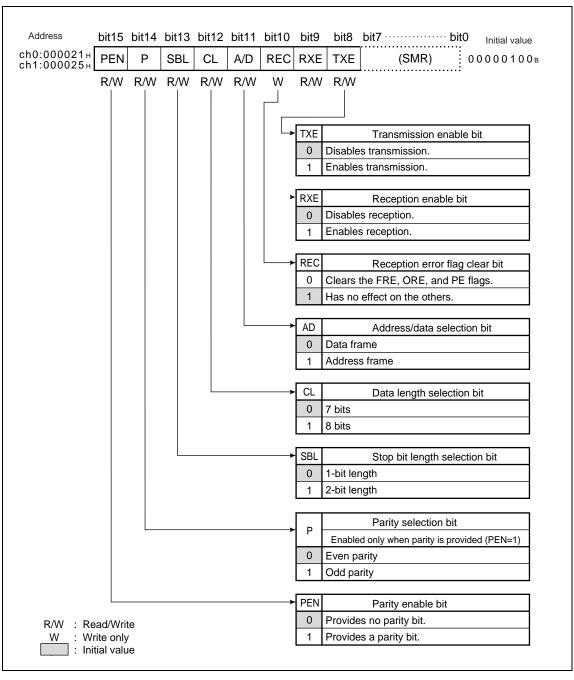

| 13.4         | 1 Serial Control Register 1 (SCR0/1)                                                     | 362 |

| 13.4         | 2 Serial Mode Control Register (SMR0/1)                                                  | 364 |

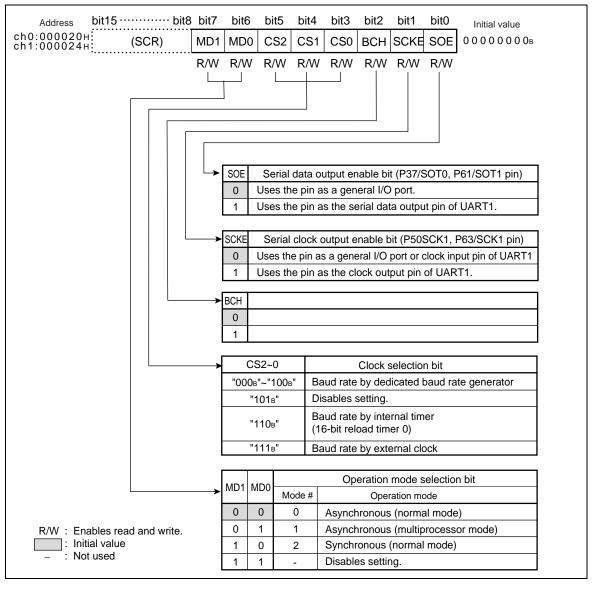

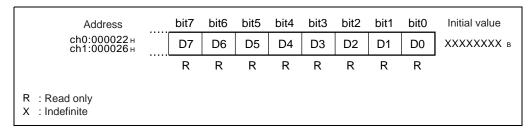

| 13.4         | -3 Serial Status Register (SSR0/1)                                                       | 366 |

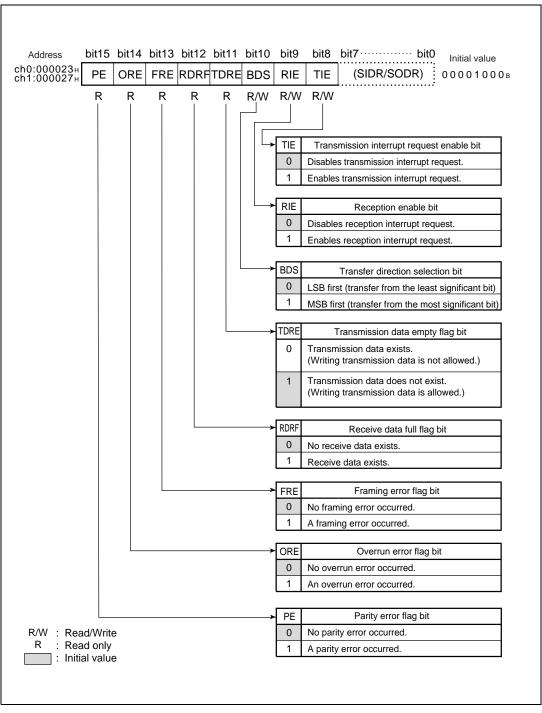

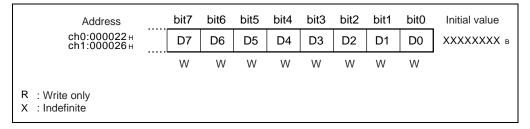

| 13.4         | .4 Serial Input Data Register (SIDR0/1) and Serial Output Data Register (SOR0/1)         | 368 |

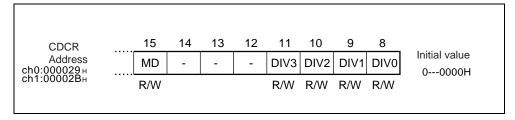

| 13.4         | .5 Communication Prescaler Control Register (CDCR0/1)                                    | 370 |

| 13.5         | UART Interrupts                                                                          | 372 |

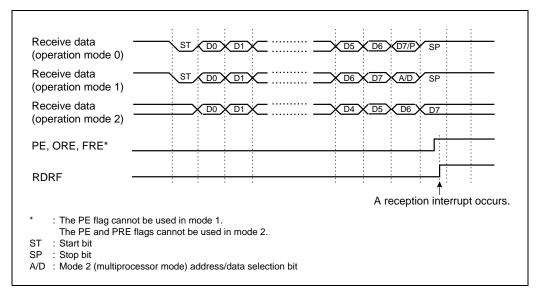

| 13.5         | .1 Reception Interrupt Generation and Flag Set Timing                                    | 374 |

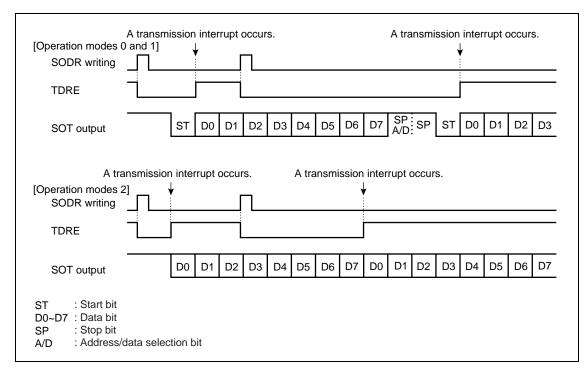

| 13.5         |                                                                                          |     |

| 13.6         | UART Baud Rates                                                                          |     |

| 13.6         | 9                                                                                        |     |

| 13.6         | ,                                                                                        |     |

| 13.6         | · · · · · · · · · · · · · · · · · · ·                                                    |     |

| 13.7         | ·                                                                                        |     |

| 13.7         |                                                                                          |     |

| 13.7         |                                                                                          |     |

| 13.7         | ,                                                                                        |     |

| 13.7         | ,                                                                                        |     |

| 13.8         | Notes on Using UART                                                                      |     |

| 13.9         | Sample Program for UART                                                                  | 398 |

| JIIA D.      | TED 44 DTD/EVTEDNAL INTERDURT CIRCUIT                                                    | 404 |

|              | TER 14 DTP/EXTERNAL INTERRUPT CIRCUIT                                                    |     |

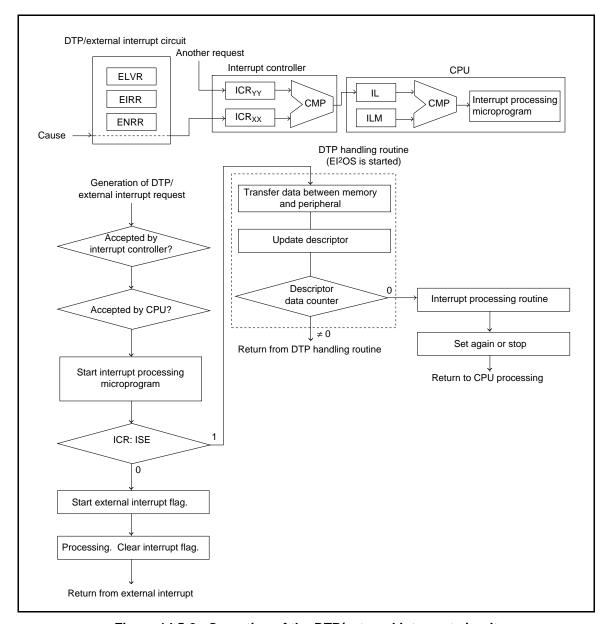

| 14.1         | Overview of the DTP/External Interrupt Circuit                                           |     |

| 14.2         | Configuration of the DTP/External Interrupt Circuit                                      |     |

| 14.3         | DTP/External Interrupt Circuit Pins                                                      |     |

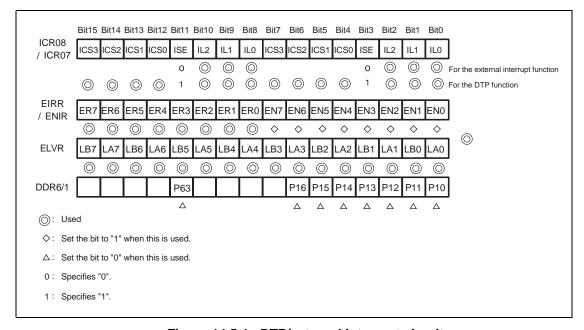

| 14.4         | DTP/External Interrupt Circuit Registers                                                 |     |

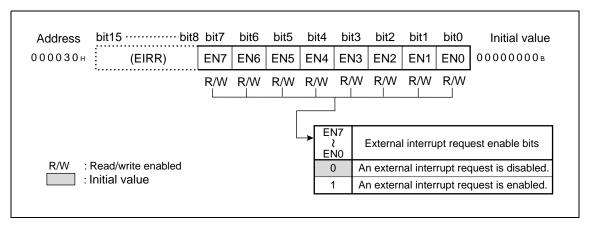

| 14.4         |                                                                                          |     |

| 14.4         |                                                                                          |     |

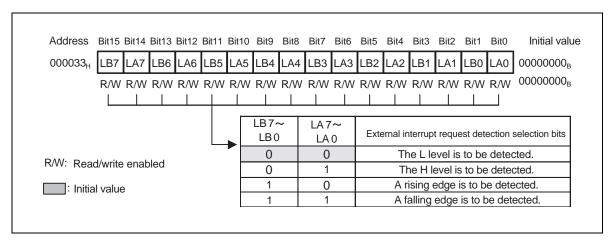

| 14.4         | .3 Request level setting register (ELVR) Operation of the DTP/External Interrupt Circuit |     |

| 14.5<br>14.5 | ·                                                                                        |     |

| 14.5         | ·                                                                                        |     |

| 14.5         | Usage Notes on the DTP/External Interrupt Circuit                                        |     |

| 14.7         | Sample Programs for the DTP/External Interrupt Circuit                                   |     |

| 14.7         | Sample Programs for the DTP/External interrupt Circuit                                   | 422 |

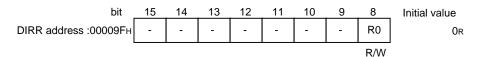

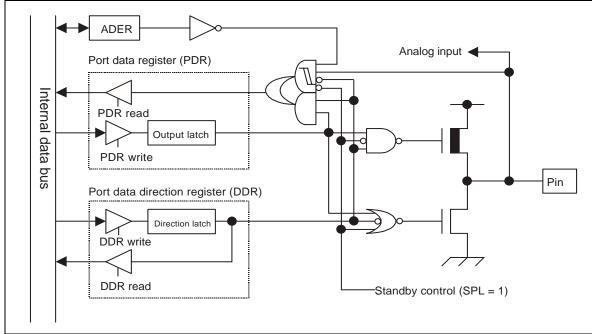

| CHAP         | TER 15 Delayed Interrupt Generator Module                                                | 427 |

| 15.1         | Overview of the Delayed Interrupt Generator Module                                       |     |

| 15.2         | Operation of the Delayed Interrupt Generator Module                                      |     |

| 10.2         | operation of the Boldycu interrupt centrator Module                                      |     |

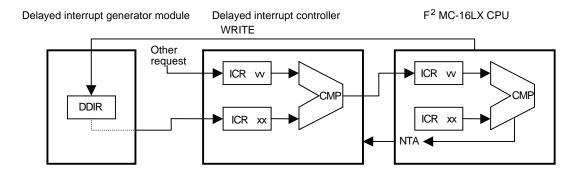

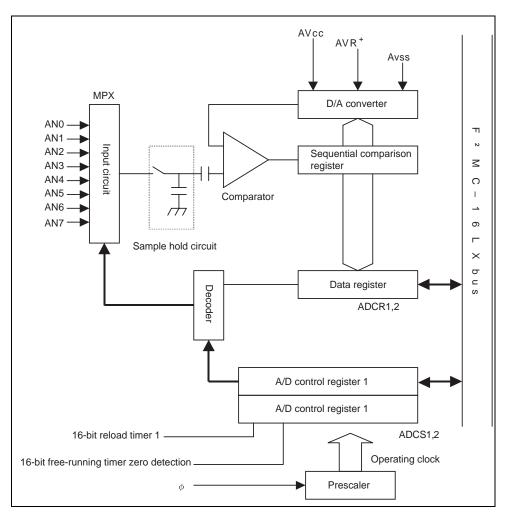

| CHAP         | TER 16 8/10-BIT A/D CONVERTER                                                            | 431 |

| 16.1         | Overview of the 8/10-Bit A/D Converter                                                   | 432 |

| 16.2         | Configuration of the 8/10-Bit A/D Converter                                              | 434 |

| 16.3         | 8/10-Bit A/D Converter Pins                                                              | 436 |

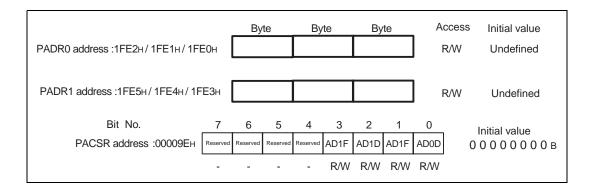

| 16.4         | 8/10-Bit A/D Converter Registers                                                         | 438 |

| 16.4         |                                                                                          |     |

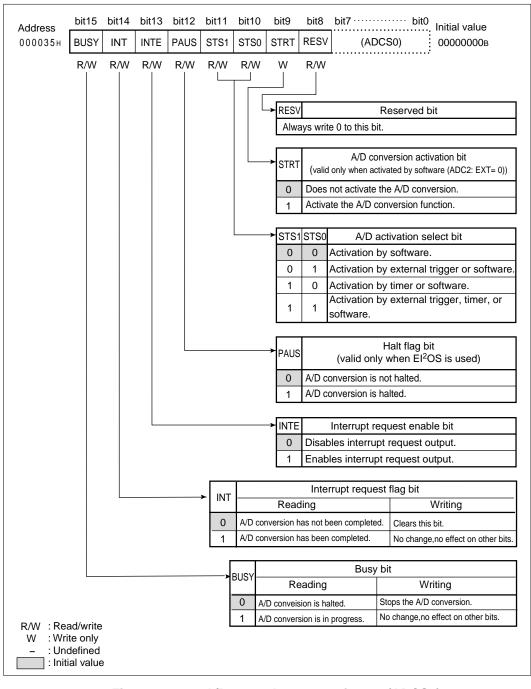

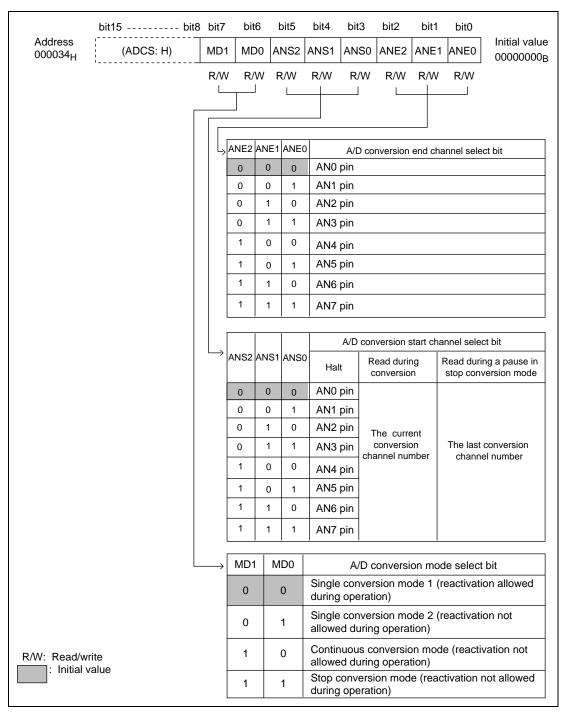

| 16.4         | 2 A/D control status register 0 (ADCS0)                                                  | 442 |

MB90560 series

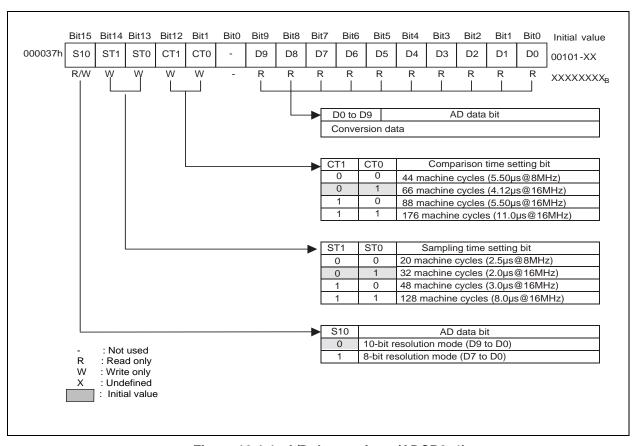

| 16.4  | 4.3 A/D data register (ADCR0, 1)                                         | 444 |

|-------|--------------------------------------------------------------------------|-----|

| 16.5  | 8/10-Bit A/D Converter Interrupts                                        | 446 |

| 16.6  | Operation of the 8/10-Bit A/D Converter                                  | 447 |

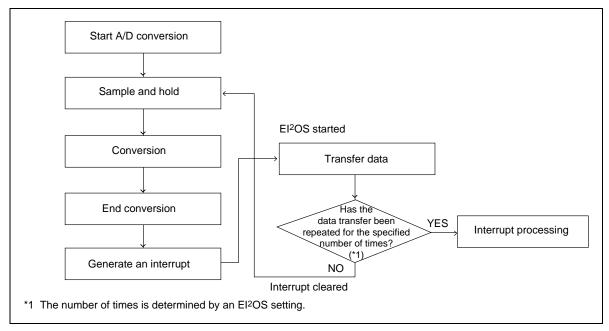

| 16.6  | 6.1 Conversion using El <sup>2</sup> OS                                  | 450 |

| 16.6  | 6.2 A/D conversion data protection function                              | 452 |

| 16.7  | Usage Notes on the 8/10-Bit A/D Converter                                | 454 |

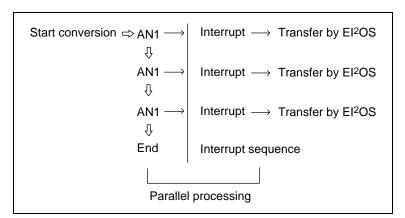

| 16.8  | Sample Program 1 for Single Conversion Mode Using El <sup>2</sup> OS     | 456 |

| 16.9  | Sample Program 2 for Continuous Conversion Mode Using El <sup>2</sup> OS | 458 |

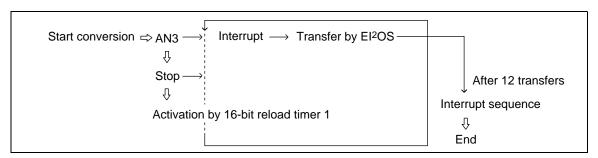

| 16.10 | Sample Program 3 for Stop Conversion Mode Using El <sup>2</sup> OS       | 461 |

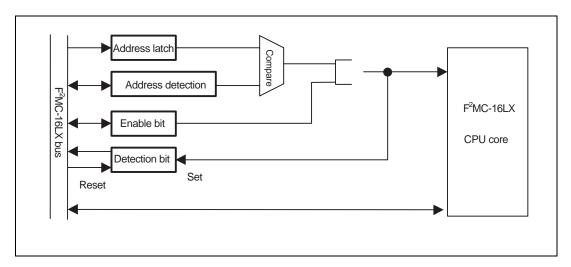

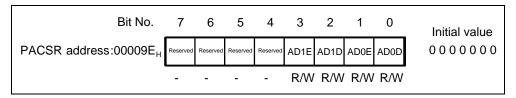

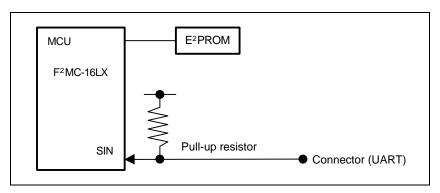

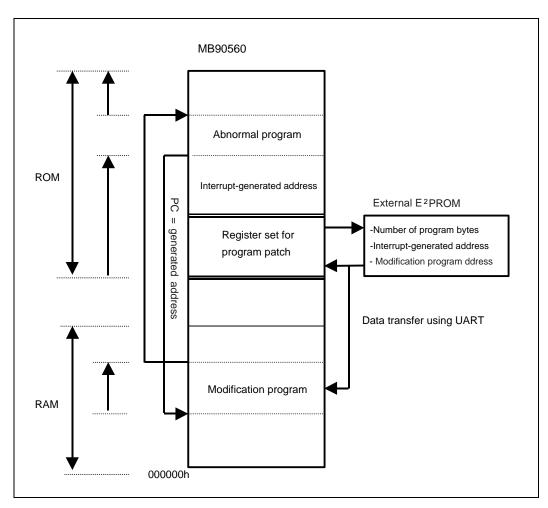

| CHAP  | TER 17 ADDRESS MATCH DETECTION FUNCTION                                  | 465 |

| 17.1  | Overview of the Address Match Detection Function                         | 466 |

| 17.2  | Example of Using the Address Match Detection Function                    |     |

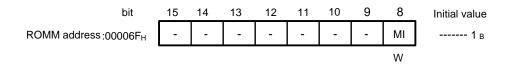

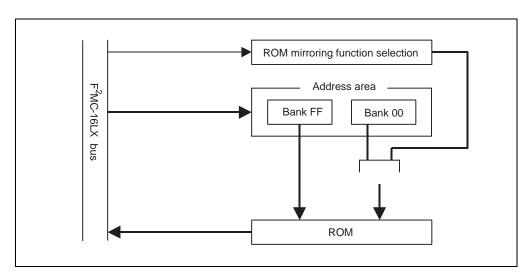

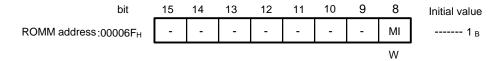

| CHAP  | TER 18 ROM MIRRORING FUNCTION SELECTION MODULE                           | 473 |

| 18.1  | Overview of the ROM Mirroring Function Selection Module                  | 474 |

| APPEI | NDIX                                                                     | 477 |

| APPEI | NDIX A I/O MAP                                                           | 479 |

| APPEI | NDIX B INSTRUCTIONS                                                      | 485 |

| B.1   | Instructions                                                             | 486 |

| B.2   | Addressing                                                               |     |

| B.3   | Direct Addressing                                                        |     |

| B.4   | Indirect Addressing                                                      | 496 |

| B.5   | Number of Execution Cycles                                               | 503 |

| B.6   | Effective-address field                                                  | 506 |

| B.7   | Reading the Instruction List                                             | 507 |

| B.8   | List of F2MC-16LX Instructions                                           |     |

| B.9   | Instruction Maps                                                         | F00 |

|       | mstruction waps                                                          | 523 |

|       | NDIX C 512K-BIT FLASH MEMORY                                             |     |

| APPEI |                                                                          |     |

viii MB90560 series

# **FIGURES**

| Figure 1.3-2  | Block diagram                                                                                     | 5   |

|---------------|---------------------------------------------------------------------------------------------------|-----|

| Figure 1.4-1  | Pin assignment of FPT-64P-M09                                                                     | 6   |

| Figure 1.4-2  | Pin assignment of FPT-64P-M09                                                                     | 7   |

| Figure 1.4-3  | Pin assignment of DIP-64P-M01                                                                     | 8   |

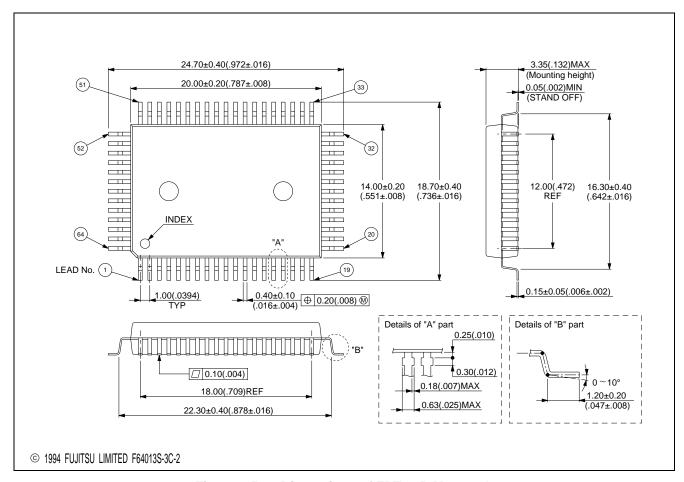

| Figure 1.5-1  | Dimensions of FPT-64P-M06 package                                                                 | .10 |

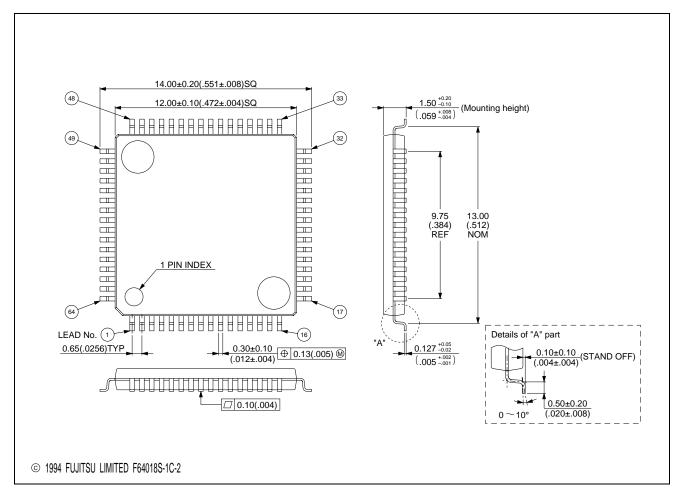

| Figure 1.5-2  | Dimensions of FPT-64P-M09 package                                                                 | .11 |

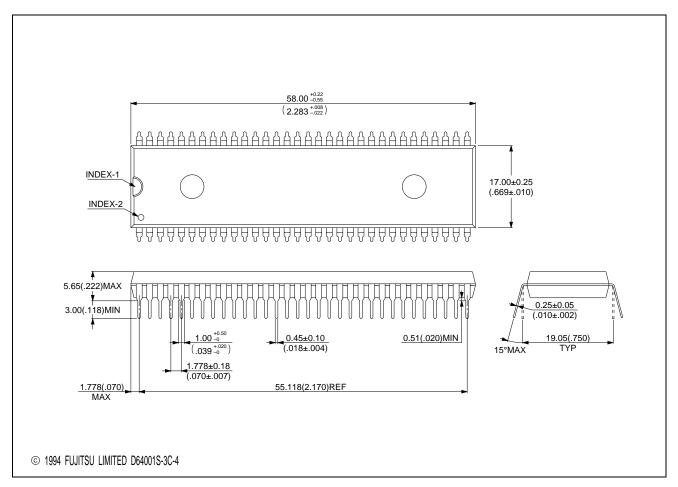

| Figure 1.5-3  | Dimensions of DIP-64P-M01 package                                                                 | .12 |

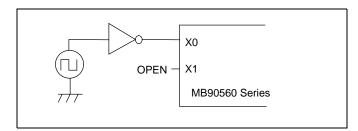

| Figure 1.8-1  | Sample connection of external clock                                                               | .21 |

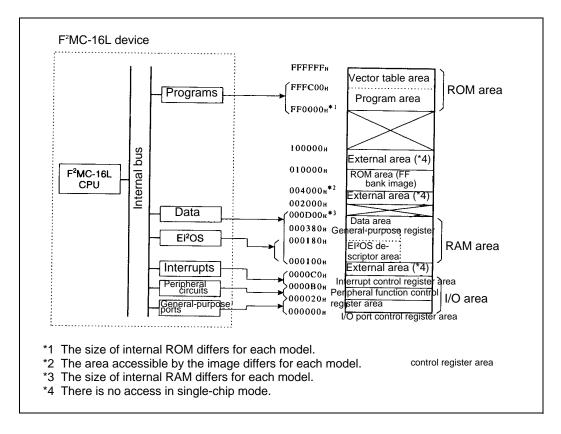

| Figure 2.2-1  | Sample relationship between the F2MC-16LX system and the memory map                               | .26 |

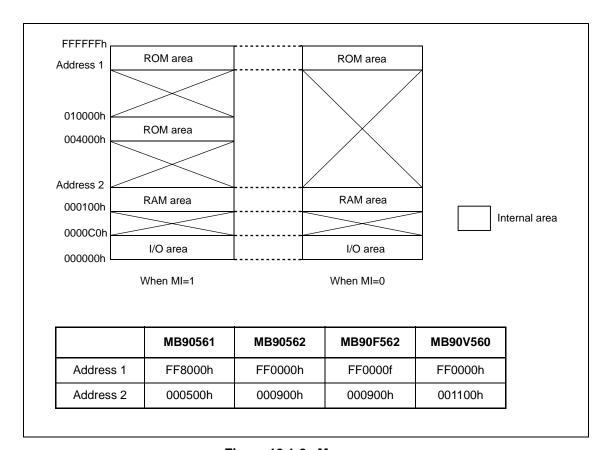

| Figure 2.3-1  | Memory maps                                                                                       | .28 |

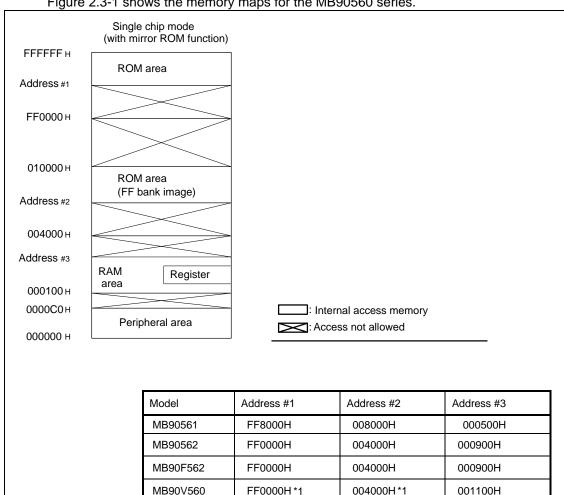

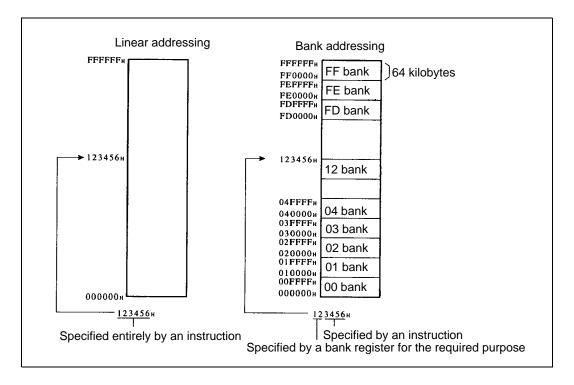

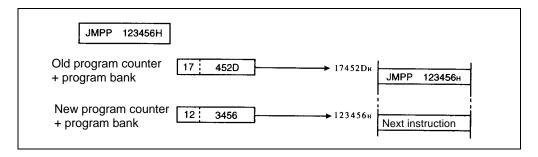

| Figure 2.4-1  | Linear addressing and bank addressing memory management                                           | .29 |

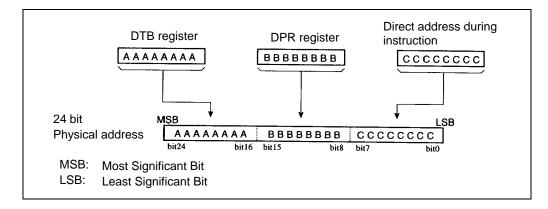

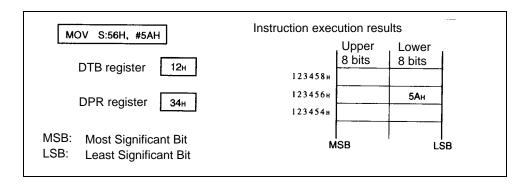

| Figure 2.4-2  | Example of direct specified 24-bit physical address in linear addressing                          | .30 |

| Figure 2.4-3  | Example of indirect specified address with a 32-bit general-purpose register in linear addressing | .30 |

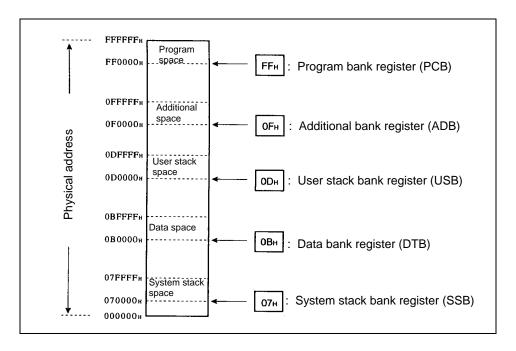

| Figure 2.4-4  | Sample bank addressing                                                                            | .33 |

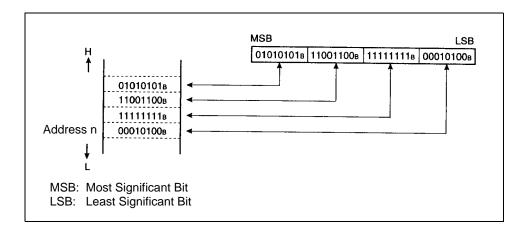

| Figure 2.5-1  | Storage of multibyte data in RAM                                                                  | .34 |

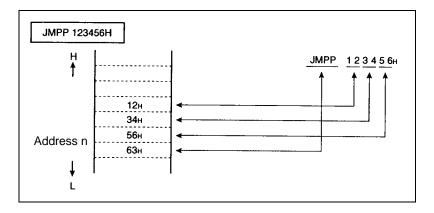

| Figure 2.5-2  | Storage of a multibyte operand                                                                    | .34 |

| Figure 2.5-3  | Storage of multibyte data in a stack                                                              | .35 |

| Figure 2.5-4  | Multibyte data access on a bank boundary                                                          | .35 |

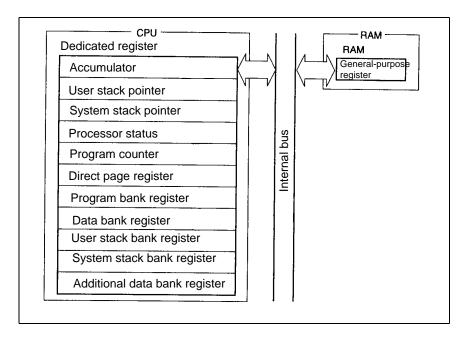

| Figure 2.6-1  | Dedicated registers and general-purpose registers                                                 | .36 |

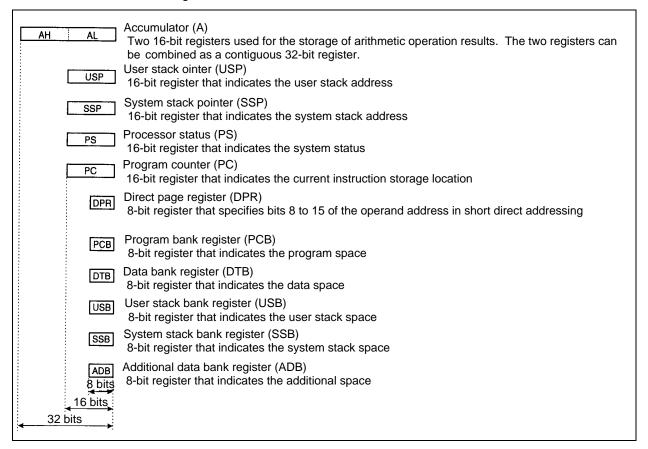

| Figure 2.7-1  | Configuration of dedicated registers                                                              | .39 |

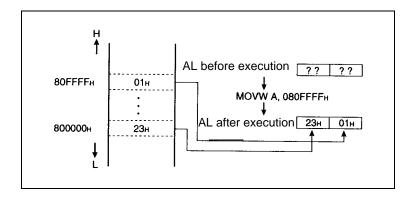

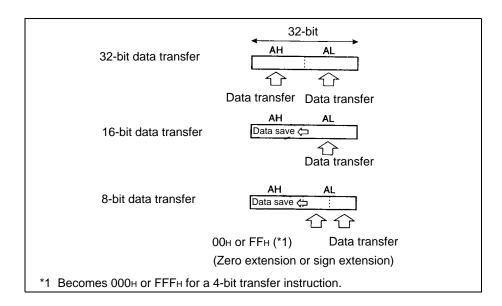

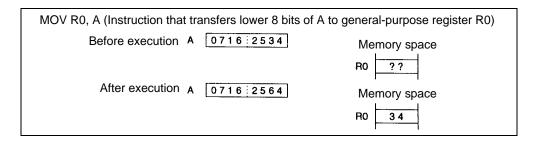

| Figure 2.7-2  | Data transfer to the accumulator                                                                  | .40 |

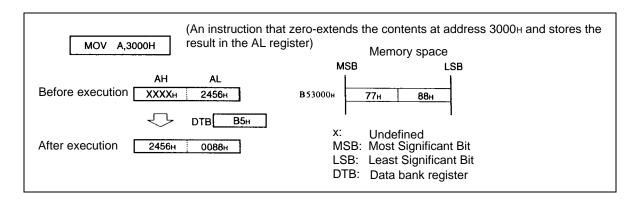

| Figure 2.7-3  | Example of AL-AH transfer in the accumulator (A) (8-bit immediate value, zero extension)          | 41  |

| Figure 2.7-4  | Example of AL-AH transfer in the accumulator (A) (8-bit immediate value, sign extension)          | .41 |

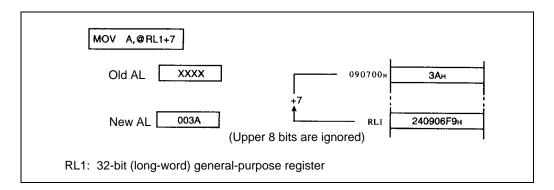

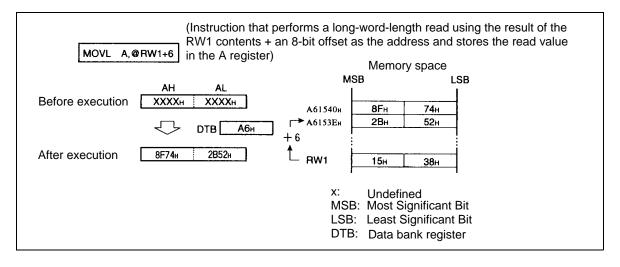

| Figure 2.7-5  | Example of 32-bit data transfer to the accumulator (A) (register indirect)                        | .41 |

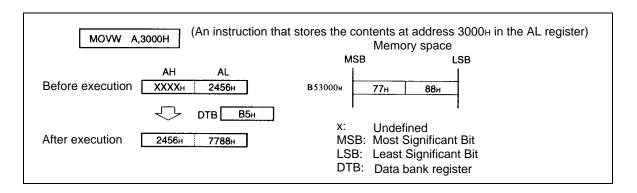

| Figure 2.7-6  | Example of AL-AH transfer in the accumulator (A) (16 bits, register indirect)                     | .42 |

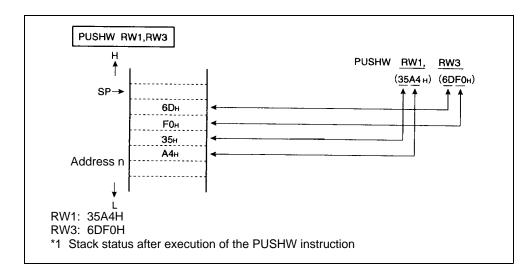

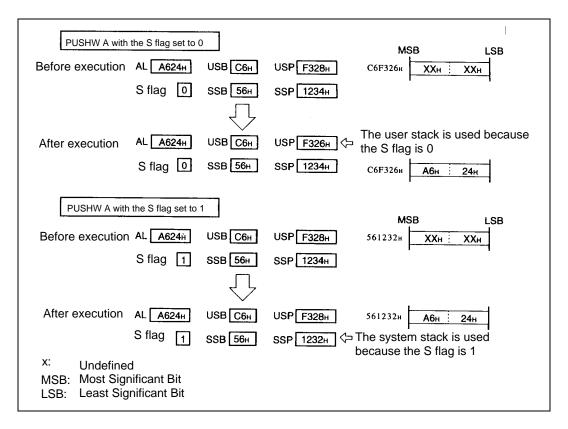

| Figure 2.7-7  | Stack operation instruction and stack pointer                                                     | .45 |

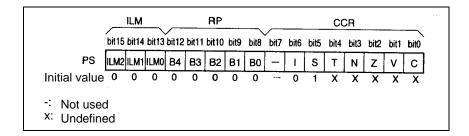

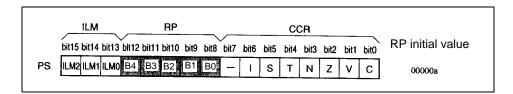

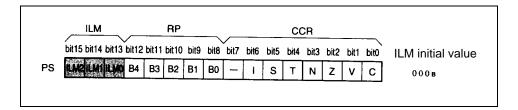

| Figure 2.7-8  | Processor status (PS) configuration                                                               | .46 |

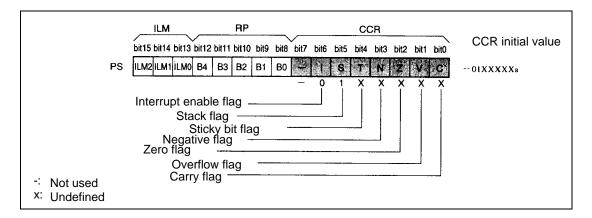

| Figure 2.7-9  | Condition code register (CCR) configuration                                                       | .48 |

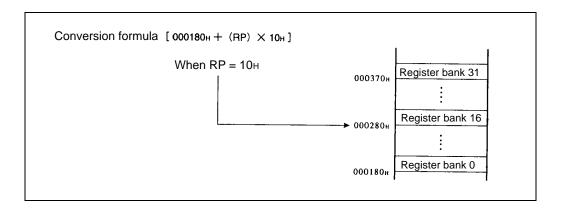

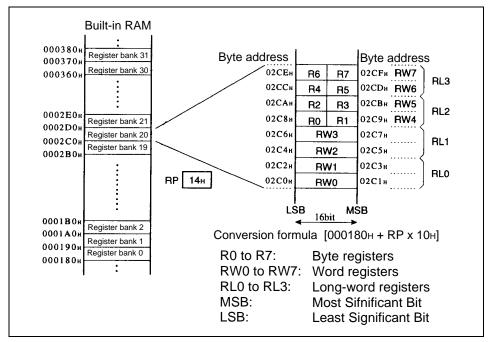

| Figure 2.7-10 | Configuration of the register bank pointer (RP)                                                   | .50 |

| Figure 2.7-11 | Conversion rules for physical address of general-purpose register area                            | .50 |

| Figure 2.7-12 | Configuration of the interrupt level mask register (ILM)                                          | .51 |

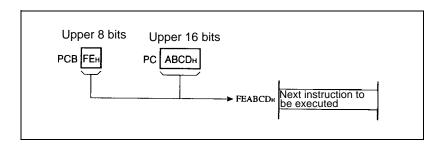

| Figure 2.7-13 | Program counter (PC)                                                                              | .52 |

| Figure 2.7-14 | Physical address generation by the direct page register (DPR)                                     | .53 |

| Figure 2.7-15 | Example of direct page register (DPR) setting and data access                                     | .53 |

| Figure 2.8-1 | Location and configuration of the general-purpose register banks in the memory space .    | 56  |

|--------------|-------------------------------------------------------------------------------------------|-----|

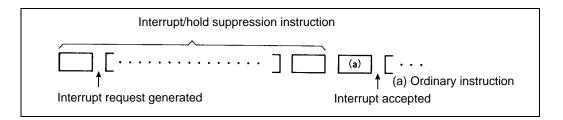

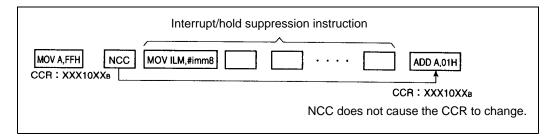

| Figure 2.9-1 | Interrupt/hold suppression                                                                | 64  |

| Figure 2.9-2 | Interrupt/hold suppression instructions and prefix codes                                  | 65  |

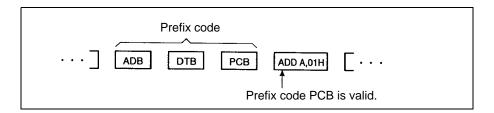

| Figure 2.9-3 | Consecutive prefix codes                                                                  | 65  |

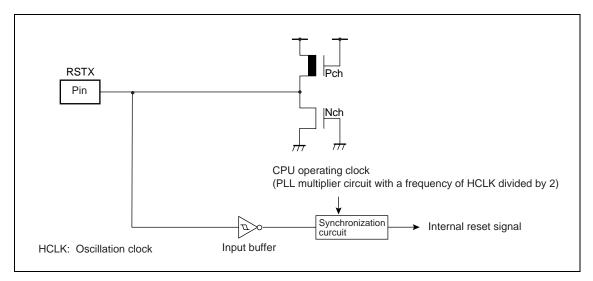

| Figure 3.3-1 | Block diagram of internal reset                                                           | 72  |

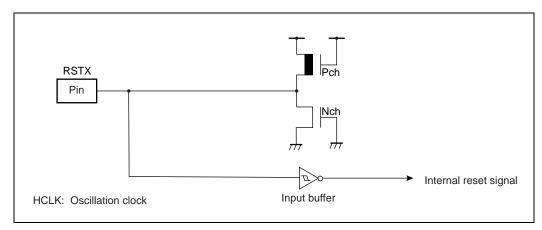

| Figure 3.3-2 | Block diagram of internal reset for external pin                                          | 73  |

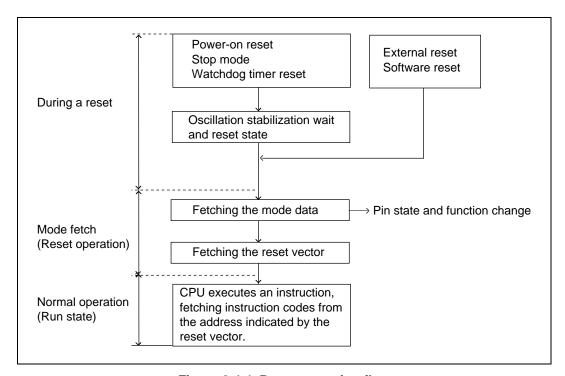

| Figure 3.4-1 | Reset operation flow                                                                      | 74  |

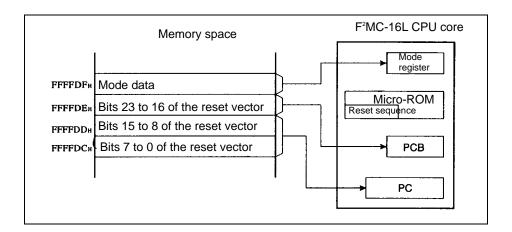

| Figure 3.4-2 | Transfer of reset vector and mode data                                                    | 75  |

| Figure 3.5-1 | Block diagram of reset cause bits                                                         | 76  |

| Figure 3.5-2 | Configuration of reset cause bits (watchdog timer control register)                       | 77  |

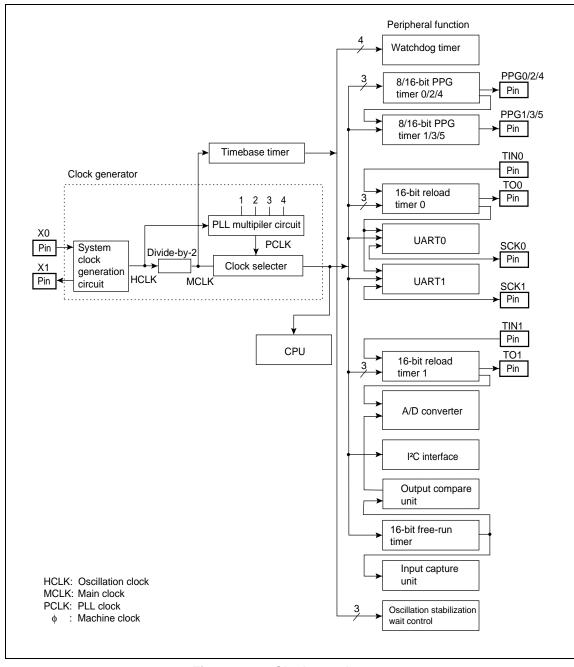

| Figure 4.1-1 | Clock supply map                                                                          | 83  |

| Figure 4.2-1 | Block diagram of the clock generator                                                      | 84  |

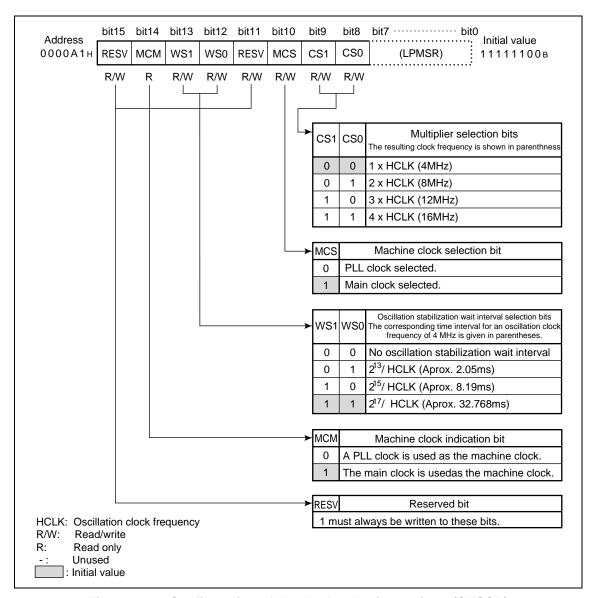

| Figure 4.3-1 | Configuration of the clock selection register (CKSCR)                                     | 86  |

| Figure 4.4-1 | Status change diagram for machine clock selection                                         | 89  |

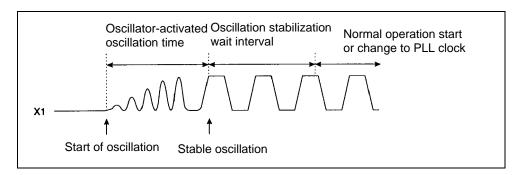

| Figure 4.5-1 | Operation when oscillation starts                                                         | 90  |

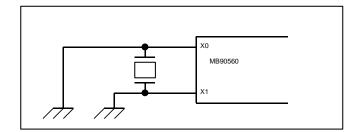

| Figure 4.6-1 | Example of connecting a crystal or ceramic oscillator to the microcontroller              | 91  |

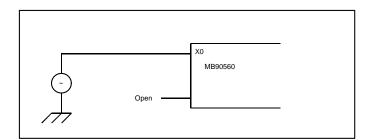

| Figure 4.6-2 | Example of connecting an external clock to the microcontroller                            | 91  |

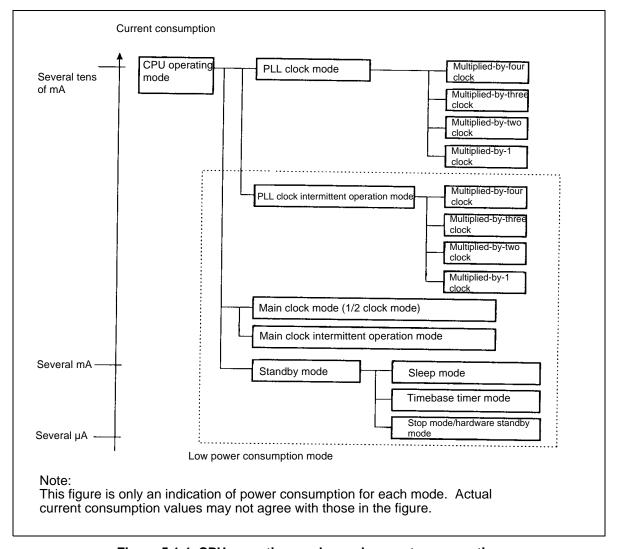

| Figure 5.1-1 | CPU operating modes and current consumption                                               | 94  |

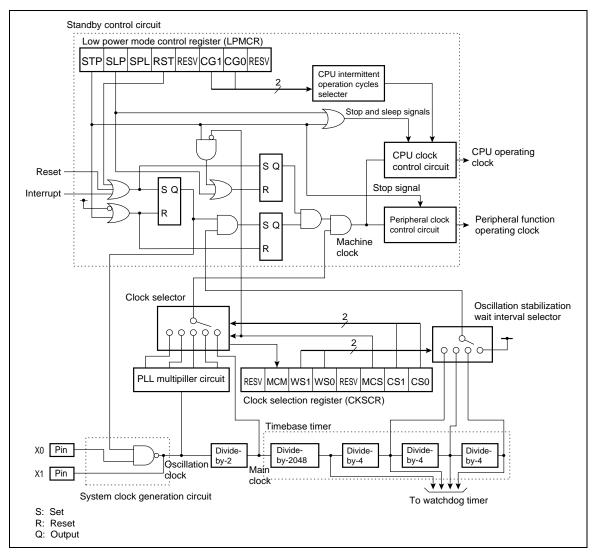

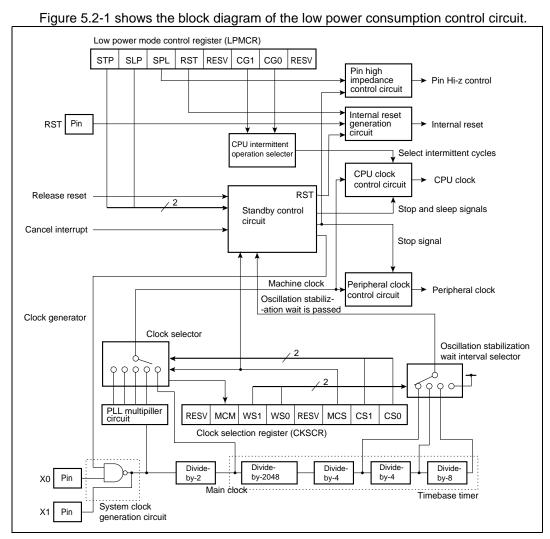

| Figure 5.2-1 | Block diagram of the low power consumption control circuit                                | 96  |

| Figure 5.3-1 | Configuration of the low power consumption mode control register (LPMCR)                  | 98  |

| Figure 5.4-1 | Clock pulses during CPU intermittent operation                                            | 102 |

| Figure 5.5-1 | Release of sleep mode for an interrupt                                                    | 105 |

| Figure 5.5-2 | Release of PLL sleep mode (by external reset)                                             | 106 |

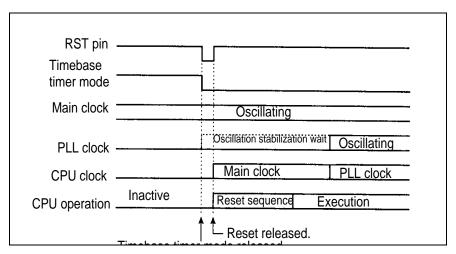

| Figure 5.5-3 | Release of timebase timer mode (by an external reset)                                     | 109 |

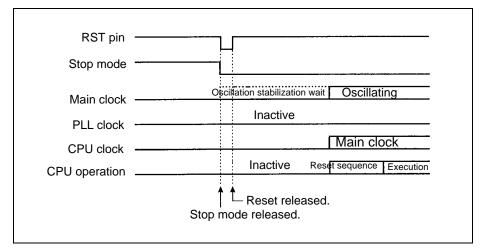

| Figure 5.5-4 | Release of stop mode (by external reset)                                                  | 111 |

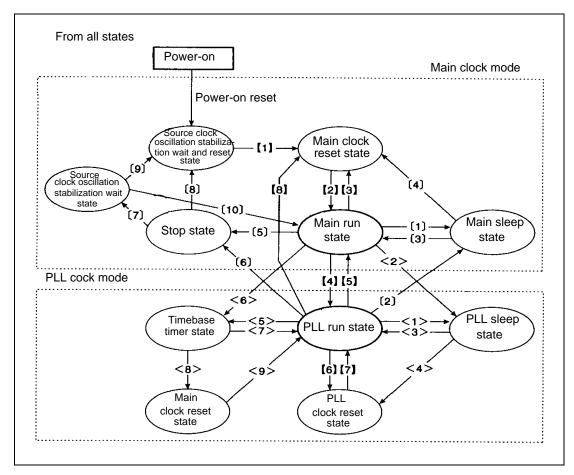

| Figure 5.6-1 | Status change diagram                                                                     | 112 |

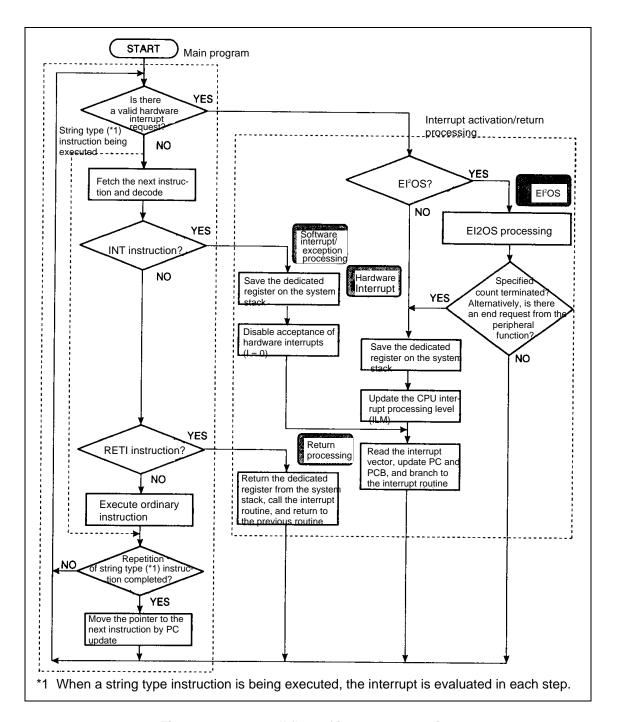

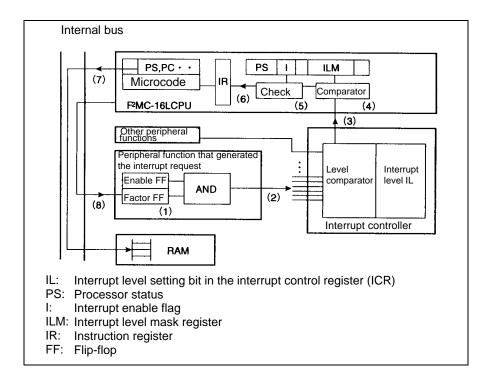

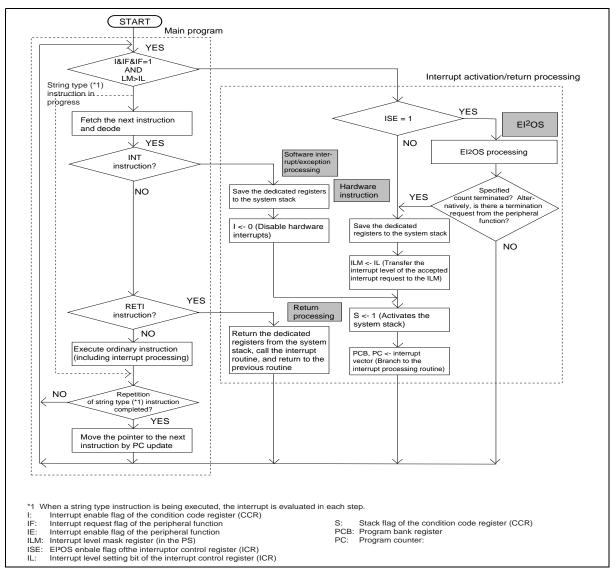

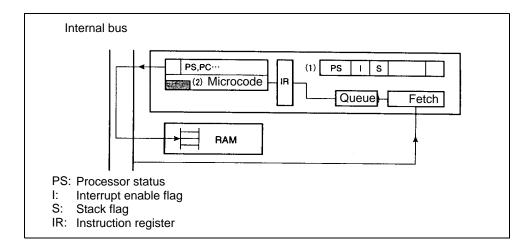

| Figure 6.1-1 | Overall flow of interrupt operation                                                       | 121 |

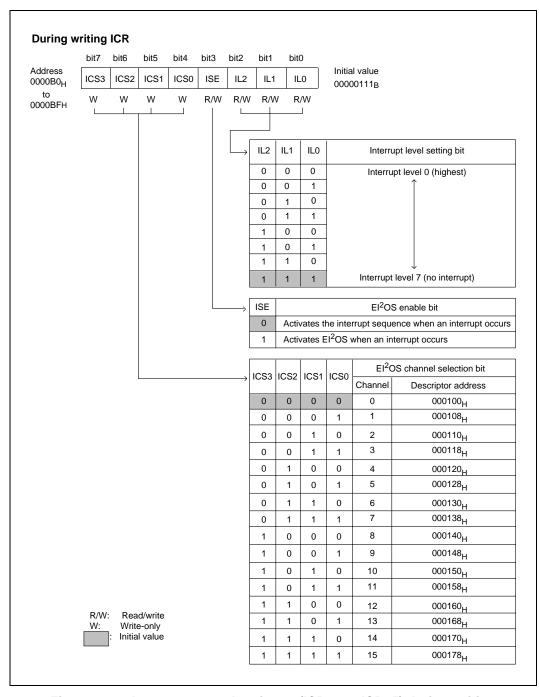

| Figure 6.3-1 | Interrupt control registers (ICR00 to ICR15) during writing                               | 126 |

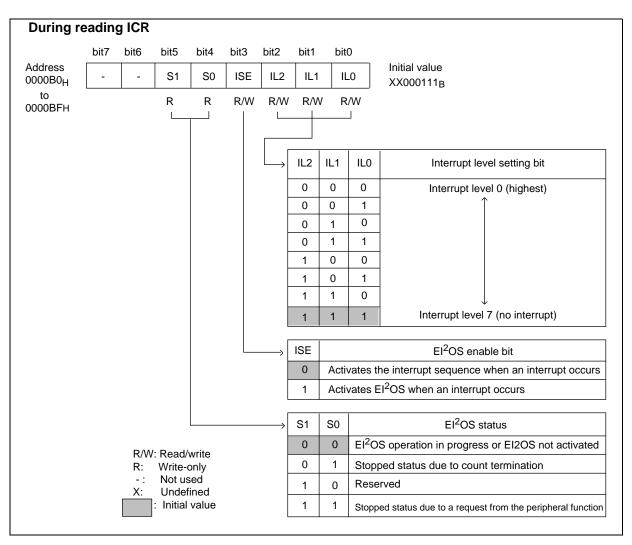

| Figure 6.3-2 | Interrupt control registers (ICR00 to ICR15) during reading                               | 127 |

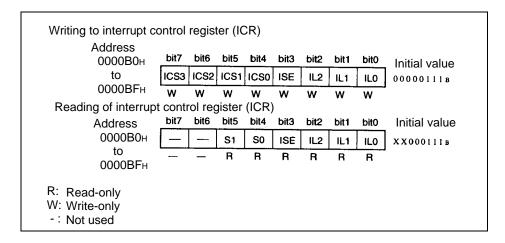

| Figure 6.3-3 | Configuration of interrupt control registers (ICR)                                        | 128 |

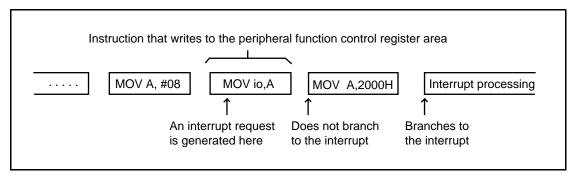

| Figure 6.4-1 | Hardware interrupt request while writing to the peripheral function control register area | 134 |

| Figure 6.4-2 | Hardware interrupt operation                                                              | 137 |

| Figure 6.4-3 | Flow of interrupt processing                                                              | 138 |

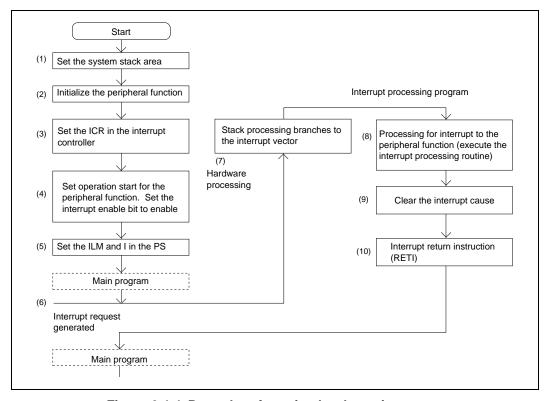

| Figure 6.4-4 | Procedure for using hardware interrupts                                                   | 139 |

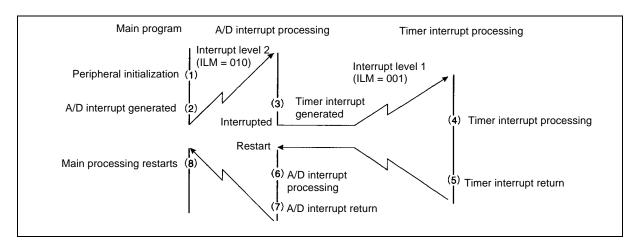

| Figure 6.4-5 | Example of multiple interrupts                                                            | 141 |

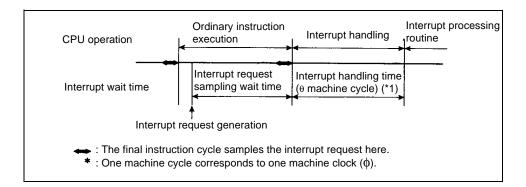

| Figure 6.4-6 | Interrupt processing time                                                                 | 142 |

| Figure 6.5-1 | Software interrupt operation                                                              | 145 |

X MB90560 series

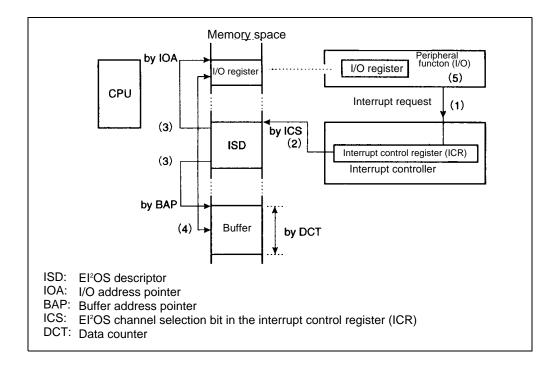

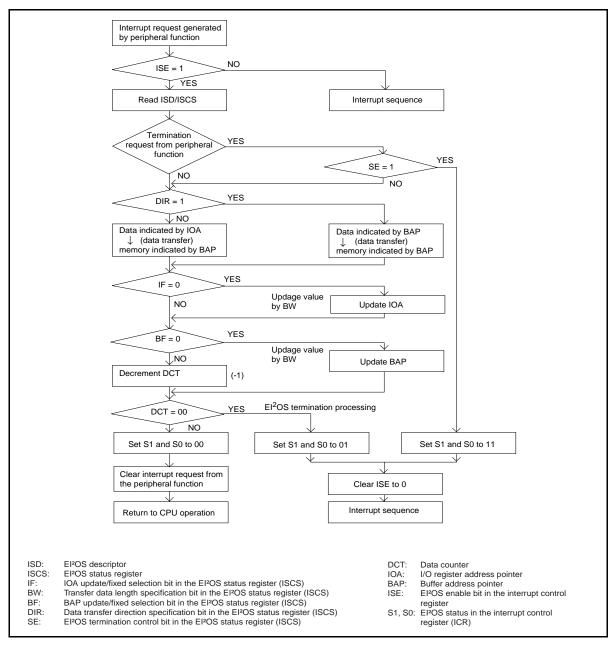

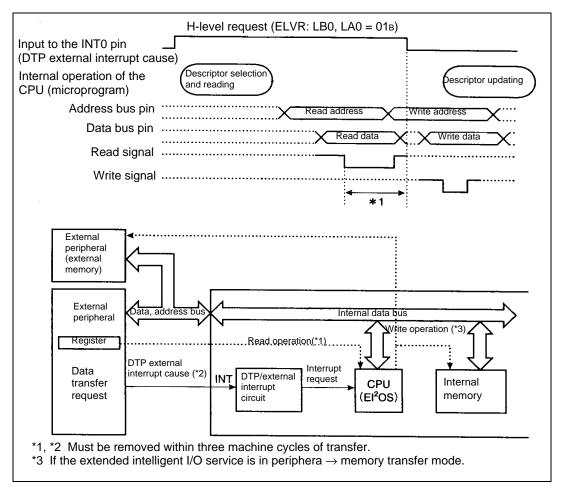

| Figure 6.6-1                    | Extended intelligent I/O service (EI2OS) operation                             | 147       |

|---------------------------------|--------------------------------------------------------------------------------|-----------|

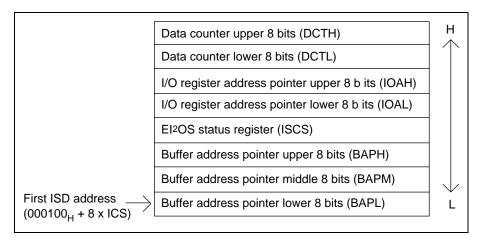

| Figure 6.6-2                    | Configuration of EI2OS descriptor (ISD)                                        | 148       |

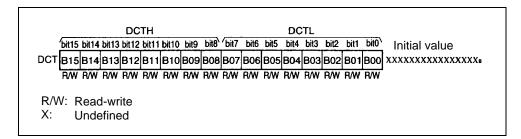

| Figure 6.6-3                    | Configuration of DCT                                                           | 150       |

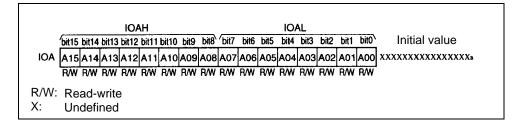

| Figure 6.6-4                    | Configuration of I/O register address pointer (IOA)                            | 150       |

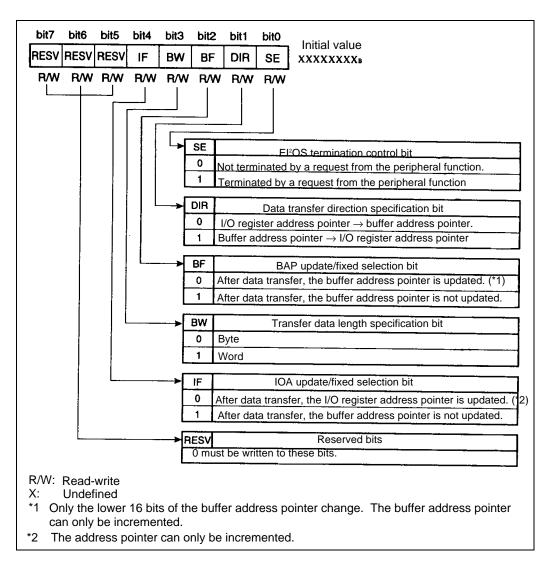

| Figure 6.6-5                    | Configuration of EI2OS status register (ISCS)                                  | 151       |

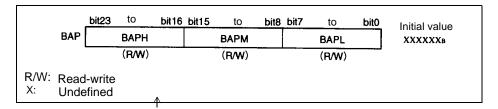

| Figure 6.6-6                    | Configuration of buffer address pointer (BAP)                                  | 152       |

| Figure 6.7-1                    | Flow of extended intelligent I/O service (EI2OS) operation                     | 154       |

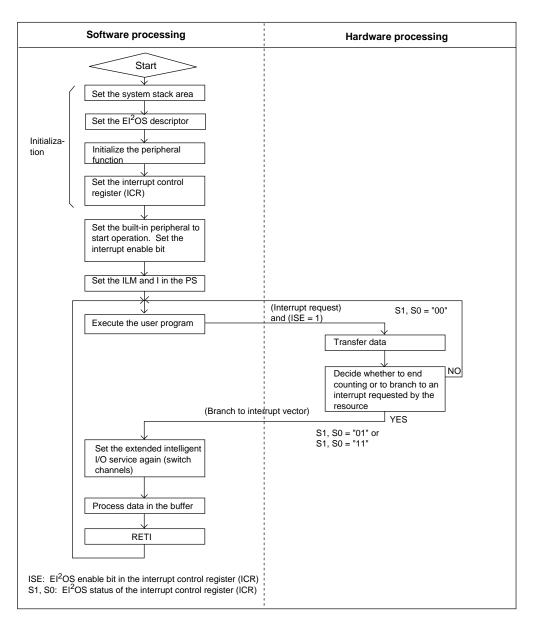

| Figure 6.7-1                    | Procedure for using the extended intelligent I/O service (EI2OS)               | 155       |

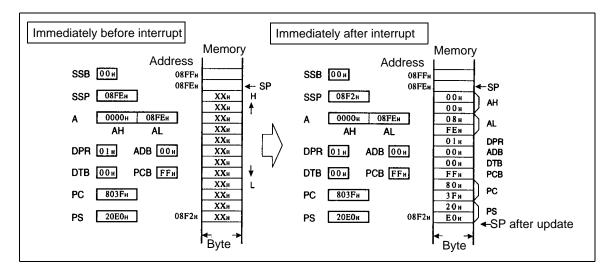

| Figure 6.9-1                    | Stack operations at the start of interrupt processing                          | 160       |

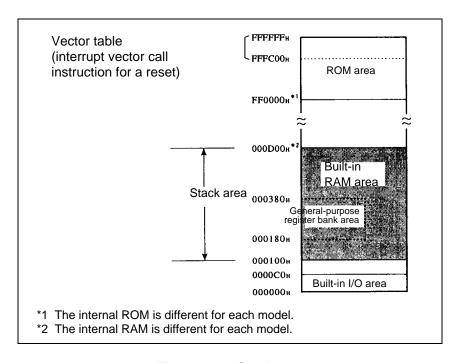

| Figure 6.9-2                    | Stack area                                                                     | 161       |

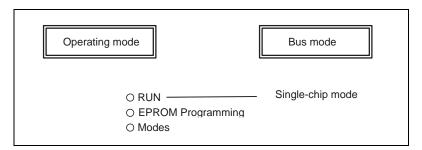

| Figure 7.1-1                    | Mode classification                                                            | 168       |

| Figure 7.3-1                    | Mode data configuration                                                        | 170       |

| Figure 7.3-2                    | Correspondence between access areas and physical addresses in single-chip mode | 171       |

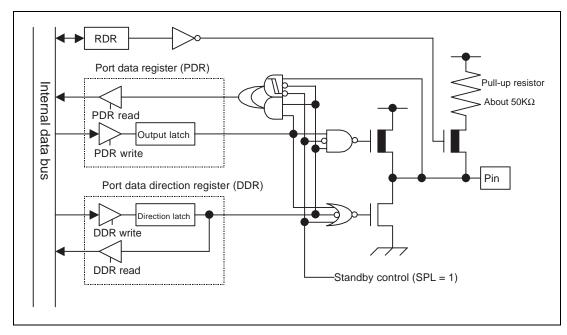

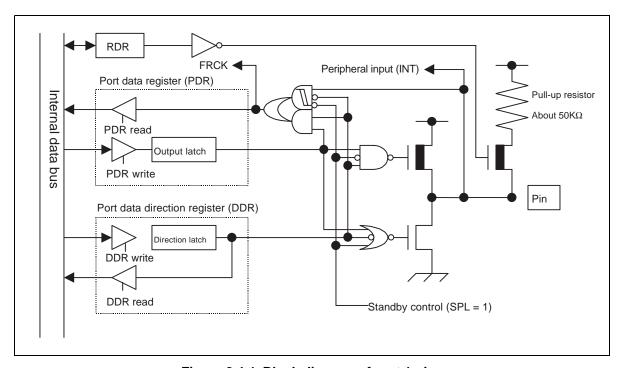

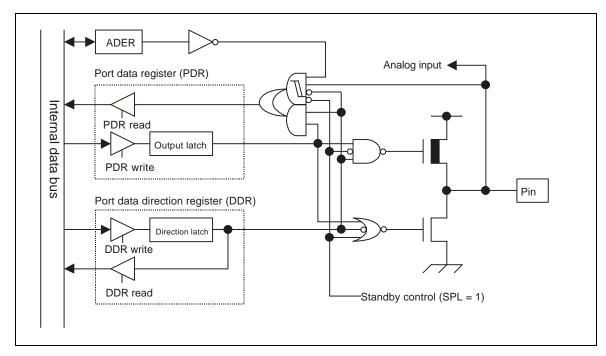

| Figure 8.3-1                    | Block diagram of port 0 pins                                                   | 177       |

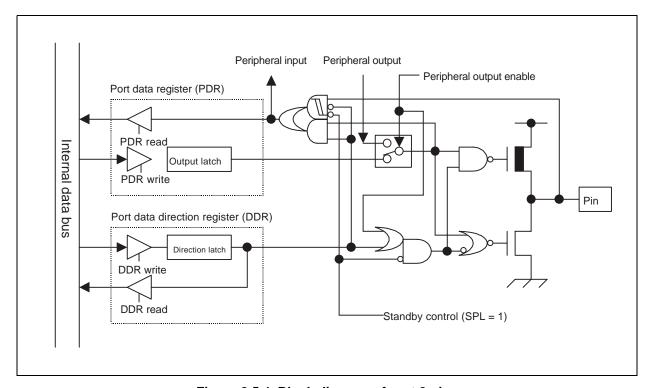

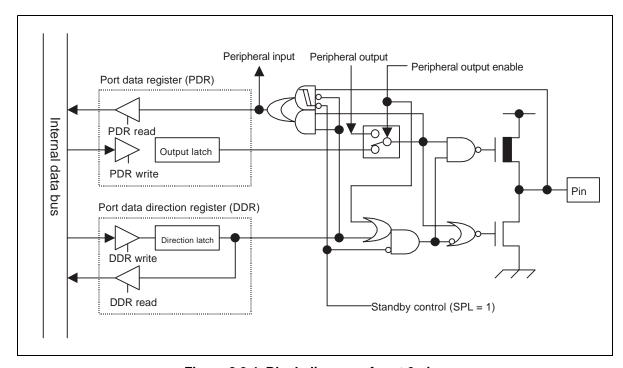

| Figure 8.4-1                    | Block diagram of port 1 pins                                                   | 183       |

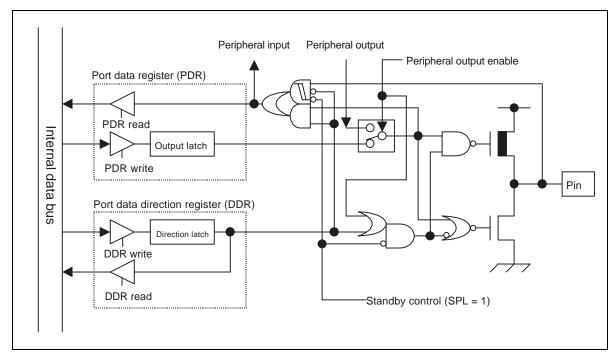

| Figure 8.5-1                    | Block diagram of port 2 pins                                                   | 189       |

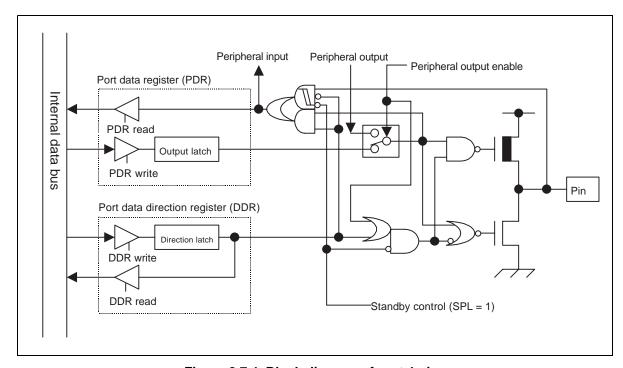

| Figure 8.6-1                    | Block diagram of port 3 pins                                                   | 195       |

| Figure 8.7-1                    | Block diagram of port 4 pins                                                   | 201       |

| Figure 8.8-1                    | Block diagram of port 5 pins                                                   | 207       |

| Figure 8.9-1                    | Block diagram of port 6 pins                                                   | 213       |

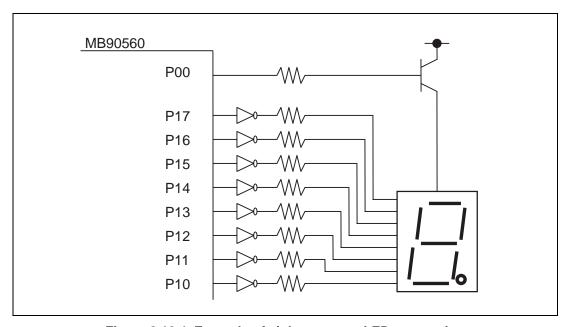

| Figure 8.10-1                   | Example of eight-segment LED connection                                        | 218       |

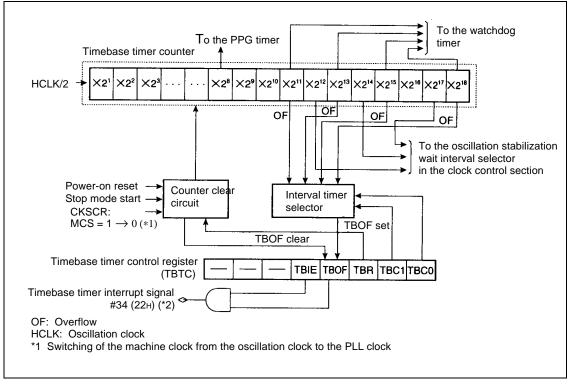

| Figure 9.2-1                    | Block diagram of the timebase timer                                            | 224       |

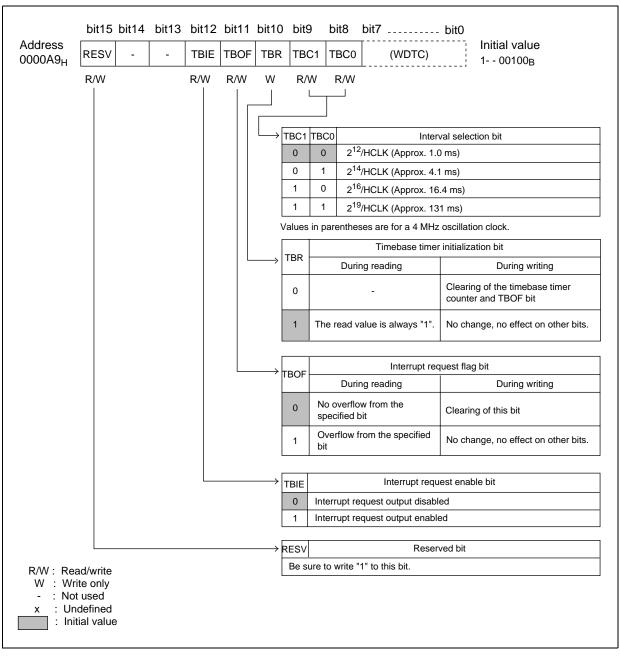

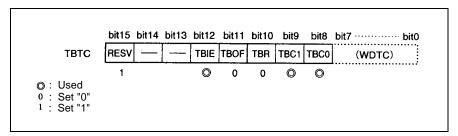

| Figure 9.3-1                    | Timebase timer control register (TBTC)                                         | 226       |

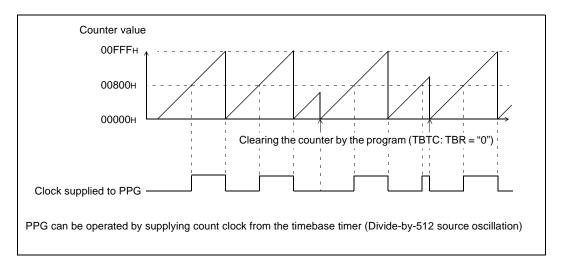

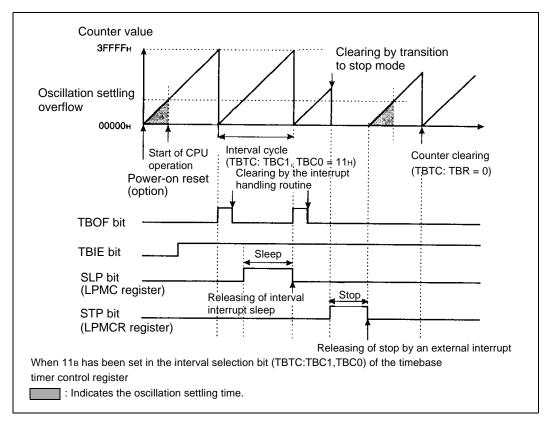

| Figure 9.5-1                    | Setting of the timebase timer                                                  | 230       |

| Figure 9.6-1                    | Effect on PPG when clearing timebase timer                                     | 232       |

| Figure 9.6-2                    | Timebase timer operations                                                      | 233       |

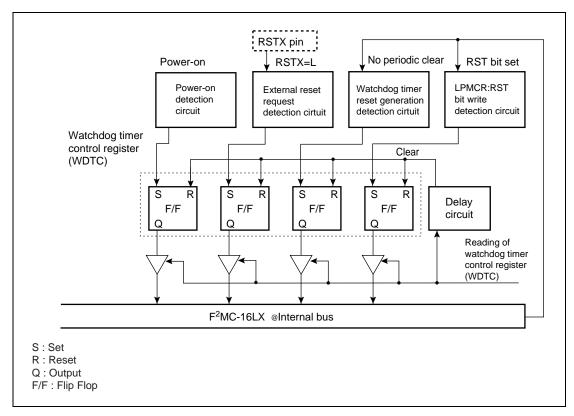

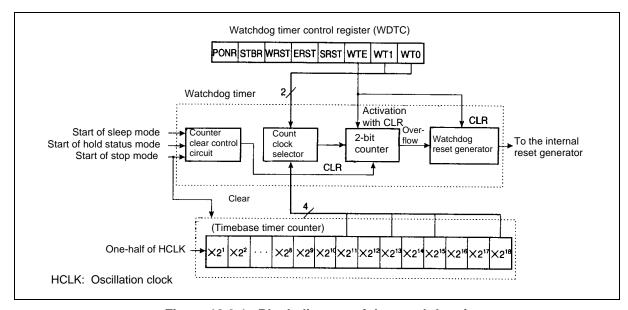

| Figure 10.2-1                   | Block diagram of the watchdog timer                                            | 239       |

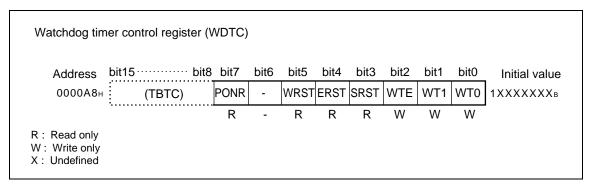

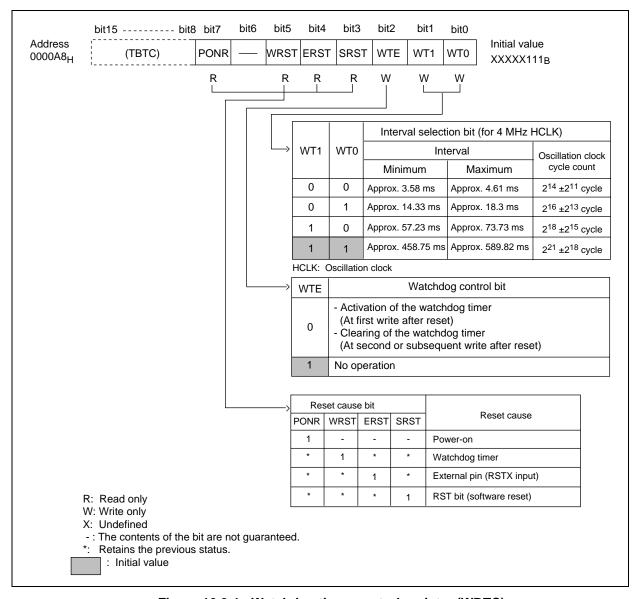

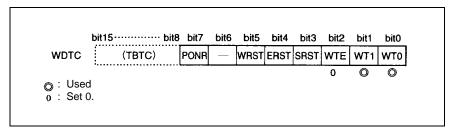

| Figure 10.3-1                   | Watchdog timer control register (WDTC)                                         | 240       |

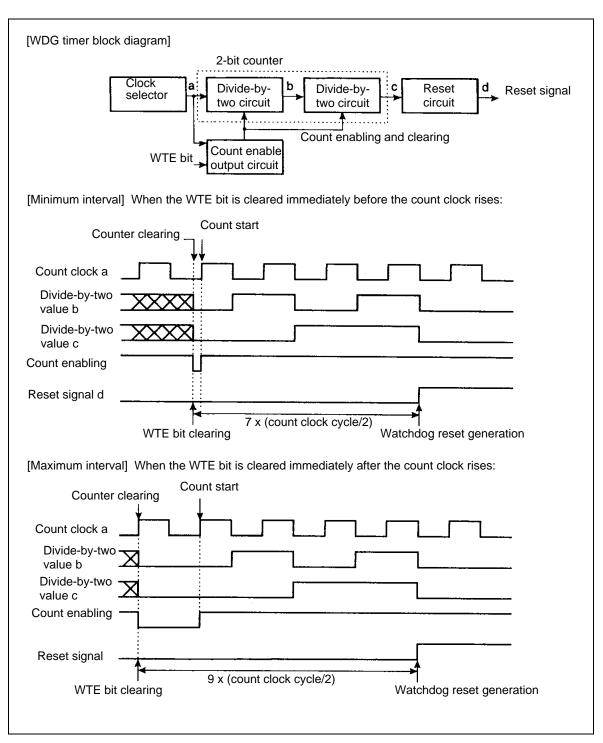

| Figure 10.4-1                   | Setting of the watchdog timer                                                  | 242       |

| Figure 10.4-2                   | Clear timing and watchdog timer intervals                                      | 243       |

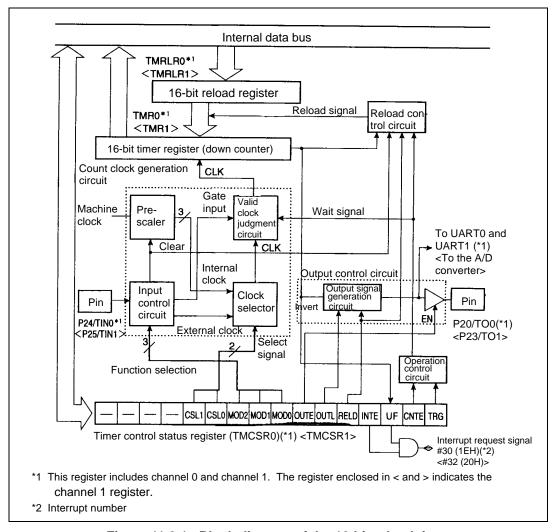

| Figure 11.2-1                   | Block diagram of the 16-bit reload timer                                       | 252       |

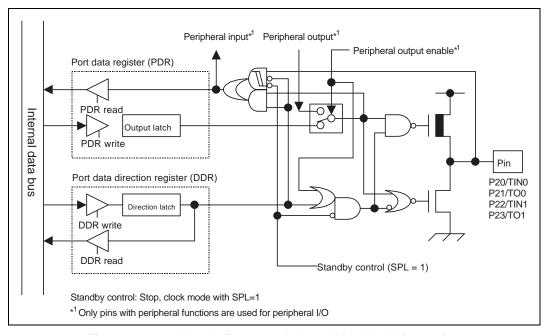

| Figure 11.3-1                   | Block diagram of the 16-bit reload timer pins                                  | 254       |

| Figure 11.4-1                   | 16-bit reload timer registers                                                  | 255       |

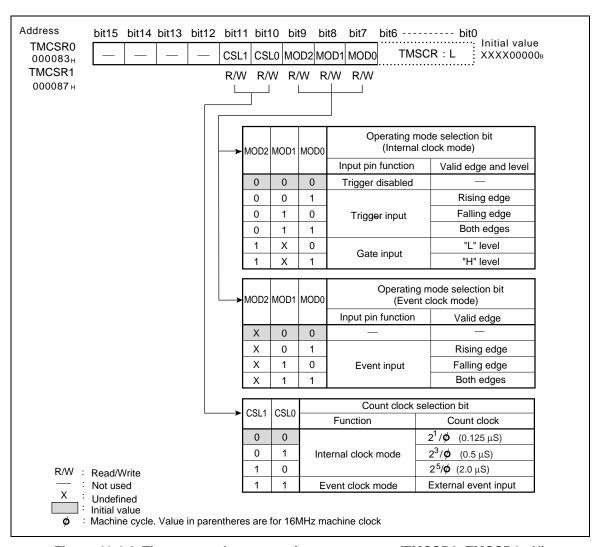

| Figure 11.4-2                   | Timer control status register, upper part (TMCSR0, TMCSR1: H)                  | 256       |

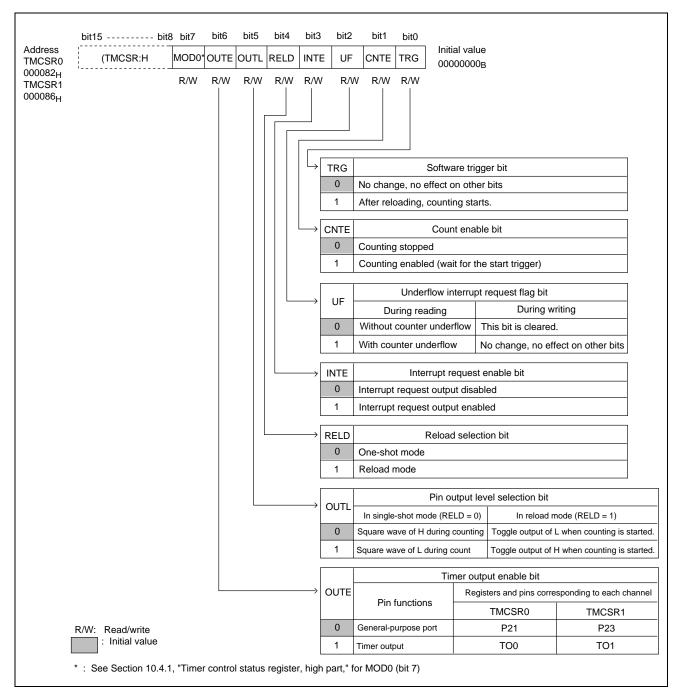

| Figure 11.4-3                   | Timer control status register, low part (TMCSR0, TMCSR1: L)                    | 258       |

| Figure 11.4-4                   | 16-bit timer register (TMR0, TMR1)                                             | 260       |

| Figure 11.4-5                   | 16-bit reload register (TMRLR0, TMRLR1)                                        | 261       |

| Figure 11.6-1<br>MB90560 series | Internal clock mode setting                                                    | 264<br>xi |

| Figure 11.6-2     | Event counter mode setting                                                      | 264 |

|-------------------|---------------------------------------------------------------------------------|-----|

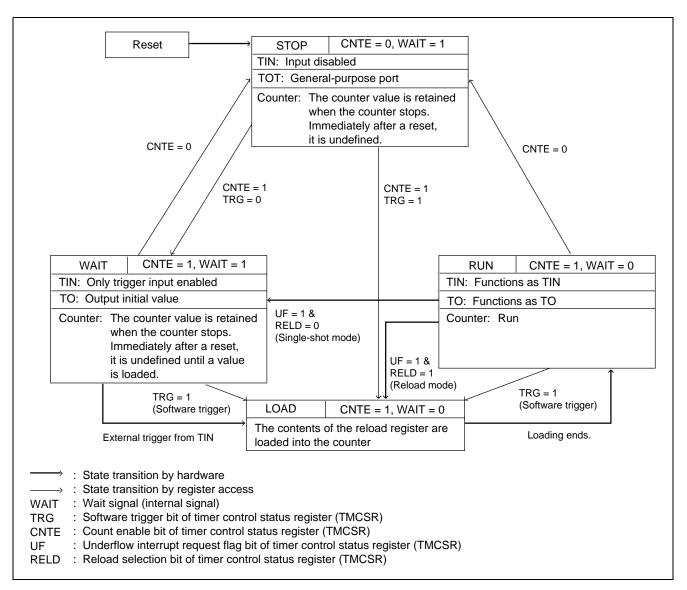

| Figure 11.6-3     | Counter status transition                                                       | 265 |

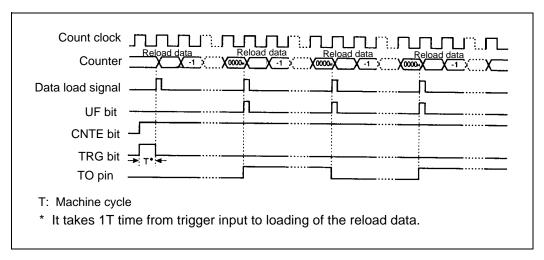

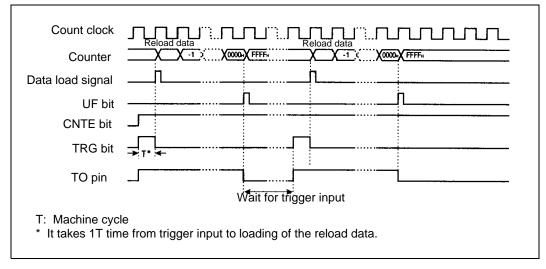

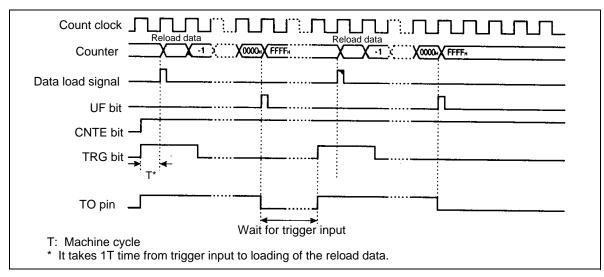

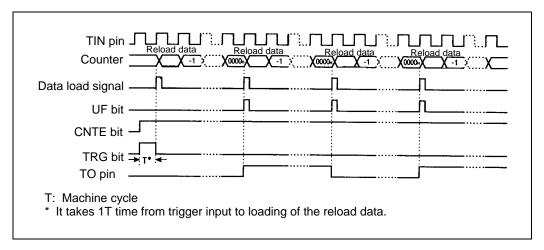

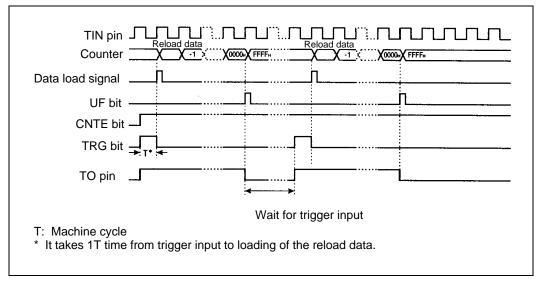

| Figure 11.6-4     | Count operation in reload mode (software trigger operation)                     | 266 |

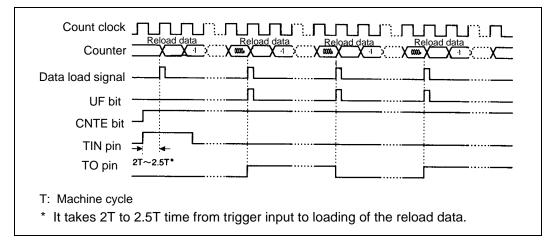

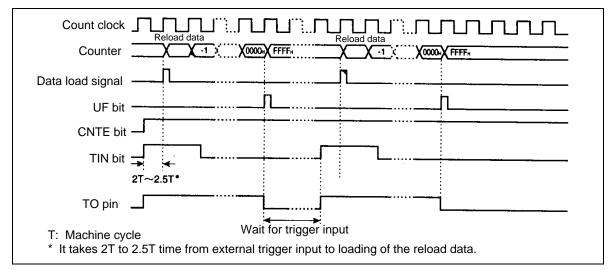

| Figure 11.6-5     | Counting in reload mode (external trigger operation)                            | 267 |

| Figure 11.6-6     | Count operation in reload mode (software trigger and gate input operation)      | 267 |

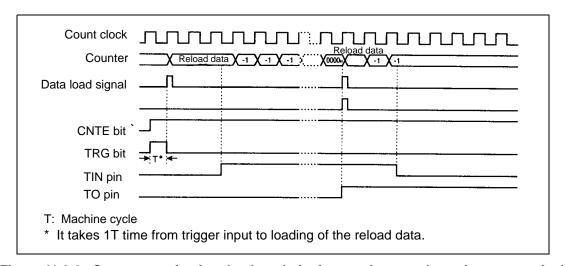

| Figure 11.6-7     | Count operation in single-shot mode (software trigger operation)                | 268 |

| Figure 11.6-8     | Count operation in single-shot mode (external trigger operation)                | 269 |

| Figure 11.6-9     | Count operation in single-shot mode (software trigger and gate input operation) | 269 |

| Figure 11.6-10    | Count operation in reload mode (event count mode)                               | 270 |

| Figure 11.6-11    | Counter operation in single-shot mode (event count mode)                        | 271 |

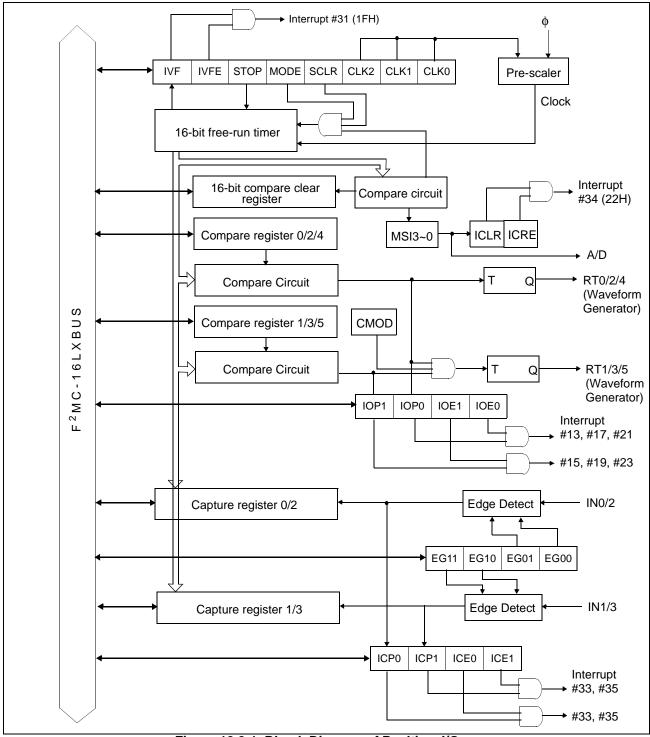

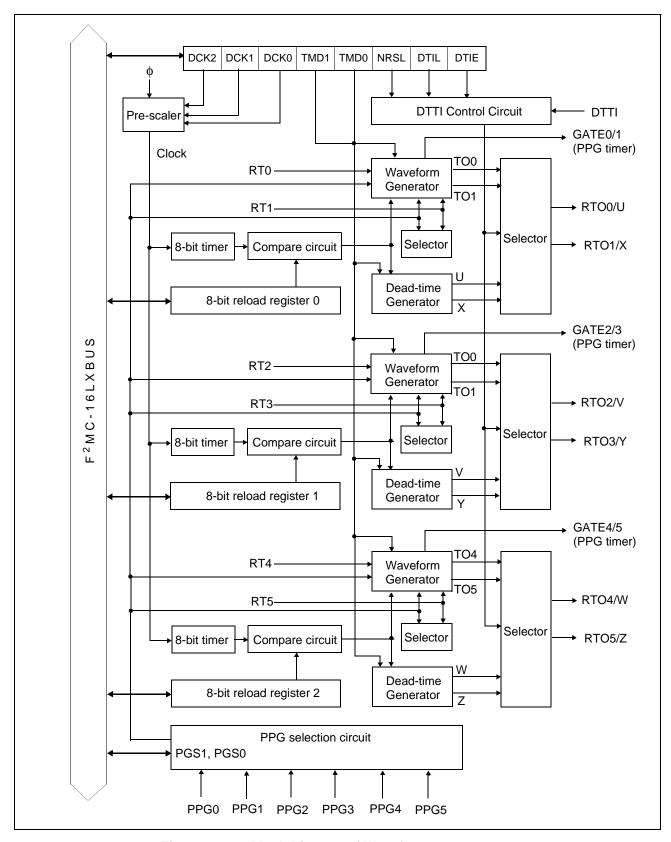

| Figure 12.2-1     | BLock Diagram of Realtime I/O                                                   | 280 |

| Figure 12.2-2     | Block Diagram of 8/16-bit PPG Timer                                             | 281 |

| Figure 12.2-3     | Block Diagram of Waveform Generator                                             | 282 |

| Figure 12.3-1     | Registers of 16-bit Free-Run Timer                                              | 284 |

| Figure 12.3-2     | Registers of Output Compare                                                     | 285 |

| Figure 12.3-3     | Registers of 16-bit Input Capture                                               | 286 |

| Figure 12.3-4     | Registers of 8/16-bit PPG Timers                                                | 287 |

| Figure 12.3-5     | Registers of Waveform Generator                                                 | 288 |

| Figure 12.3.1-1   | Registers of 16-bit Free-Run Timer                                              | 290 |

| Figure 12.3.1.1-  | 1Compare Clear Register (CPCR)                                                  | 291 |

| Figure 12.3.1.2-  | 1Timer Data Register                                                            | 292 |

| Figure 12.3.1.3-  | 1Timer Control Status Register (Upper)                                          | 294 |

| Figure 12.3.1.3-2 | 2Timer Control Status Register (Lower)                                          | 296 |

| Figure 12.3.2-1   | Registers of Output Compare                                                     | 298 |

| Figure 12.3.2.1-  | 1Compare Registers (OCCP0~5)                                                    | 299 |

| Figure 12.3.2.2-  | 1 Compare Control Register (Upper, OSC1/3/5)                                    | 300 |

| Figure 12.3.2.2-2 | 2Compare Control Register (Lower, OSC0/2/4)                                     | 302 |

| Figure 12.3.3-1   | Registers of 16-bit Input Capture                                               | 304 |

| Figure 12.3.3.1-  | 1 Input Capture Registers (IPCP0~3)                                             | 305 |

| Figure 12.3.3.2-  | 1 Capture Control Register (ICS23)                                              | 306 |

| Figure 12.3.3.2-2 | 2Capture Control Register (ICS01)                                               | 308 |

| Figure 12.3.4-1   | Registers of 8/16-bit PPG Timers                                                | 310 |

| Figure 12.3.4.1-  | 1PPG Reload Register (PRLH0~5, PRLL0~5)                                         | 311 |

| Figure 12.3.4.2-  | 1PPG1/3/5 Control Register (PPGC1/3/5)                                          | 312 |

| Figure 12.3.4.2-2 | 2PPG0/2/4 Control Register (PPGC0/2/4)                                          | 314 |

| Figure 12.3.4.3-  | 1PPG0/1/2/3/4/5 Clock Control Register (PCD01/23/45)                            | 316 |

| Figure 12.3.5-1   | Registers of Waveform Generator                                                 | 318 |

| Figure 12.3.5.1-  | 18-bit Reload Registers (TMRR0/1/2)                                             | 319 |

|   | Figure 12.3.5.2-  | 18-bit Timer Control Register (DTCR0/1/2)                                                                 | 320  |

|---|-------------------|-----------------------------------------------------------------------------------------------------------|------|

|   | Figure 12.3.5.3-  | 1Waveform Control Register (SIGCR)                                                                        | 322  |

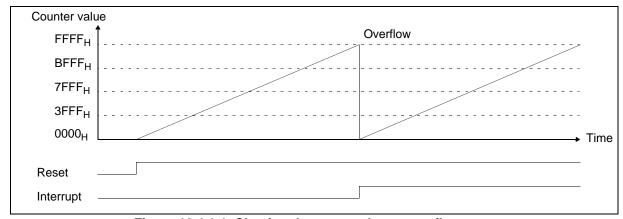

|   | Figure 12.4.1-1   | Clearing the counter by an overflow                                                                       | 326  |

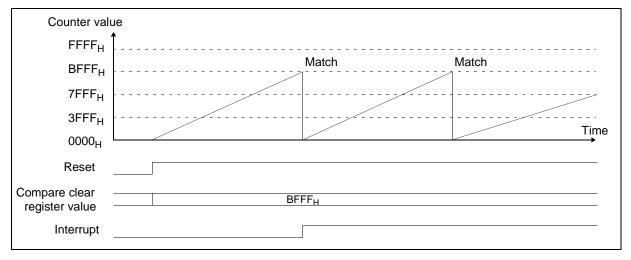

|   | Figure 12.4.1-2   | Clearing the counter upon a match with compare clear register                                             | 326  |

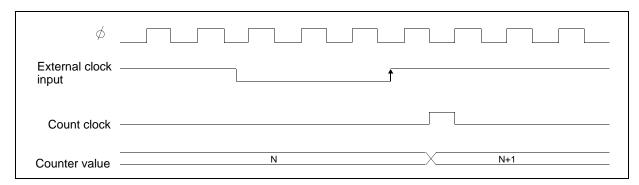

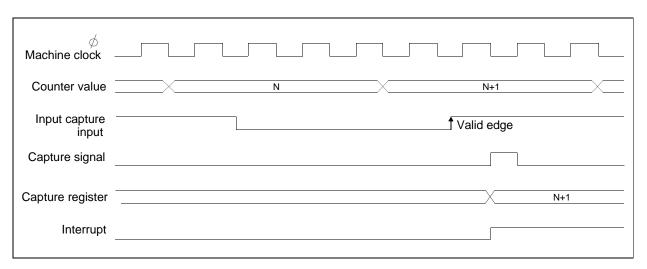

|   | Figure 12.4.1-3   | 16-bit Free-run timer count timing                                                                        | 327  |

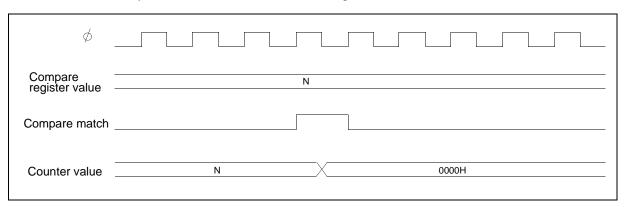

|   | Figure 12.4.1-4   | 16-bit Free-run timer clear timing                                                                        | 327  |

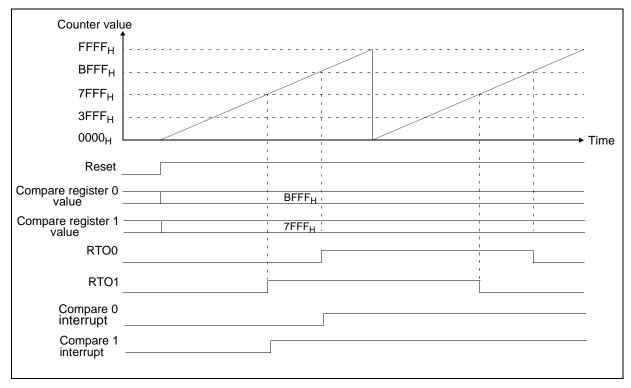

|   | Figure 12.4.2-1   | Sample output waveform when compare registers 0 and 1 are used individually when the output value is "0". |      |

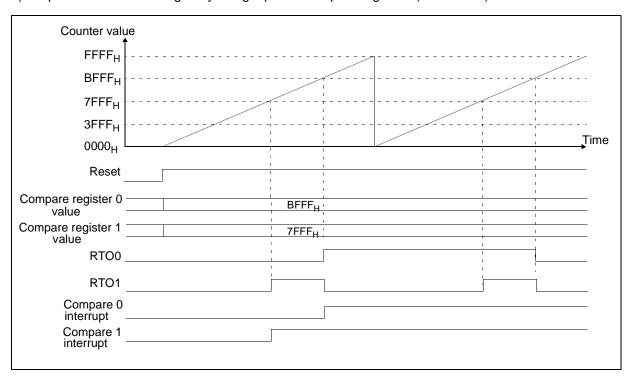

|   | Figure 12.4.2-2   | Sample output waveform when compare registers 0 and 1 are used in a pair when the in output value is "0". |      |

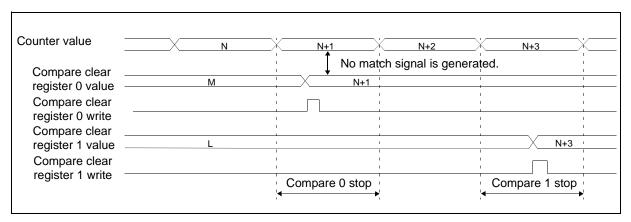

|   | Figure 12.4.2-3   | Compare operation upon update of compare registers                                                        | 330  |

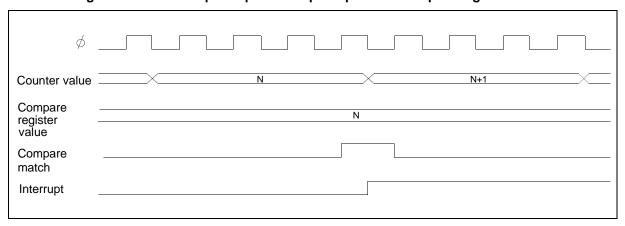

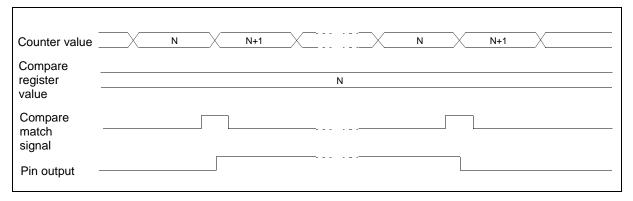

|   | Figure 12.4.2-4   | Compare interrupt timing                                                                                  | 330  |

|   | Figure 12.4.2-5   | Output pin change timing                                                                                  | 330  |

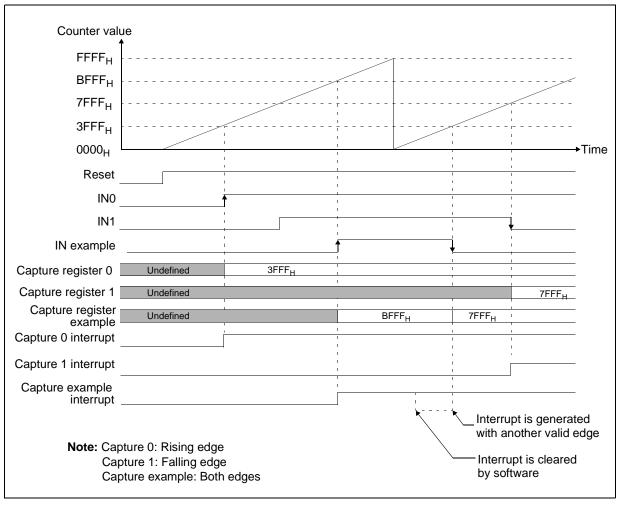

|   | Figure 12.4.3-1   | Sample input capture timing                                                                               | 332  |

|   | Figure 12.4.3-2   | 16-bit input capture timing for input signals                                                             | 333  |

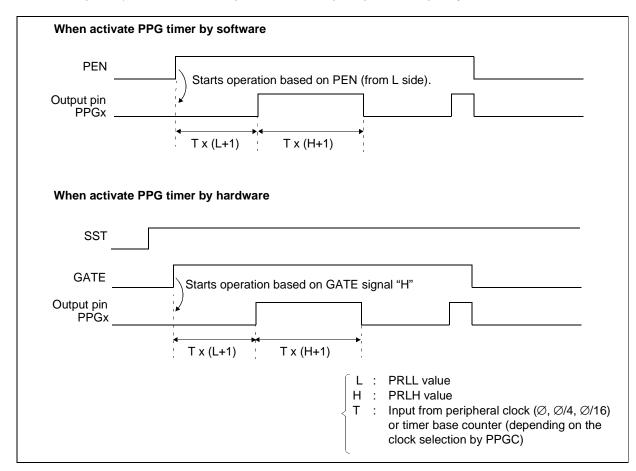

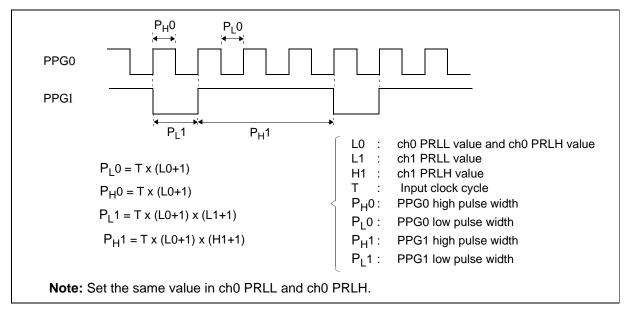

|   | Figure 12.4.4-1   | PPG output operation, output waveform                                                                     | 335  |

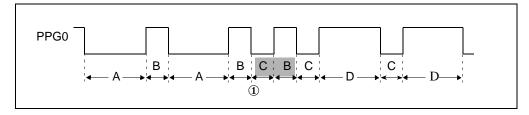

|   | Figure 12.4.4-2   | 8+8 PPG output operation waveform                                                                         | 337  |

|   | Figure 12.4.4-3   | Write timing chart                                                                                        | 338  |

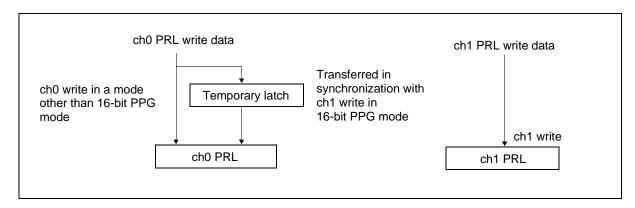

|   | Figure 12.4.4-4   | PRL write operation block diagram                                                                         | 338  |

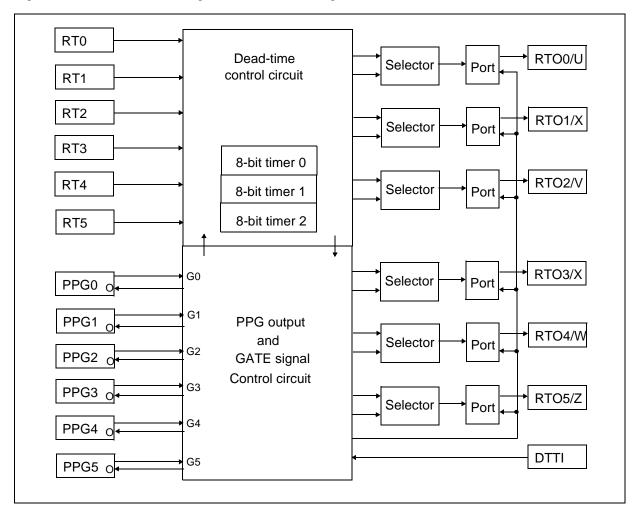

|   | Figure 12.4.5-1   | Waveform Generator                                                                                        | 340  |

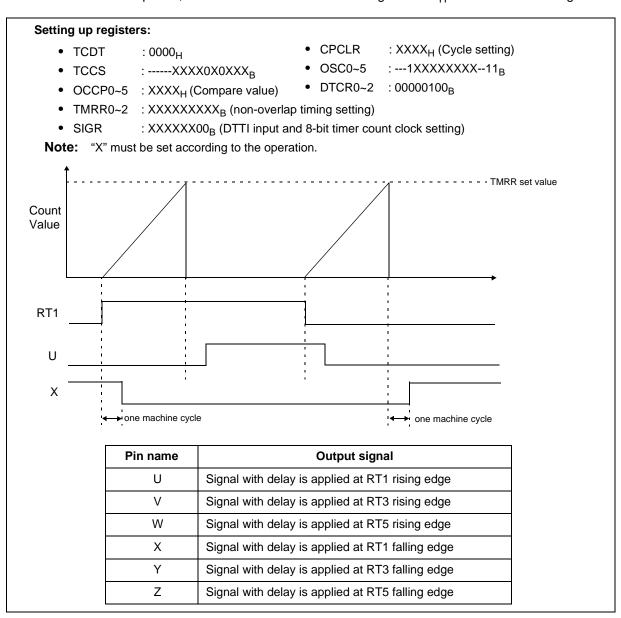

|   | Figure 12.4.5.1-  | 1 Positive Polarity Non-overlap Signal Generation by RT1/3/5                                              | 342  |

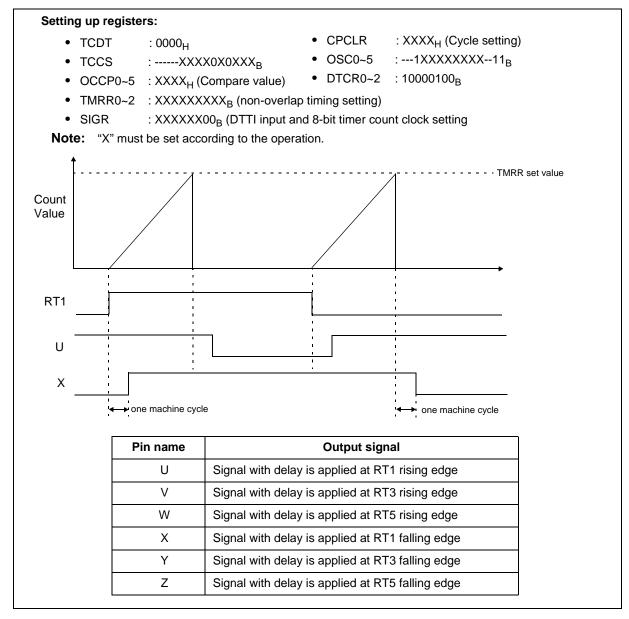

|   | Figure 12.4.5.1-2 | 2Negative Polarity Non-overlap Signal Generation by RT1/3/5                                               | 343  |

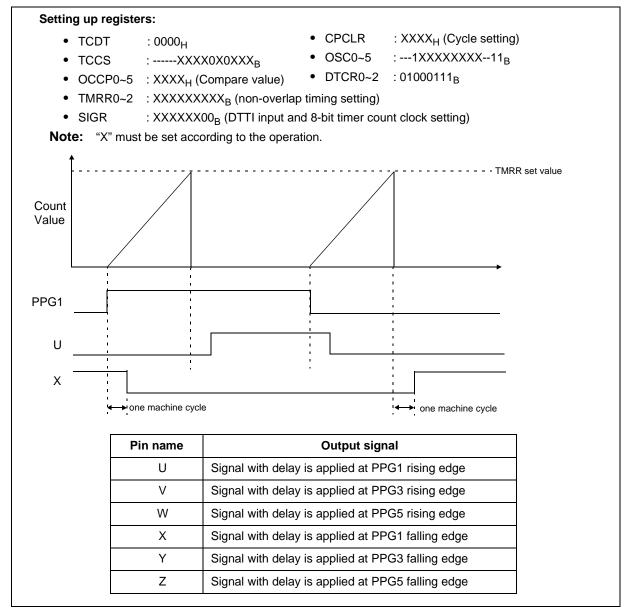

|   | Figure 12.4.5.1-3 | 3Positive Polarity Non-overlap Signal Generation by PPG timer                                             | 344  |

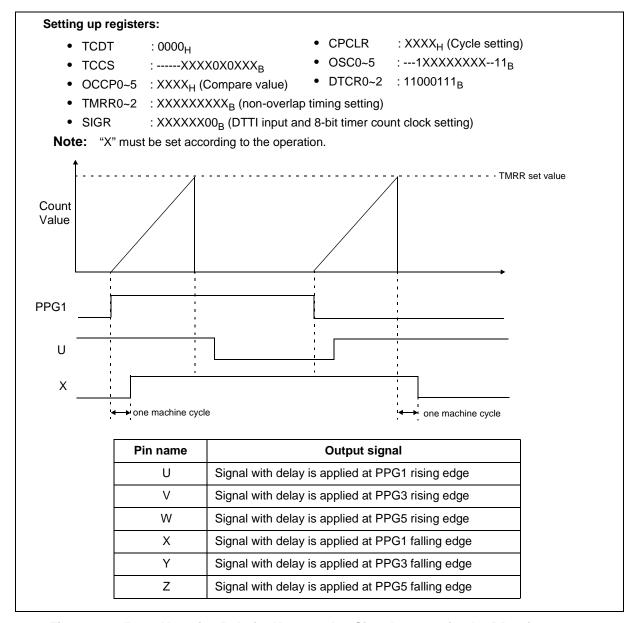

|   | Figure 12.4.5.1-  | 4Negative Polarity Non-overlap Signal Generation by PPG timer                                             | 345  |

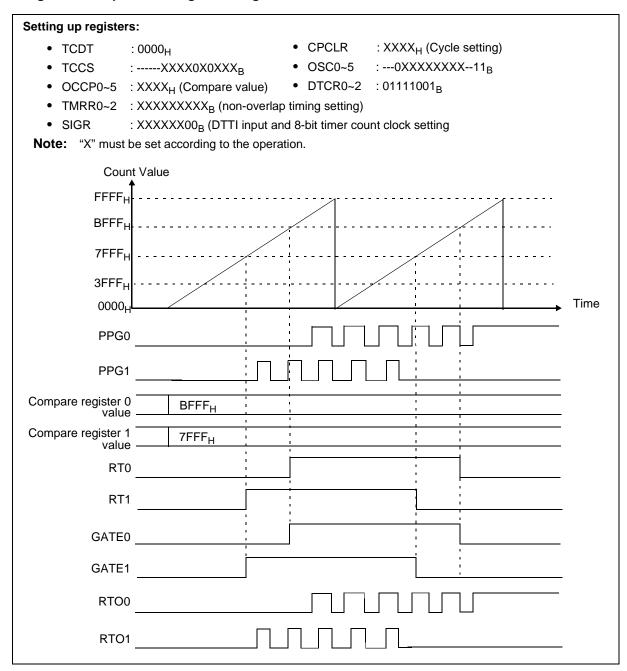

|   | Figure 12.4.5.2-  | 1Generating PPG output/GATE signal during each RT is at "H" level                                         | 346  |

|   | Figure 12.4.5.2-2 | 2Generating PPG output/GATE signal until the value 8-bit timer and 8-bit reload register is matched.      |      |

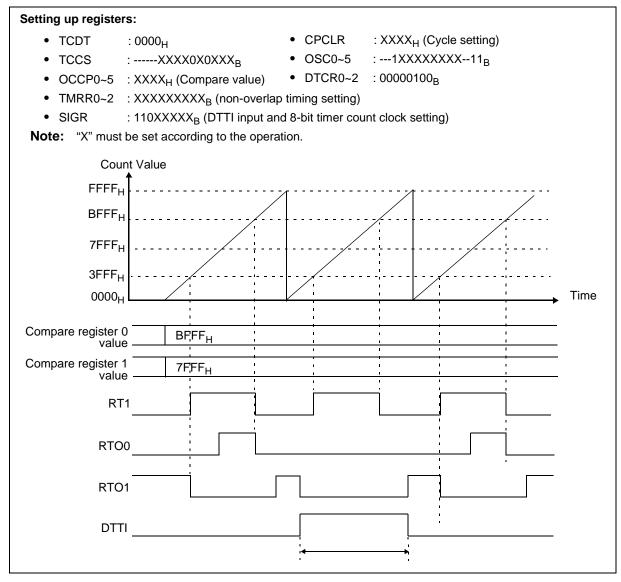

|   | Figure 12.4.5.3-  | 1Operation when DTTI input is enabled                                                                     | 348  |

|   | Figure 13.1-1     | UART operation mode                                                                                       | 353  |

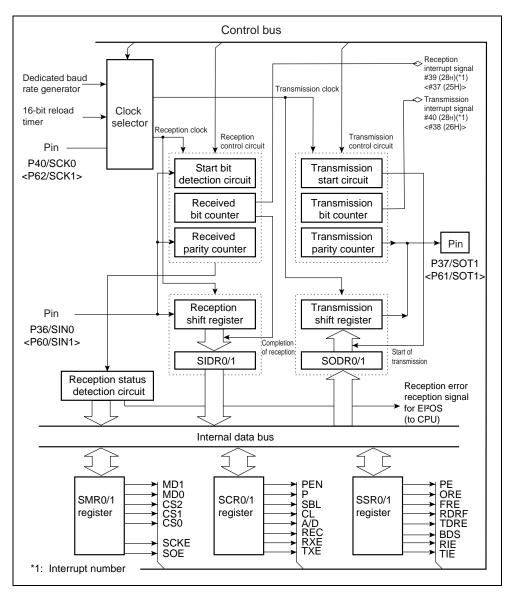

|   | Figure 13.2-1     | Block diagram of UART                                                                                     | 354  |

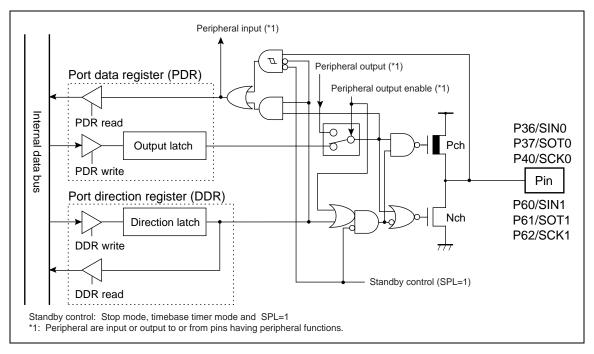

|   | Figure 13.3-1     | Block Diagram of UART Pins                                                                                | 359  |

|   | Figure 13.4-1     | UART registers                                                                                            | 360  |

|   | Figure 13.4-2     | Serial Control register (SCR0/1)                                                                          | 362  |

|   | Figure 13.4-3     | Serial Mode control register (SMR0/1)                                                                     | 364  |

|   | Figure 13.4-4     | Status register (SSR0/1)                                                                                  | 366  |

|   | Figure 13.4-5     | Serial input data register (SIDR0/1)                                                                      | 368  |

|   | Figure 13.4-6     | Output data register (SODR0/1)                                                                            | 368  |

|   | Figure 13.5-1     | Reception operation and flag set timing                                                                   | 374  |

|   | Figure 13.5-2     | Transmission operation and flag set timing                                                                | 375  |

| ١ | /IB90560 series   |                                                                                                           | xiii |

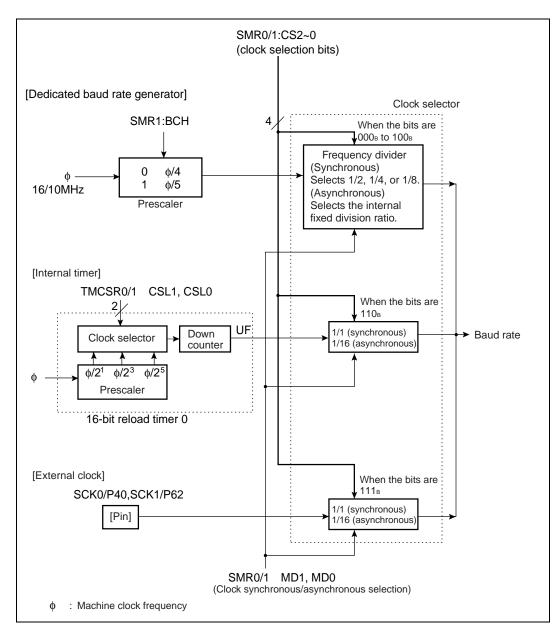

| Figure 13.6-1 | baud rate selection circuit                                                                         | 377   |

|---------------|-----------------------------------------------------------------------------------------------------|-------|

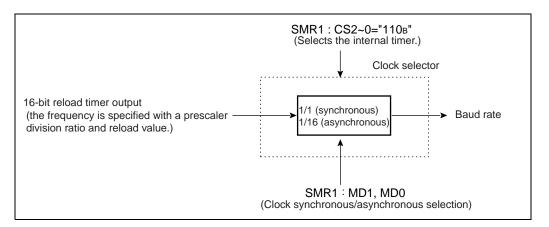

| Figure 13.6-2 | Baud rate selection circuit for the internal timer (16-bit reload timer 0)                          | . 382 |

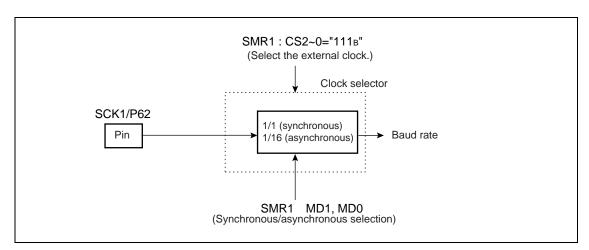

| Figure 13.6-3 | Baud rate selection circuit for the external clock                                                  | . 384 |

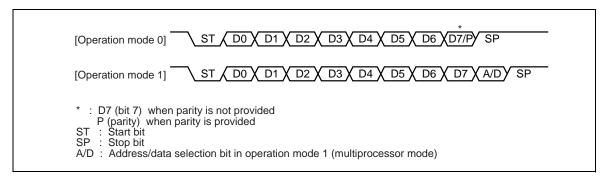

| Figure 13.7-1 | Transfer data format (operation modes 0 and 1)                                                      | . 388 |

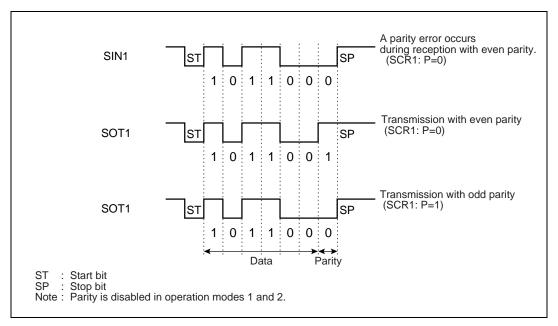

| Figure 13.7-2 | Transmission data when parity is enabled                                                            | . 389 |

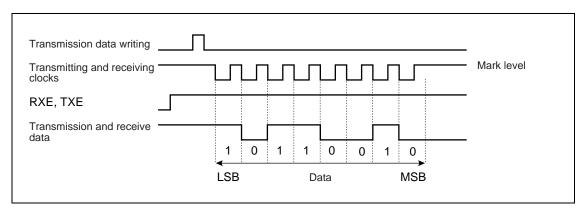

| Figure 13.7-3 | Transfer data format (operation mode 2)                                                             | . 390 |

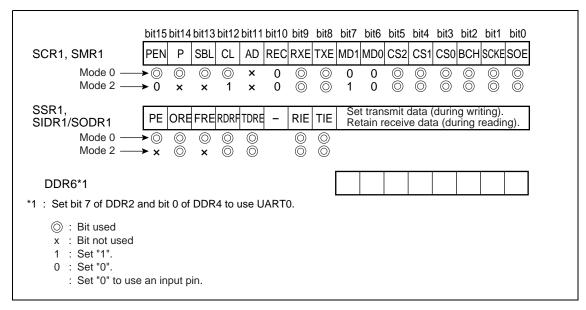

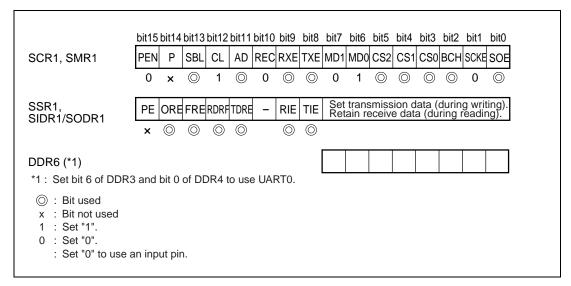

| Figure 13.7-4 | Settings for UART1 operation mode 0                                                                 | . 392 |

| Figure 13.7-5 | Connection example of UART1 bidirectional communication                                             | . 392 |

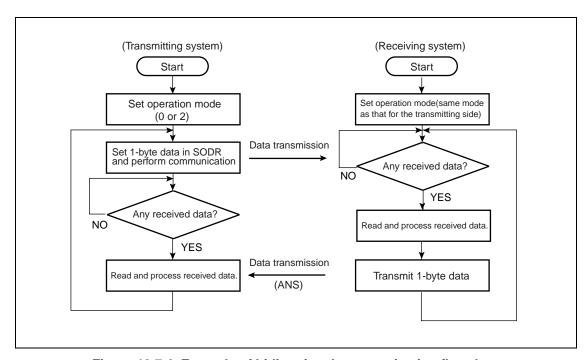

| Figure 13.7-6 | Example of bidirectional communication flowchart                                                    | . 393 |

| Figure 13.7-7 | Settings for UART operation mode 1                                                                  | . 394 |

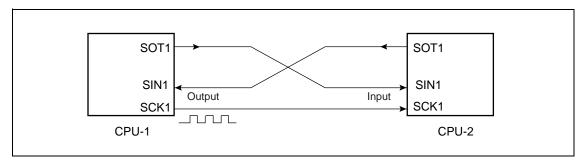

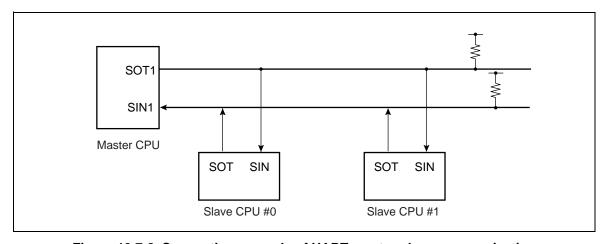

| Figure 13.7-8 | Connection example of UART master-slave communication                                               | . 394 |

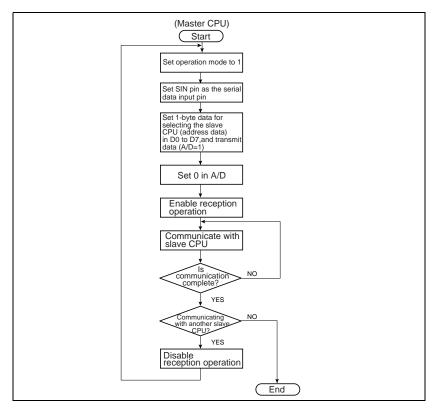

| Figure 13.7-9 | Master-slave communication flowchart                                                                | . 395 |

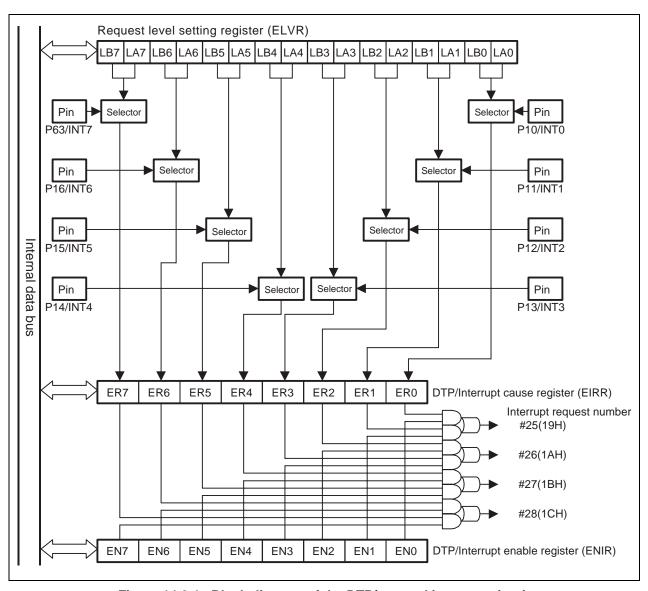

| Figure 14.2-1 | Block diagram of the DTP/external interrupt circuit                                                 | . 404 |

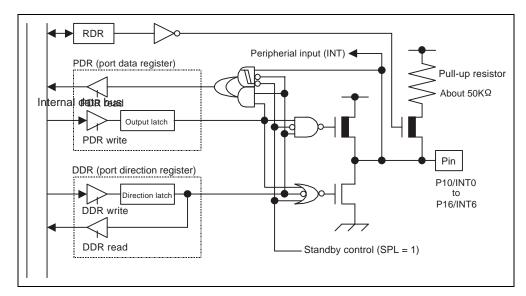

| Figure 14.3-1 | Block diagram of the DTP/external interrupt circuit pins (For P10/INT0 ~ P16/INT6 only)             | . 407 |

| Figure 14.3.2 | Block diagram of the DTP/external interrupt circuit pins (For P63/ INT7 only)                       | . 407 |

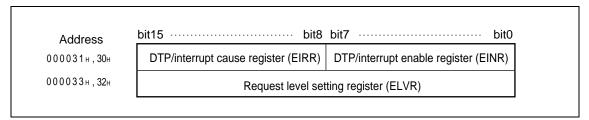

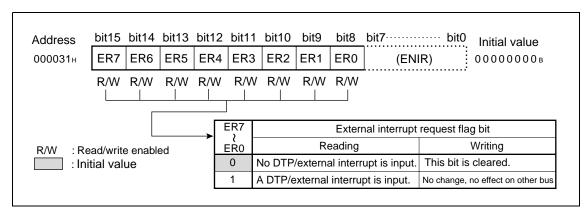

| Figure 14.4-2 | DTP/external interrupt circuit registers                                                            | . 408 |

| Figure 14.4-2 | DTP/interrupt cause register (EIRR)                                                                 | . 409 |

| Figure 14.4-3 | DTP/interrupt enable register (ENIR)                                                                | . 410 |

| Figure 14.4-4 | Request level setting register (ELVR)                                                               | . 412 |

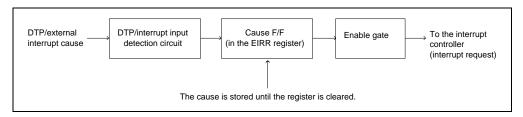

| Figure 14.5-1 | DTP/external interrupt circuit                                                                      | . 414 |

| Figure 14.5-2 | Operation of the DTP/external interrupt circuit                                                     | . 416 |

| Figure 14.5-3 | Example of interfacing to the external peripheral                                                   | . 418 |

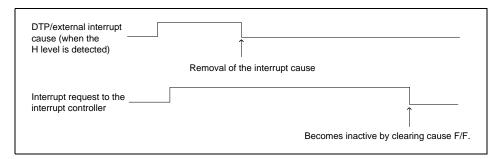

| Figure 14.6-1 | Clearing the cause retention circuit when a level is specified                                      | . 420 |

| Figure 14.6-2 | DTP/external interrupt cause and interrupt request when the output of interrupt requests is enabled | 420   |

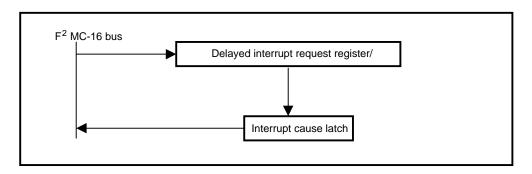

| Figure 15.1-1 | Block diagram of the delayed interrupt generator module                                             | . 428 |

| Figure 15.2-1 | Operation of the delayed interrupt generator module                                                 | . 429 |

| Figure 16.2-1 | Block diagram of the 8/10-bit A/D converter                                                         | . 434 |

| Figure 16.3-1 | Block diagram of the P50/AN0 to P57/AN7 pins                                                        | . 437 |

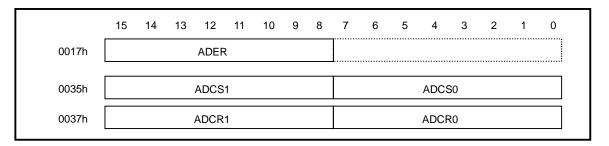

| Figure 16.4-1 | 8/10-bit A/D converter registers                                                                    | . 438 |

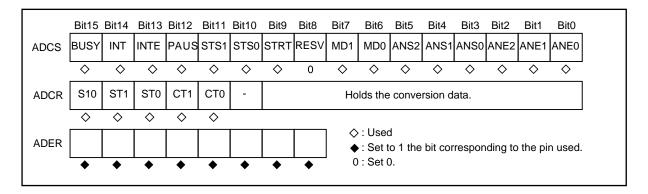

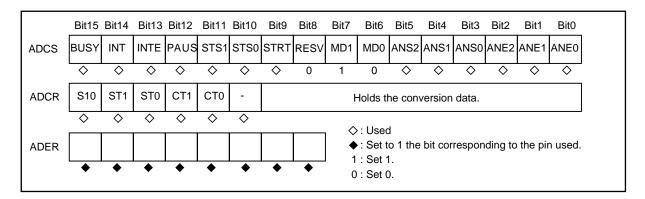

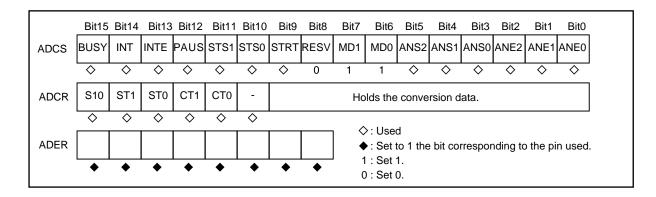

| Figure 16.4-2 | A/D control status register 1 (ADCS1)                                                               | . 439 |

| Figure 16.4-3 | A/D control status register 0 (ADCS0)                                                               | . 442 |

| Figure 16.4-4 | A/D data register (ADCR0, 1)                                                                        | . 444 |

| Figure 16.6-1 | Settings for single conversion mode                                                                 | . 447 |

| Figure 16.6-2 | Settings for continuous conversion mode                                                             | . 448 |

| Figure 16.6-3 | Settings for stop conversion mode                                                                   | . 449 |

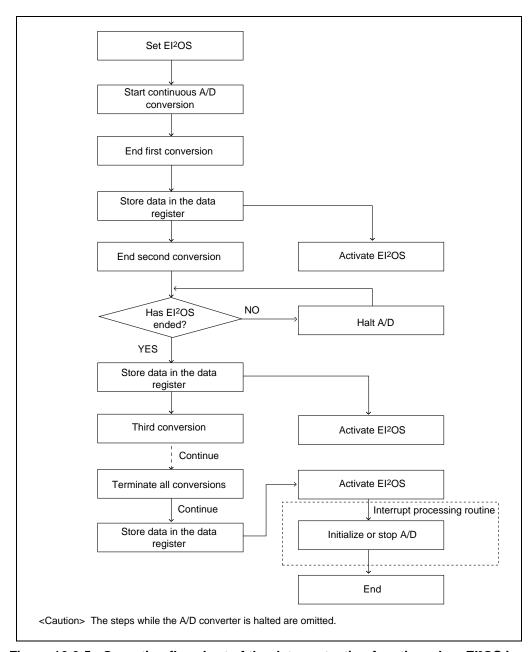

| Figure 16.6-4 | Sample operation flowchart when EI2OS is used                                                       | . 450 |

| Figure 16.6-5 | Operation flowchart of the data protection function when EI2OS is used                              | 453   |

xiv MB90560 series

| Figure 16.8-1  | Flowchart of program using EI2OS (single conversion mode)                                                 | 456 |

|----------------|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 16.9-1  | Flowchart of program using El <sup>2</sup> OS (continuous conversion mode)                                | 458 |

| Figure 16.10-1 | Flowchart of program using EI2OS (stop conversion mode)                                                   | 461 |

| Figure 17.1-1  | Block diagram                                                                                             | 466 |

| Figure 17.2-1  | System configuration example                                                                              | 469 |

| Figure 17.2-2  | System configuration example                                                                              | 470 |

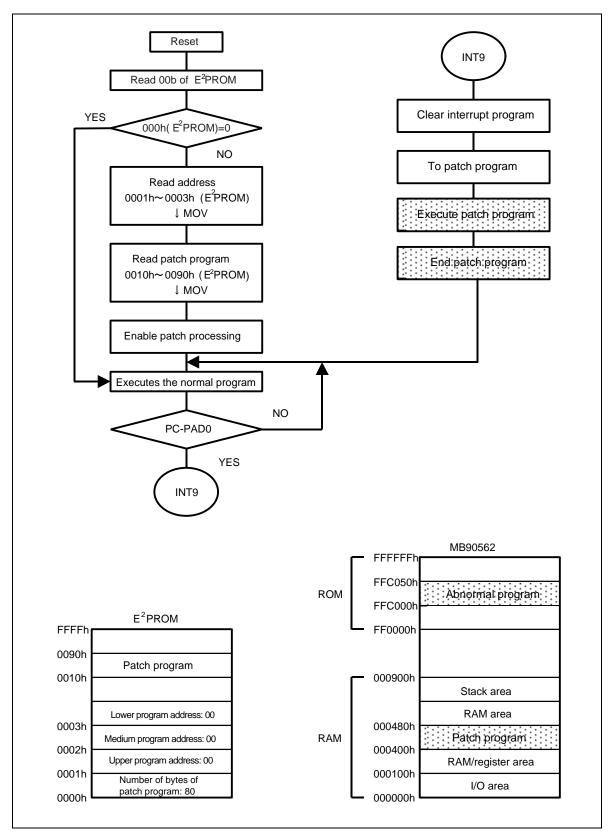

| Figure 17.2-3  | Flowchart of program patch processing                                                                     | 471 |

| Figure 18.1-1  | Block diagram                                                                                             | 474 |

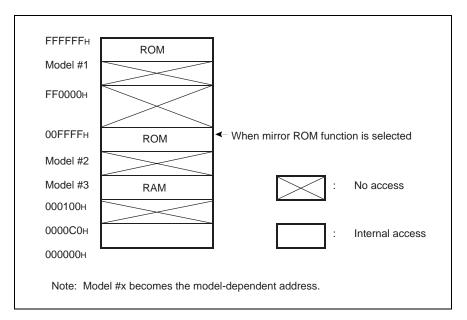

| Figure 18.1-2  | Memory space                                                                                              | 475 |

| Figure B.3-1   | Example of immediate addressing (#imm)                                                                    | 490 |

| Figure B.3-2   | Example of register direct addressing                                                                     | 491 |

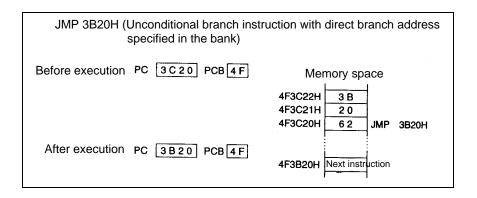

| Figure B.3-3   | Example of direct branch addressing (addr16)                                                              | 491 |

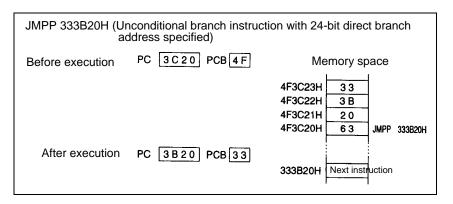

| Figure B.3-4   | Example of physical direct branch addressing (addr24)                                                     | 492 |

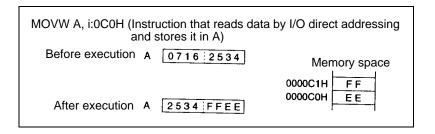

| Figure B.3-5   | Example of I/O direct addressing (io)                                                                     | 492 |

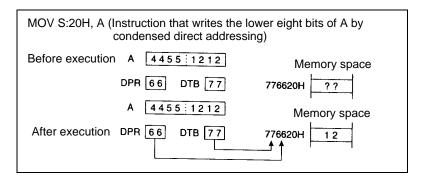

| Figure B.3-6   | Example of condensed direct addressing (dir)                                                              | 492 |

| Figure B.3-7   | Example of direct addressing (addr16)                                                                     | 493 |

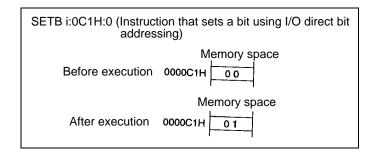

| Figure B.3-8   | Example of I/O direct bit addressing (io:bp)                                                              | 493 |

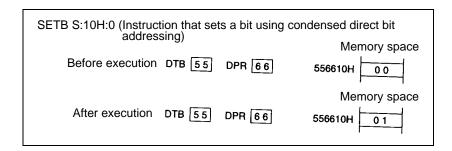

| Figure B.3-9   | Example of condensed direct bit addressing (dir:bp)                                                       | 494 |

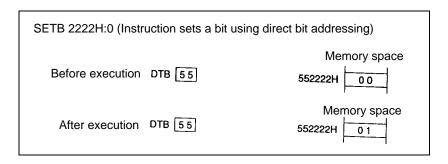

| Figure B.3-10  | Example of direct bit addressing (addr16:bp)                                                              | 494 |

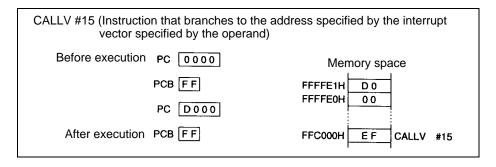

| Figure B.3-11  | Example of vector addressing (#vct)                                                                       | 494 |

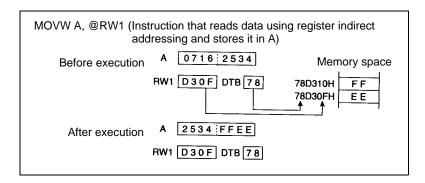

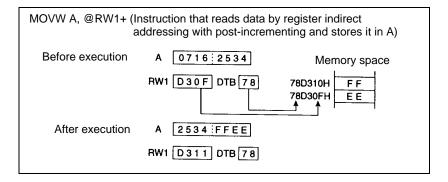

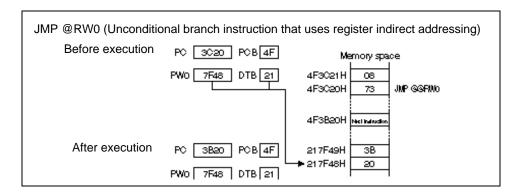

| Figure B.4-1   | Example of register indirect addressing (@RWj j = 0 to 3)                                                 | 496 |

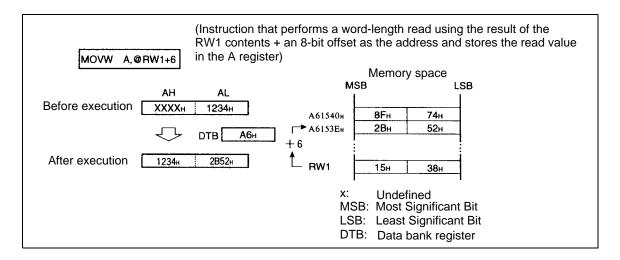

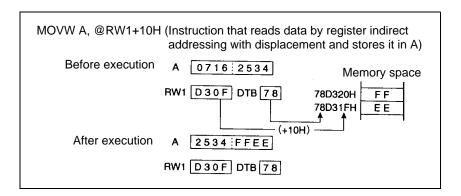

| Figure B.4-3   | Example of register indirect addressing with displacement (@RWi+disp8 i = 0 to 7, @RWj+disp16 j = 0 to 3) | 497 |

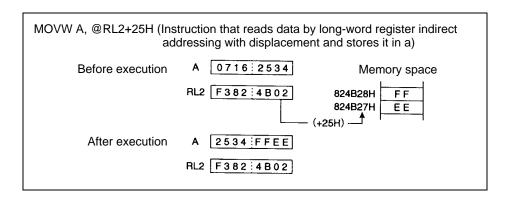

| Figure B.4-4   | Example of long-word register indirect addressing with displacement (@RLi+disp8 i = 0 to 3)               | 497 |

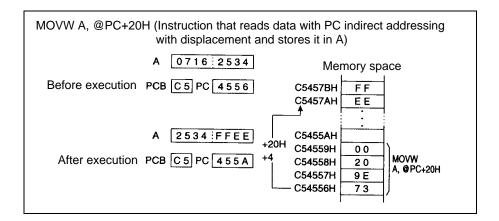

| Figure B.4-5   | Example of program counter indirect addressing with displacement (@PC+disp16)                             | 498 |

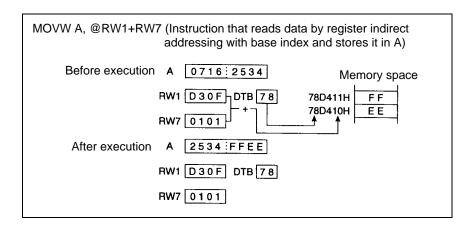

| Figure B.4-6   | Example of register indirect addressing with base index (@RW0+RW7, @RW1+RW7) .                            | 499 |

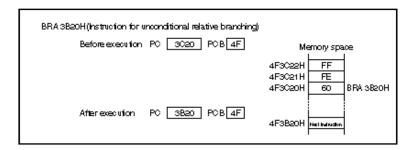

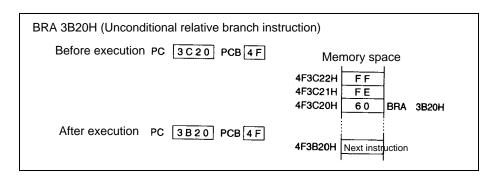

| Figure B.4-7   | Example of program counter relative branch addressing (rel)                                               | 499 |

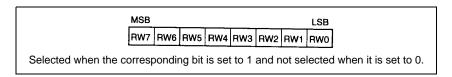

| Figure B.4-8   | Register list configuration                                                                               | 500 |

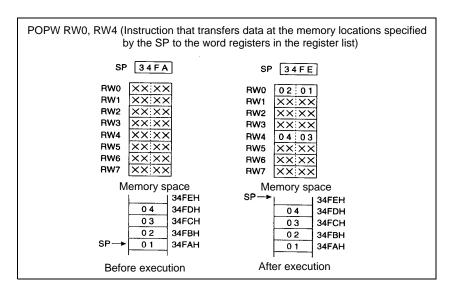

| Figure B.4-9   | Example of register list (rlst)                                                                           | 500 |

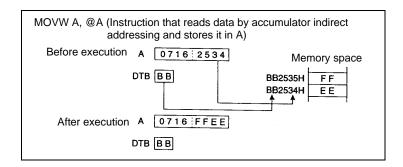

| Figure B.4-10  | Example of accumulator indirect addressing (@A)                                                           | 500 |

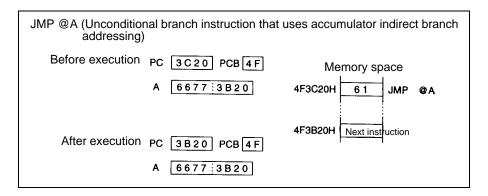

| Figure B.4-11  | Example of accumulator indirect branch addressing (@A)                                                    | 501 |

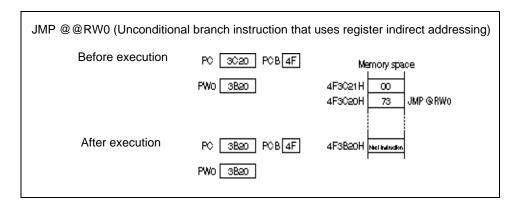

| Figure B.4-12  | Example of indirect designation branch addressing (@ear)                                                  | 501 |

| Figure B.4-13  | Example of indirect designation branch addressing (@eam)                                                  | 502 |

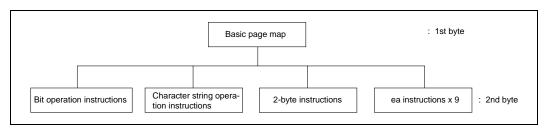

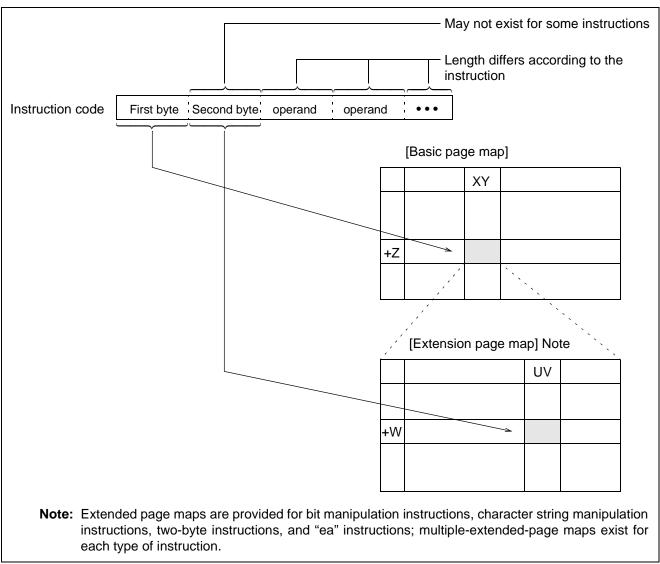

| Figure B.9-1   | Configuration of instruction maps                                                                         | 523 |

| Figure B.9-2   | Relationship between actual instruction codes and instruction maps                                        | 524 |

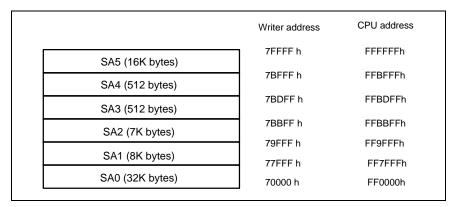

| Figure C-1     | Sector configuration of 512K-bit flash memory                                                             | 545 |

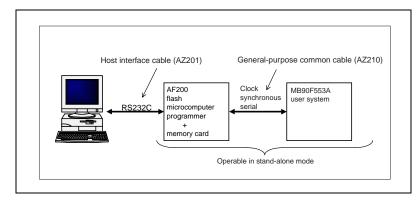

| Figure D-1     | Standard configuration for Fujitsu standard serial on-board writing                                       | 551 |

|                |                                                                                                           |     |

MB90560 series xv

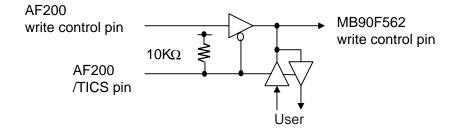

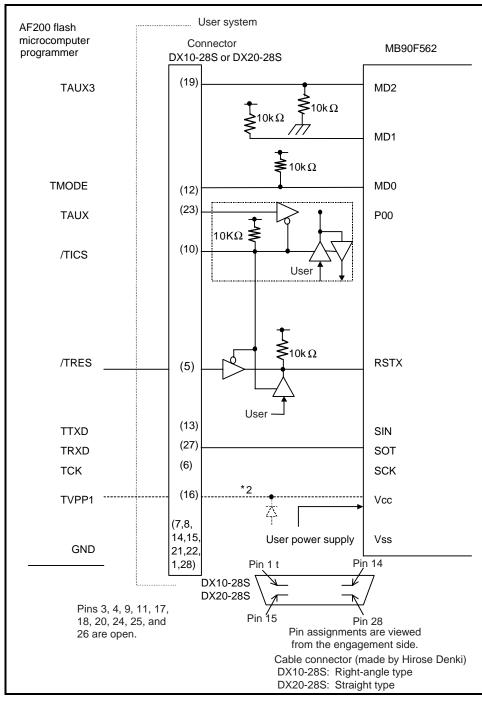

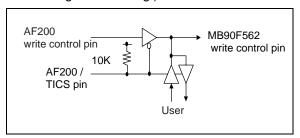

| Figure D.2 | Connection example for MB90F562 serial writing |  |

|------------|------------------------------------------------|--|

xvi MB90560 series

# **TABLES**

| Table 1.2-1                | Product lineup of the MB90560 series                                                        | 4    |

|----------------------------|---------------------------------------------------------------------------------------------|------|

| Table 1.6-1                | Pin functions                                                                               | 14   |

| Table 1.6-2                | Pin functions (Continued)                                                                   | 15   |

| Table 1.6-3                | Pin functions (Continued)                                                                   | 16   |

| Table 1.7-1                | I/O circuit types                                                                           | 18   |

| Table 1.7-2                | I/O circuit types (Continued)                                                               | 19   |

| Table 2.4-1                | Access space and main function of each bank register                                        | 32   |

| Table 2.4-2                | Addressing and default spaces                                                               | 33   |

| Table 2.7-1                | Initial values of the dedicated registers                                                   | 39   |

| Table 2.7-2                | Stack address specification                                                                 | 44   |

| Table 2.7-3                | Interrupt level mask register (ILM) and interrupt level priority                            | 51   |

| Table 2.8-1                | Typical functions of general-purpose registers                                              | 57   |

| Table 2.9-1                | Bank select prefix codes and selected memory spaces                                         | 60   |

| Table 2.9-2                | Instructions not affected by bank select prefix codes                                       | 60   |

| Table 2.9-3                | Instructions which use requires caution when bank select prefix codes are used              | 61   |

| Table 2.9-4                | Instructions whose use requires caution when the common register bank prefix (CMR) is used  | 62   |

| Table 2.9-5                | Instructions requiring caution when the flag change suppression prefix (NCC) is used        | 63   |

| Table 2.9-6                | Prefix codes and interrupt/hold suppression instructions                                    | 64   |

| Table 3.1-1                | Reset causes                                                                                | 68   |

| Table 3.2-1                | Reset causes and oscillation stabilization wait intervals                                   | 70   |

| Table 3.2-2                | Oscillation stabilization wait intervals set by the clock selection register (CKSCR)        | 70   |

| Table 3.5-1                | Correspondence between reset cause bits and reset causes                                    | 77   |

| Table 4.3-1                | Function description of each bit of the clock selection register (CKSCR)                    | 87   |

| Table 5.3-1                | Function description of each bit of the low power consumption mode control register (LPMCR) | 99   |

| Table 5.3-2                | Instructions to be used for switching to low power consumption mode                         | .100 |

| Table 5.5-1                | Operation statuses during standby mode                                                      | .103 |

| Table 5.6-1                | Low power consumption mode operating states                                                 | .113 |

| Table 5.6-2                | Clock mode switching and release                                                            | .113 |

| Table 5.6-3                | Switching to and release of standby mode                                                    | .114 |

| Table 5.7-1                | State of pins in single-chip mode                                                           | .115 |

| Table 6.2-1                | Interrupt vectors                                                                           | .122 |

|                            |                                                                                             |      |

| Table 6.2-2                | Interrupt causes, interrupt vectors, and interrupt control registers                        | .123 |

| Table 6.2-2<br>Table 6.3-1 | Interrupt causes, interrupt vectors, and interrupt control registers                        |      |

| Table 6.3-3 | Correspondence between the EI2OS channel selection bits and descriptor addresses | 129 |

|-------------|----------------------------------------------------------------------------------|-----|

| Table 6.3-4 | Relationship between EI2OS status bits and the EI2OS status                      | 130 |

| Table 6.4-1 | Mechanisms used for hardware interrupts                                          | 133 |

| Table 6.4-2 | Hardware interrupt suppression instruction                                       | 134 |

| Table 6.4-3 | Compensation values (Z) for the interrupt handling time                          | 143 |

| Table 6.6-1 | Correspondence between channel numbers and descriptor addresses                  | 148 |

| Table 6.7-1 | Extended intelligent I/O service execution time                                  | 156 |

| Table 6.7-2 | Data transfer compensation value for EI2OS execution time                        | 156 |

| Table 6.7-3 | Interpolation value (Z) for the interrupt handling time                          | 157 |

| Table 7.2-1 | Mode pin settings                                                                | 169 |

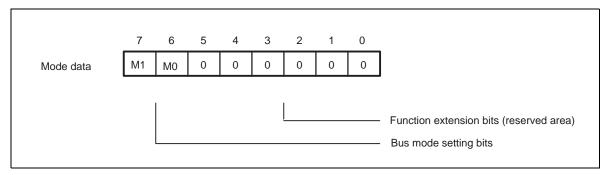

| Table 7.3-1 | Bus mode setting bits and functions                                              | 170 |

| Table 7.3-2 | Relationship between mode pins and mode data                                     | 171 |

| Table 8.1-1 | Functions of individual ports                                                    | 174 |

| Table 8.2-1 | Registers and corresponding ports                                                | 175 |

| Table 8.3-1 | Port 0 pins                                                                      | 176 |

| Table 8.3-2 | Port 0 pins and their corresponding register bits                                | 177 |

| Table 8.3-3 | Port 0 register functions                                                        | 178 |

| Table 8.3-4 | States of port 0 pins                                                            | 181 |

| Table 8.4-1 | Port 1 pins                                                                      | 182 |

| Table 8.4-2 | Port 1 pins and their corresponding register bits                                | 183 |

| Table 8.4-3 | Port 1 register functions                                                        | 184 |

| Table 8.4-4 | States of port 1 pins                                                            | 187 |

| Table 8.5-1 | Port 2 pins                                                                      | 188 |

| Table 8.5-2 | Port 2 pins and their corresponding register bits                                | 189 |

| Table 8.5-3 | Port 2 register functions                                                        | 190 |

| Table 8.5-4 | States of port 2 pins                                                            | 193 |

| Table 8.6-1 | Port 3 pins                                                                      | 194 |

| Table 8.6-2 | Port 3 pins and their corresponding register bits                                | 195 |

| Table 8.6-3 | Port 3 register functions                                                        | 196 |

| Table 8.6-4 | States of port 3 pins                                                            | 199 |

| Table 8.7-1 | Port 4 pins                                                                      | 200 |

| Table 8.7-2 | Port 4 pins and their corresponding register bits                                | 201 |

| Table 8.7-3 | Port 4 register functions                                                        | 202 |

| Table 8.7-4 | States of port 4 pins                                                            | 205 |

| Table 8.8-1 | Port 5 pins                                                                      | 206 |

| Table 8.8-2 | Port 5 pins and their corresponding register bits                                | 207 |

| Table 8.8-3 | Port 5 register functions                                                        | 208 |

| Table 8.8-4      | States of port 5 pins                                                                                     | 211 |

|------------------|-----------------------------------------------------------------------------------------------------------|-----|

| Table 8.9-1      | Port 6 pins                                                                                               | 212 |

| Table 8.9-2      | Port 6 pins and their corresponding register bits                                                         | 213 |

| Table 8.9-3      | Port 6 register functions                                                                                 | 214 |

| Table 8.9-4      | States of port 6 pins                                                                                     | 217 |

| Table 9.1-1      | Intervals for the timebase timer                                                                          | 222 |

| Table 9.1-2      | Clock cycle time supplied from the timebase timer                                                         | 223 |

| Table 9.3-1      | Function description of each bit in the timebase timer control register (TBTC)                            | 227 |

| Table 9.4-1      | Timebase interrupts and EI2OS                                                                             | 228 |

| Table 9.5-1      | Timebase timer counter clearing and oscillation stabilization wait intervals                              | 231 |

| Table 10.1-1     | Intervals for the watchdog timer                                                                          | 238 |

| Table 10.3-1     | Function description of each bit of the watchdog timer control register (WDTC)                            | 241 |

| Table 11.1-1     | 16-bit reload timer operating modes                                                                       | 248 |

| Table 11.1-2     | Intervals for the 16-bit reload timer                                                                     | 249 |

| Table 11.1-3     | 16-bit reload timer interrupts and EI2OS                                                                  | 250 |

| Table 11.3-1     | 16-bit reload timer pins                                                                                  | 254 |

| Table 11.4-1     | Function description of each bit of the upper part of the timer control status register (TMC TMCSR1: H)   |     |

| Table 11.4-2     | Function description of each bit of the low part of the timer control status register (TMCSR0, TMCSR1: L) | 259 |

| Table 11.5-1     | Interrupt control bits and interrupt causes of the 16-bit reload timer                                    | 262 |

| Table 11.5-2     | 16-bit reload timer interrupts and EI2OS                                                                  | 262 |

| Table 12.3.1.3-1 | Timer Control Status Register (Upper) Bit                                                                 | 295 |

| Table 12.3.1.3-2 | Timer Control Status Register (Lower)                                                                     | 297 |

| Table 12.3.2.2-1 | Compare Control Register (Upper, OSC1/3/5) Bit                                                            | 301 |

| Table 12.3.2.2-2 | Compare Control Register (Lower, OSC0/2/4)                                                                | 303 |

| Table 12.3.3.2-1 | Capture Control Register (ICS23) Bit                                                                      | 307 |

| Table 12.3.3.2-2 | Capture Control Register (ICS01)                                                                          | 309 |

| Table 12.3.4.1-1 | Function of PPG Reload registers                                                                          | 311 |

| Table 12.3.4.2-1 | PPG1/3/5 Control Register (PPGC1/3/5) Bit                                                                 | 313 |

| Table 12.3.4.2-2 | PPG0/2/4 Control Register (PPG0/2/4)                                                                      | 315 |

| Table 12.3.4.3-1 | PPG0/1/2/3/4/5 Clock Control Register (PPG0/2/4)                                                          | 317 |

| Table 12.3.5.2-1 | 8-bit Timer Control Registers (DTCR0/1/2) Bit                                                             | 321 |

| Table 12.3.5.3-1 | Waveform Control Register (SIGCR)                                                                         | 323 |

| Table 12.4.4-1   | Reload operation and pulse output                                                                         | 334 |

| Table 13.1-1     | UART functions                                                                                            | 352 |

| Table 13.1-2     | UART interrupt and EI2OS                                                                                  | 353 |

| Table 13.3-1     | UART pins                                                                                                 | 358 |

| Table 13.4-1     | Functions of each bit of serial control register (SCR0/1)                                                 | 363 |

MB90560 series xix

| Table 13.4-2 | Functions of each bit of serial mode control register (SMR0/1)                              | 365 |

|--------------|---------------------------------------------------------------------------------------------|-----|

| Table 13.4-3 | Functions of each bit of serial status register (SSR0/1)                                    | 367 |

| Table 13.4-4 | Communication prescaler                                                                     | 370 |

| Table 13.5-1 | Interrupt control bits and interrupt causes of UART                                         | 372 |

| Table 13.5.2 | UART interrupts and EI2OS                                                                   | 373 |

| Table 13.6-1 | Selection of each division ratio for the machine clock prescaler                            | 378 |

| Table 13.6-2 | Selection of synchronous baud rate division ratios                                          | 379 |

| Table 13.6-3 | Selection of synchronous baud rate division ratios                                          | 379 |

| Table 13.6-4 | Baud rates and reload values                                                                | 383 |