### INTEGRATED CIRCUITS

# DATA SHEET

# **TEA1200TS**0.95 V starting DC-to-DC converter with low battery indicator

**Product specification**

2002 May 14

### **TEA1200TS**

### **FEATURES**

- Complete DC-to-DC converter circuit and battery low detector

- Configurable for 1, 2 or 3-cell Nickel-Cadmium (NiCd) or Nickel Metal Hydride (NiMH) batteries and 1 Lithium Ion (Li-Ion) battery

- Guaranteed DC-to-DC converter start-up from 1-cell NiCd or NiMH battery, even with a load current

- Upconversion or downconversion

- Internal power MOSFETs featuring a low  $R_{DSon}$  of approximately 0.1  $\Omega$

- Synchronous rectification for high efficiency

- · Soft start

- · PWM-only operating option

- Stand-alone low battery detector requires no additional supply voltage

- Low battery detection level at 0.90 V, externally adjustable to a higher level

- · Adjustable output voltages

- · Shut-down function

- · Small outline package

- 0.6 μm BICMOS process.

### **APPLICATIONS**

- · Cellular phones

- · Cordless phones

- Personal Digital Assistants (PDAs)

- · Portable audio players

- Pagers

- Mobile equipment.

### **GENERAL DESCRIPTION**

The TEA1200TS is a fully integrated battery power unit including a high-efficiency DC-to-DC converter which runs from a 1-cell NiCd or NiMH battery and a low battery detector. The circuit can be arranged in several ways to optimize the application circuit of a power supply system. Therefore, the DC-to-DC converter can be arranged for upconversion or downconversion and the low battery detector can be configured for several types of batteries. Accurate low battery detection is possible while all other blocks are switched off.

The DC-to-DC converter features efficient, compact and dynamic power conversion using a digital control concept comparable with Pulse Width Modulation (PWM) and Pulse Frequency Modulation (PFM), integrated CMOS power switches with a very low R<sub>DSon</sub> and fully synchronous rectification.

The device operates at a switching frequency of 600 kHz which enables the use of external components with minimum size. The switching frequency can be synchronized to an external high frequency clock signal. Optionally, the device can be kept in PWM control mode only. Deadlock is prevented by an on-chip undervoltage lockout circuit.

Active current limiting enables efficient conversion in pulsed-load systems such as Global System for Mobile communication (GSM) and Digital Enhanced Cordless Telecommunications (DECT).

The low battery detector has a built-in detection level which is optimum for a 1-cell NiCd or NiMH battery.

### **ORDERING INFORMATION**

| TYPE      |        | PACKAGE                                                           |          |  |  |

|-----------|--------|-------------------------------------------------------------------|----------|--|--|

| NUMBER    | NAME   | E DESCRIPTION VERS                                                |          |  |  |

| TEA1200TS | SSOP16 | plastic shrink small outline package; 16 leads; body width 4.4 mm | SOT369-1 |  |  |

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### **QUICK REFERENCE DATA**

| SYMBOL                | PARAMETER                                      | CONDITIONS                                             | MIN.                  | TYP.  | MAX.  | UNIT |

|-----------------------|------------------------------------------------|--------------------------------------------------------|-----------------------|-------|-------|------|

| DC-to-DC c            | onverter                                       |                                                        | <u> </u>              | !     |       | !    |

| UPCONVERS             | ION                                            |                                                        |                       |       |       |      |

| V <sub>i(up)</sub>    | input voltage                                  |                                                        | V <sub>i(start)</sub> | _     | 5.50  | V    |

| V <sub>o(up)</sub>    | output voltage                                 |                                                        | V <sub>o(uvlo)</sub>  | _     | 5.50  | V    |

| V <sub>i(start)</sub> | start-up input voltage                         | I <sub>L</sub> < 10 mA                                 | 0.93                  | 0.96  | 1.00  | V    |

| V <sub>o(uvlo)</sub>  | undervoltage lockout voltage                   | note 1                                                 | 2.0                   | 2.2   | 2.4   | V    |

| DOWNCONVE             | ERSION                                         |                                                        | ·                     |       |       |      |

| V <sub>i(dwn)</sub>   | input voltage                                  |                                                        | V <sub>o(uvlo)</sub>  | _     | 5.50  | V    |

| V <sub>o(dwn)</sub>   | output voltage                                 |                                                        | 1.30                  | _     | 5.50  | V    |

| CURRENT LE            | VELS                                           |                                                        |                       | •     | •     | •    |

| I <sub>q(DC/DC)</sub> | quiescent current at pin UPOUT/DNIN            |                                                        | -                     | 110   | _     | μΑ   |

| I <sub>shdwn</sub>    | current in shut-down mode                      | $V_{LBI1} = V_{I(up)} = 1.2 \text{ V}$                 | _                     | 65    | _     | μΑ   |

| I <sub>LX(max)</sub>  | maximum continuous current at pins LX1 and LX2 | T <sub>amb</sub> = 80 °C                               | _                     | _     | 1.0   | А    |

| $\Delta I_{lim}$      | current limit deviation                        | I <sub>lim</sub> set to 1.0 A                          |                       |       |       |      |

|                       |                                                | upconversion                                           | -12                   | -     | +12   | %    |

|                       |                                                | downconversion                                         | -12                   | -     | +12   | %    |

| Power MOS             | SFETs                                          |                                                        |                       |       |       |      |

| R <sub>DSon(N)</sub>  | drain-to-source on-state resistance NFET       | $T_j = 27  ^{\circ}\text{C};  I_{DS} = 100  \text{mA}$ | -                     | 110   | 200   | mΩ   |

| R <sub>DSon(P)</sub>  | drain-to-source on-state resistance PFET       | $T_j = 27 ^{\circ}\text{C};  I_{DS} = 100 \text{mA}$   | _                     | 125   | 250   | mΩ   |

| EFFICIENCY            |                                                | ,                                                      | <u>'</u>              |       | •     | •    |

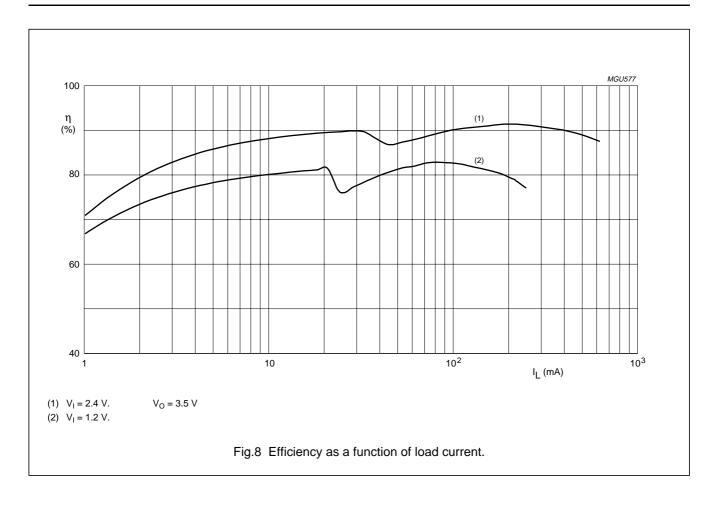

| η                     | efficiency upconversion                        | see Fig.8; Vo up to 3.3 V                              |                       |       |       |      |

|                       |                                                | $V_i = 1.2 \text{ V}; I_L = 100 \text{ mA}$            | _                     | 84    | _     | %    |

|                       |                                                | $V_i = 2.4 \text{ V}; I_L = 10 \text{ mA}$             | _                     | 92    | _     | %    |

| TIMING                |                                                |                                                        |                       | •     | •     | •    |

| f <sub>sw</sub>       | switching frequency                            | PWM mode                                               | 480                   | 600   | 720   | kHz  |

| f <sub>i(sync)</sub>  | synchronization clock input frequency          |                                                        | 6                     | 13    | 20    | MHz  |

| t <sub>start</sub>    | start-up time                                  |                                                        | _                     | 10    | _     | ms   |

|                       | aracteristics                                  | •                                                      |                       | •     | •     | •    |

| V <sub>ref</sub>      | reference voltage                              |                                                        | 1.165                 | 1.190 | 1.215 | V    |

### Note

The undervoltage lockout level shows wide specification limits since it decreases with increasing temperature. When

the temperature increases, the minimum supply voltage of the digital control part of the IC decreases and therefore

the correct operation of this function is guaranteed over the whole temperature range. The undervoltage lockout level

is measured at pin UPOUT/DNIN.

Product specification

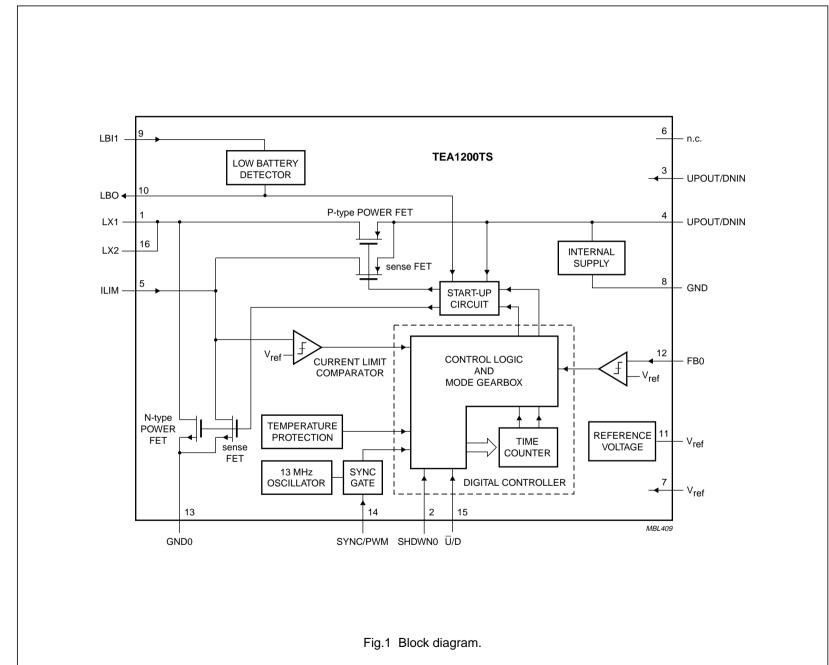

**BLOCK DIAGRAM**

Philips Semiconductors

TEA1200TS

# 0.95 V starting DC-to-DC converter with low battery indicator

### TEA1200TS

### **PINNING**

| SYMBOL     | PIN | DESCRIPTION                                                                  |

|------------|-----|------------------------------------------------------------------------------|

| LX1        | 1   | inductor connection 1                                                        |

| SHDWN0     | 2   | DC-to-DC converter shut-down input                                           |

| UPOUT/DNIN | 3   | up mode: DC-to-DC converter output; down mode DC-to-DC converter input       |

| UPOUT/DNIN | 4   | up mode: DC-to-DC converter<br>output; down mode DC-to-DC<br>converter input |

| ILIM       | 5   | current limiting resistor connection                                         |

| n.c.       | 6   | not connected                                                                |

| $V_{ref}$  | 7   | reference voltage input                                                      |

| GND        | 8   | internal supply ground                                                       |

| LBI1       | 9   | low battery detector input 1                                                 |

| LBO        | 10  | low battery detector output                                                  |

| $V_{ref}$  | 11  | reference voltage input                                                      |

| FB0        | 12  | DC-to-DC converter feedback input                                            |

| GND0       | 13  | DC-to-DC converter ground                                                    |

| SYNC/PWM   | 14  | synchronization clock input or PWM-only selection input                      |

| Ū/D        | 15  | conversion mode selection input                                              |

| LX2        | 16  | inductor connection 2                                                        |

# LX1 1 1 16 LX2 15 Ū/D 14 SYNC/PWM 13 GND0 12 FB0 11 Vref 10 LBO 9 LBI1 Fig.2 Pin configuration.

### **FUNCTIONAL DESCRIPTION**

### **Control mechanism**

The TEA1200TS DC-to-DC converter is able to operate in the PFM (discontinuous conduction) or PWM (continuous conduction) operating mode. All switching actions are completely determined by a digital control circuit which uses the output voltage level as its control input. This novel digital approach enables the use of a new pulse width and frequency modulation scheme, which ensures optimum power efficiency over the complete range of operation of the converter.

When high output power is requested, the device will operate in the PWM operating mode. This results in minimum AC currents in the circuit components and hence optimum efficiency, minimum costs and low EMC. In this operating mode, the output voltage is allowed to vary between two predefined voltage levels. As long as the output voltage stays within this so-called window, switching continues in a fixed pattern.

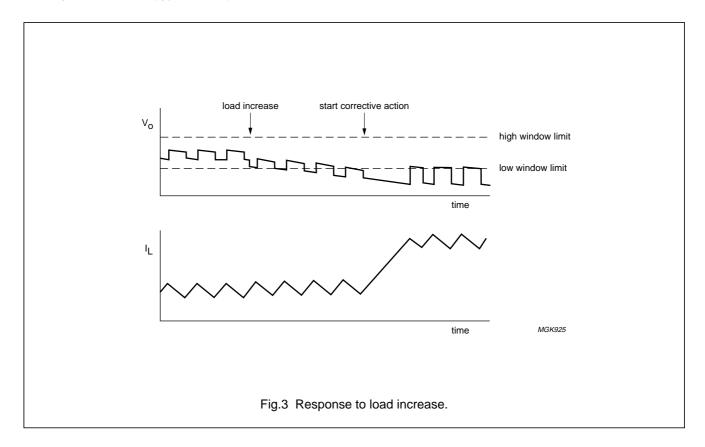

When the output voltage reaches one of the window borders, the digital controller immediately reacts by adjusting the pulse width and inserting a current step in such a way that the output voltage stays within the window with higher or lower current capability. This approach enables very fast reaction to load variations. Figure 3 shows the response of the converter to a sudden load increase. The upper trace shows the output voltage.

The ripple on top of the DC level is a result of the current in the output capacitor, which changes in sign twice per cycle, times the internal Equivalent Series Resistance (ESR) of the capacitor. After each ramp-down of the inductor current, i.e. when the ESR effect increases the output voltage, the converter determines what to do in the next cycle. As soon as more load current is taken from the output the output voltage starts to decay.

# 0.95 V starting DC-to-DC converter with low battery indicator

### TEA1200TS

When the output voltage becomes lower than the low limit of the window, a corrective action is taken by a ramp-up of the inductor current during a much longer time. As a result, the DC current level is increased and normal PWM control can continue. The output voltage (including ESR effect) is again within the predefined window.

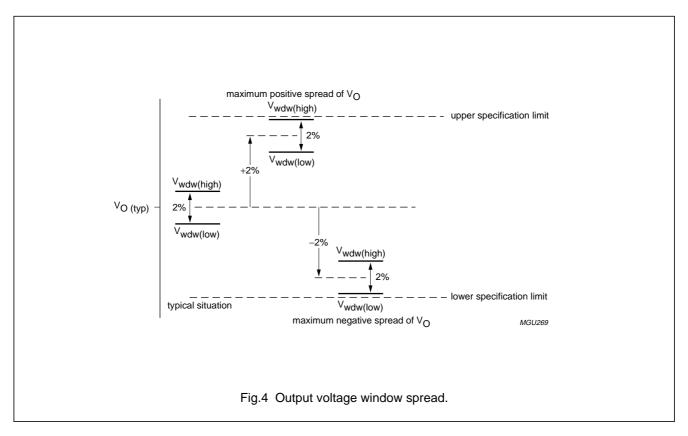

Figure 4 shows the spread of the output voltage window. The absolute value is mostly dependent on spread, while the actual window size  $[V_{wdw(high)} - V_{wdw(low)}]$  is not affected. For one specific device, the output voltage will not vary more than 2% (typical value).

In low output power situations, the TEA1200TS will switch over to PFM operating mode. In this mode, regulation information from an earlier PWM operating mode is used. This results in optimum inductor peak current levels in the PFM mode, which are slightly larger than the inductor ripple current in the PWM mode. As a result, the transition between PFM and PWM mode is optimum under all circumstances. In the PFM mode the TEA1200TS regulates the output voltage to the high window limit as shown in Fig.3.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### Synchronous rectification

For optimum efficiency over the whole load range, synchronous rectifiers within the TEA1200TS ensure that during the whole second switching phase, all inductor current will flow through the low-ohmic power MOSFETs. Special circuitry is included which detects when the inductor current reaches zero. Following this detection, the digital controller switches off the power MOSFET and proceeds with regulation.

### Start-up

Start-up from low input voltage in the boost mode is realized by an independent start-up oscillator, which starts switching the N-type power MOSFET as soon as the low-battery detector detects a sufficiently high voltage. The inductor current is limited internally to ensure soft-starting. The switch actions of the start-up oscillator will increase the output voltage. As soon as the output voltage is high enough for normal regulation, the digital control system will take control over the power MOSFETs.

### **Undervoltage lockout**

As a result of too high a load or disconnection of the input power source, the output voltage can drop so low that normal regulation cannot be guaranteed. In this event, the device switches back to start-up mode. If the output voltage drops even further, switching is stopped completely.

### Shut-down

When the shut-down input is set HIGH, the DC-to-DC converter disables both switches and power consumption is reduced to a few microamperes.

### Power switches

The power switches in the IC are one N-type and one P-type power MOSFET, both having a typical drain-to-source resistance of 100 m $\Omega$ . The maximum continuous current in the power switches is 1.0 A at  $T_{amb} = 80$  °C.

# 0.95 V starting DC-to-DC converter with low battery indicator

TEA1200TS

### Temperature protection

When the DC-to-DC converter operates in the PWM mode, and the die temperature gets too high (typical value is 190 °C), the converter will stop operating. It resumes operation when the die temperature falls below 90 °C again. As a result, low frequency cycling between the on and off state will occur. It should be noted that in the event of device temperatures at the cut-off limit, the application differs strongly from maximum specifications.

### **Current limiters**

If the current in one of the power switches exceeds the programmed limit in the PWM mode, the current ramp is stopped immediately and the next switching phase is entered. Current limiting is required to keep power conversion efficient during temporary high loads. Furthermore, current limiting protects the IC against overload conditions, inductor saturation, etc.

The current limiting level is set by an external resistor which must be connected between pin ILIM and ground for downconversion, or between pins ILIM and UPOUT/DNIN for upconversion.

### **External synchronization and PWM-only mode**

If an external high-frequency clock or a HIGH level is applied to pin SYNC/PWM, the TEA1200TS will use PWM regulation independent of the load applied.

In the event that a high-frequency clock is applied, the switching frequency in the PWM mode will be exactly that frequency divided by 22. In the PWM mode the quiescent current of the device increases.

In the event that no external synchronization or PWM mode selection is necessary, pin SYNC/PWM must be connected to ground.

### Behaviour when the input voltage exceeds the specified range

In general, an input voltage exceeding the specified range is not recommended since instability may occur. There are two exceptions:

- Upconversion: at an input voltage higher than the target output voltage, but up to 5.5 V, the converter will stop switching and the external Schottky diode will take over. The output voltage will equal the input voltage minus the diode voltage drop. Since all current flows through the external diode in this situation, the current limiting function is not active.

- In the PWM mode, the P-type power MOSFET is always on when the input voltage exceeds the target output voltage. The internal synchronous rectifier ensures that the inductor current does not fall below zero. As a result, the achieved efficiency is higher in this situation than standard PWM-controlled converters achieve.

- Downconversion: when the input voltage is lower than the target output voltage, but higher than 2.2 V, the P-type power MOSFET will stay conducting resulting in the output voltage being equal to the input voltage minus some resistive voltage drop. The current limiting function remains active.

### Low battery detector

The low battery detector is an autonomous circuit which can work at an input voltage down to 0.90 V. It is always on, even when all other blocks are in the shut-down mode.

The low battery input (pin LBI1) is adjusted to accept a 1-cell NiCd or NiMH battery voltage directly. Hysteresis is included for proper operating.

The output of the low battery detector (pin LBO) is an open-collector output. The output is high (i.e. no current is sunk by the collector) when the input voltage of the detector is below the lower detection level.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL           | PARAMETER                      | CONDITIONS     | MIN. | MAX.  | UNIT |

|------------------|--------------------------------|----------------|------|-------|------|

| V <sub>n</sub>   | voltage on any pin             | shut-down mode | -0.2 | +6.5  | V    |

|                  |                                | operating mode | -0.2 | +5.5  | ٧    |

| Tj               | junction temperature           |                | -40  | +150  | °C   |

| T <sub>amb</sub> | ambient temperature            |                | -20  | +80   | Ô    |

| T <sub>stg</sub> | storage temperature            |                | -40  | +125  | °C   |

| V <sub>es</sub>  | electrostatic handling voltage | notes 1 and 2  | Cla  | ss II | ٧    |

### **Notes**

- 1. ESD specification is in accordance with the JEDEC standard:

- a) Human Body Model (HBM) tests are carried out by discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

- b) Machine Model (MM) tests are carried out by discharging a 200 pF capacitor via a 0.75 μH series inductor.

- 2. Exception is pin ILIM: 1000 V HBM and 100 V MM.

### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 143   | K/W  |

### **QUALITY SPECIFICATION**

In accordance with "SNW-FQ-611 D".

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### **CHARACTERISTICS**

$T_{amb}$  = -20 to +80 °C; all voltages are measured with respect to ground; positive currents flow into the IC; unless otherwise specified.

| SYMBOL                                                     | PARAMETER                                                  | CONDITIONS                                             | MIN.                  | TYP. | MAX. | UNIT |

|------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|-----------------------|------|------|------|

| DC-to-DC c                                                 | onverter                                                   |                                                        | -                     | •    | •    | 1    |

| UPCONVERS                                                  | ION; pin $\overline{U}/D = LOW$                            |                                                        |                       |      |      |      |

| V <sub>i(up)</sub>                                         | input voltage                                              |                                                        | V <sub>i(start)</sub> | _    | 5.50 | V    |

| V <sub>o(up)</sub>                                         | output voltage                                             |                                                        | V <sub>o(uvlo)</sub>  | _    | 5.50 | V    |

| V <sub>i(start)</sub>                                      | start-up input voltage                                     | I <sub>L</sub> < 10 mA                                 | 0.93                  | 0.96 | 1.00 | V    |

| V <sub>o(uvlo)</sub>                                       | undervoltage lockout voltage                               | note 1                                                 | 2.0                   | 2.2  | 2.4  | V    |

| Downconve                                                  | ERSION; pin $\overline{U}/D = HIGH$                        |                                                        | •                     | •    | •    | •    |

| V <sub>i(dwn)</sub>                                        | input voltage                                              | note 2                                                 | V <sub>o(uvlo)</sub>  | _    | 5.50 | V    |

| V <sub>o(dwn)</sub>                                        | output voltage                                             |                                                        | 1.30                  | _    | 5.50 | V    |

| REGULATION                                                 |                                                            |                                                        |                       |      |      |      |

| $\Delta V_{o(wdw)}$                                        | output voltage window size as a function of output voltage | PWM mode                                               | 1.5                   | 2.0  | 2.5  | %    |

| CURRENT LE                                                 | VELS                                                       |                                                        | !                     |      |      |      |

| I <sub>q(DC/DC)</sub>                                      | quiescent current at pin UPOUT/DNIN                        | note 3                                                 | _                     | 110  | _    | μΑ   |

| I <sub>shdwn</sub>                                         | current in shut-down mode                                  | $V_{LBI1} = V_{I(up)} = 1.2 \text{ V}$                 | _                     | 65   | _    | μΑ   |

| I <sub>lim(max)</sub>                                      | maximum current limit                                      | V 17                                                   | _                     | 5    | _    | Α    |

| $\Delta I_{lim}$                                           | current limit deviation                                    | I <sub>lim</sub> set to 1.0 A; note 4                  |                       |      |      |      |

|                                                            |                                                            | upconversion                                           | -12                   | _    | +12  | %    |

|                                                            |                                                            | downconversion                                         | -12                   | _    | +12  | %    |

| I <sub>LX(max)</sub>                                       | maximum continuous current at pins LX1 and LX2             | T <sub>amb</sub> = 80 °C                               | _                     | _    | 1.0  | A    |

| Power MOS                                                  | SFETs                                                      |                                                        |                       | •    |      | •    |

| R <sub>DSon(N)</sub>                                       | drain-to-source on-state resistance NFET                   | $T_j = 27  ^{\circ}\text{C};  I_{DS} = 100  \text{mA}$ | -                     | 110  | 200  | mΩ   |

| R <sub>DSon(P)</sub>                                       | drain-to-source on-state resistance PFET                   | $T_j = 27  ^{\circ}\text{C};  I_{DS} = 100  \text{mA}$ | _                     | 125  | 250  | mΩ   |

| EFFICIENCY                                                 |                                                            |                                                        | ·                     |      | •    |      |

| η                                                          | efficiency upconversion                                    | see Fig.8; V <sub>o</sub> up to 3.3 V; note 5          |                       |      |      |      |

|                                                            |                                                            | V <sub>i</sub> = 1.2 V; I <sub>L</sub> = 100 mA        | _                     | 84   | _    | %    |

|                                                            |                                                            | $V_i = 2.4 \text{ V}; I_L = 10 \text{ mA}$             | _                     | 92   | _    | %    |

| TIMING                                                     |                                                            |                                                        |                       |      |      |      |

| f <sub>sw</sub>                                            | switching frequency                                        | PWM mode                                               | 480                   | 600  | 720  | kHz  |

| f <sub>i(sync)</sub> synchronization clock input frequency |                                                            |                                                        | 6                     | 13   | 20   | MHz  |

| t <sub>start</sub>                                         | start-up time                                              | note 6                                                 | _                     | 10   | _    | ms   |

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

| SYMBOL               | PARAMETER                                       | CONDITIONS               | MIN.               | TYP.  | MAX.                 | UNIT |

|----------------------|-------------------------------------------------|--------------------------|--------------------|-------|----------------------|------|

| DIGITAL INPU         | T LEVELS                                        |                          | <u>'</u>           |       | 1                    | !    |

| $V_{IL(n)}$          | LOW-level input voltage on all digital pins     |                          | 0                  | _     | 0.4                  | V    |

| V <sub>IH(n)</sub>   | HIGH-level input voltage                        | note 7                   |                    |       |                      |      |

|                      | on pins SYNC/PWM,<br>SHDWN0 and SHDWN2          |                          | 0.55V <sub>4</sub> | _     | V <sub>4</sub> + 0.3 | V    |

|                      | all other digital input pins                    |                          | $V_4 - 0.4$        | _     | $V_4 + 0.3$          | V    |

| Low battery          | detector                                        |                          |                    |       |                      |      |

| t <sub>t(HL)</sub>   | HIGH-to-LOW transition time                     | falling V <sub>BAT</sub> | _                  | 2     | _                    | μs   |

| DETECTION I          | NPUT PIN LBI1                                   |                          |                    |       |                      |      |

| V <sub>det(LB)</sub> | low battery detection level                     | falling V <sub>BAT</sub> | 0.87               | 0.90  | 0.93                 | V    |

| $V_{hys(LB)}$        | low battery detection hysteresis                |                          | _                  | 20    | _                    | mV   |

| TC <sub>Vdet</sub>   | temperature coefficient of detection level      |                          | _                  | 0     | _                    | mV/K |

| TC <sub>Vhys</sub>   | temperature coefficient of detection hysteresis |                          | _                  | 0.175 | -                    | mV/K |

| DETECTION (          | DUTPUT PIN LBO                                  |                          | •                  |       |                      |      |

| I <sub>o(sink)</sub> | output sink current                             |                          | 15                 | _     | _                    | μΑ   |

| General cha          | aracteristics                                   |                          |                    |       |                      |      |

| V <sub>ref</sub>     | reference voltage                               |                          | 1.165              | 1.190 | 1.215                | V    |

| Iq                   | quiescent current at pin UPOUT/DNIN             | all blocks operating     | _                  | 270   | -                    | μΑ   |

| T <sub>amb</sub>     | ambient temperature                             |                          | -20                | +25   | +80                  | °C   |

| T <sub>max</sub>     | internal temperature for cut-off                |                          | _                  | 190   | _                    | °C   |

### **Notes**

- The undervoltage lockout level shows wide specification limits since it decreases with increasing temperature. When

the temperature increases, the minimum supply voltage of the digital control part of the IC decreases and therefore

the correct operation of this function is guaranteed over the whole temperature range. The undervoltage lockout level

is measured at pin UPOUT/DNIN.

- 2. When  $V_i$  is lower than the target output voltage but higher than 2.2 V, the P-type power MOSFET will remain conducting (duty factor is 100%), resulting in  $V_o$  following  $V_i$ .

- 3. The quiescent current is specified as the input current in the upconversion configuration at  $V_i$  = 1.20 V and  $V_o$  = 3.30 V, using L1 = 6.8  $\mu$ H, R1 = 150 k $\Omega$  and R2 = 91 k $\Omega$ .

- 4. The current limit is defined by resistor R10. This resistor must be 1% accurate.

- 5. The specified efficiency is valid when using an output capacitor having an ESR of 0.1  $\Omega$  and an inductor of 6.8  $\mu$ H with an ESR of 0.05  $\Omega$  and a sufficient saturation current level.

- 6. The specified start-up time is the time between the connection of a 1.20 V input voltage source and the moment the output reaches 3.30 V. The output capacitance equals 100 μF, the inductance equals 6.8 μH and no load is present.

- V<sub>4</sub> is the voltage at pin UPOUT/DNIN. If the applied HIGH-level voltage is less than V<sub>4</sub> 1 V, the quiescent current

of the device will increase.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

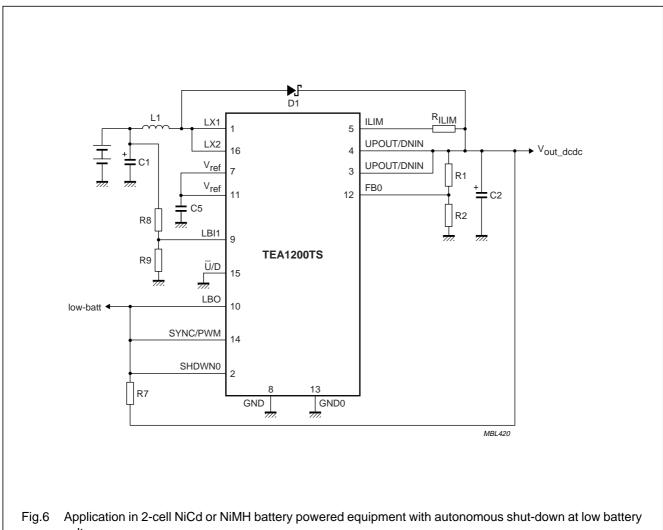

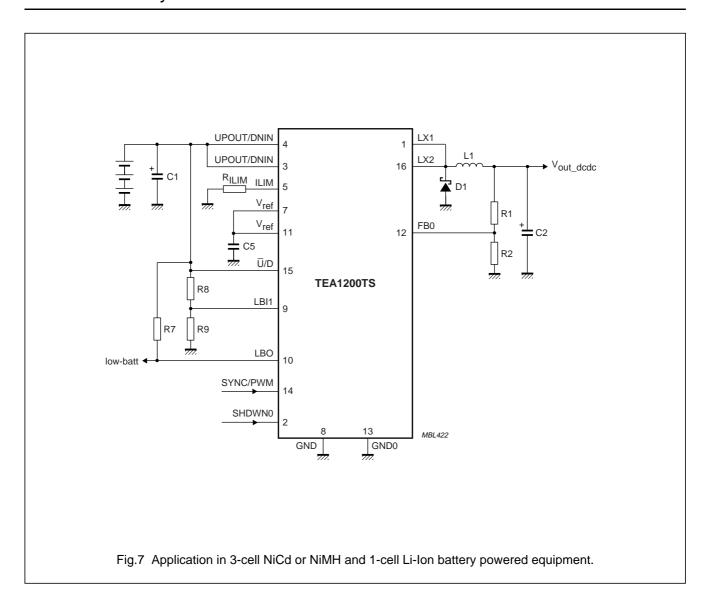

### **APPLICATION INFORMATION**

### 0.95 V starting DC-to-DC converter with low battery indicator

### **TEA1200TS**

voltage.

2002 May 14 13

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

**TEA1200TS**

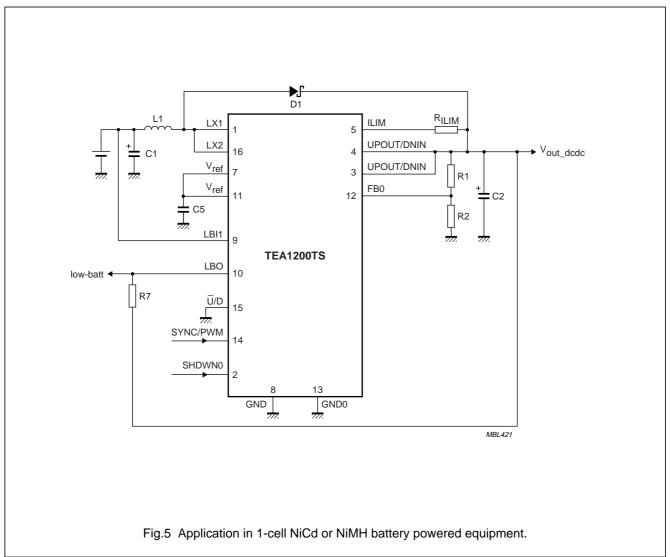

### **External component selection**

### INDUCTOR L1

The performance of the TEA1200TS is not very sensitive to inductance value. The best efficiency performance over a wide load current range is achieved by using an inductance of 6.8  $\mu$ H e.g. TDK SLF7032 or Coilcraft DO1608 range.

### DC-TO-DC CONVERTER INPUT CAPACITOR C1

The value of C1 strongly depends on the type of input source. In general, a 100  $\mu F$  tantalum capacitor is sufficient.

### DC-TO-DC CONVERTER OUTPUT CAPACITOR C2

The value and type of C2 depends on the maximum output current and the ripple voltage which is allowed in the application. Low-ESR tantalum capacitors show good results. The most important specification of C2 is its ESR, which mainly determines the output voltage ripple.

### DIODE D1

The Schottky diode is only used for short time during takeover from N-type power MOSFET and P-type power MOSFET and vice versa. Therefore, a medium-power diode is sufficient in most applications e.g. Philips PRLL5819.

### FEEDBACK RESISTORS R1 AND R2

The output voltage of the DC-to-DC converter is determined by the resistors R1 and R2. The following conditions apply:

- Only use a 1% accurate SMD type resistors. If larger body-size resistors are used, the capacitance on pin FB0 will be too large, and could cause inaccurate operation.

- Resistors R1 and R2 should have a maximum value of  $50~\text{k}\Omega$  when connected in parallel. A higher value will result in inaccurate operation.

Under these conditions, the output voltage can be calculated by the following equation:

$$V_o = V_{ref} \times \left(1 + \frac{R1}{R2}\right)$$

### **CURRENT LIMITING RESISTOR R10**

The maximum instantaneous current is set by the external resistor R10. The preferred type is SMD, with 1% accuracy.

The connection of resistor R10 differs for each mode:

- At upconversion: resistor R10 must be connected between pins ILIM and UPOUT/DNIN; the current limiting level is defined by:  $I_{lim} = \frac{320}{R10}$

- At downconversion: resistor R10 must be connected between pins ILIM and GND0; the current limiting level is defined by:  $I_{lim} = \frac{300}{R10}$

The average inductor current during limited current operation also depends on the inductance value, input voltage, output voltage and resistive losses in all components in the power path. Ensure that  $I_{lim} < I_{sat}$  (saturation current) of the inductor.

### REFERENCE VOLTAGE DECOUPLING CAPACITOR C5

Optionally, a decoupling capacitor can be connected between pin  $V_{ref}$  and ground in order to achieve a lower noise level of the output voltages of the LDO. The best choice for C5 is a ceramic multilayer capacitor of approximately 10 nF.

LOW BATTERY DETECTOR COMPONENTS R7, R8 AND R9

Resistor R7 is connected between pin LBO and the input or output pin and must be 330  $k\Omega$  or higher.

A 1-cell NiCd or NiMH battery can be connected directly to pin LBI1.

A higher battery voltage can be detected by application of a divider circuit with resistor R8 and R9. The low-battery detection level for a higher battery voltage can be set by using the following equation:

$$V_{LBI(det))} \, = \, V_{det} \times \frac{R9}{(R8 + R9)}$$

Since current flows into pin LBI1, the parallel impedance of R8 and R9 must be approximately 1 k $\Omega$  in order to avoid inaccuracy due to the spread of the LBI1 current.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

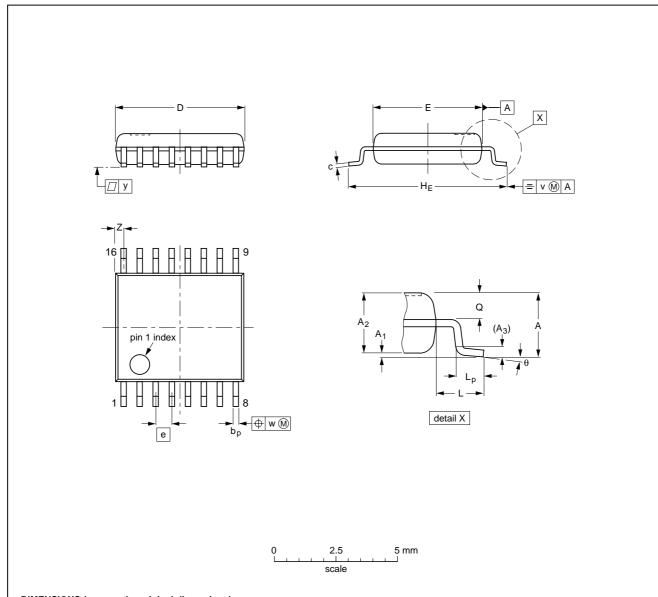

### **PACKAGE OUTLINE**

SSOP16: plastic shrink small outline package; 16 leads; body width 4.4 mm

SOT369-1

### **DIMENSIONS** (mm are the original dimensions)

|      |           |                |                |                |              | -,           |                  |                  |      |            |     |              |              |     |      |     |                  |           |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|-----|--------------|--------------|-----|------|-----|------------------|-----------|

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L   | Lp           | Q            | v   | w    | у   | z <sup>(1)</sup> | θ         |

| mm   | 1.5       | 0.15<br>0.00   | 1.4<br>1.2     | 0.25           | 0.32<br>0.20 | 0.25<br>0.13 | 5.30<br>5.10     | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.45 | 0.65<br>0.45 | 0.2 | 0.13 | 0.1 | 0.48<br>0.18     | 10°<br>0° |

### Note

1. Plastic or metal protrusions of 0.20 mm maximum per side are not included.

| OUTLINE  |     | REFERENCES |      |  |  | ISSUE DATE                       |

|----------|-----|------------|------|--|--|----------------------------------|

| VERSION  | IEC | JEDEC      | EIAJ |  |  | ISSUE DATE                       |

| SOT369-1 |     | MO-152     |      |  |  | <del>-95-02-04</del><br>99-12-27 |

## 0.95 V starting DC-to-DC converter with low battery indicator

### **TEA1200TS**

### **SOLDERING**

### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended.

### Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 220 °C for thick/large packages, and below 235 °C for small/thin packages.

### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is **preferred** to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to  $300\ ^{\circ}$ C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320  $^{\circ}$ C.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                                             | SOLDERING METHOD                  |                       |  |  |

|-----------------------------------------------------|-----------------------------------|-----------------------|--|--|

| PACKAGE                                             | WAVE                              | REFLOW <sup>(1)</sup> |  |  |

| BGA, HBGA, LFBGA, SQFP, TFBGA                       | not suitable                      | suitable              |  |  |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, SMS | not suitable(2)                   | suitable              |  |  |

| PLCC <sup>(3)</sup> , SO, SOJ                       | suitable                          | suitable              |  |  |

| LQFP, QFP, TQFP                                     | not recommended <sup>(3)(4)</sup> | suitable              |  |  |

| SSOP, TSSOP, VSO                                    | not recommended <sup>(5)</sup>    | suitable              |  |  |

### **Notes**

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 2. These packages are not suitable for wave soldering. On versions with the heatsink on the bottom side, the solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the heatsink on the top side, the solder might be deposited on the heatsink surface.

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

# 0.95 V starting DC-to-DC converter with low battery indicator

**TEA1200TS**

### **DATA SHEET STATUS**

| DATA SHEET STATUS(1) | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITIONS                                                                                                                                                                                                                                                                                                            |

|----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data       | Development                      | This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                            |

| Preliminary data     | Qualification                    | This data sheet contains data from the preliminary specification.  Supplementary data will be published at a later date. Philips  Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                   |

| Product data         | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

### **Notes**

- 1. Please consult the most recently issued data sheet before initiating or completing a design.

- 2. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

### **DEFINITIONS**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### **DISCLAIMERS**

Life support applications — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

TEA1200TS

**NOTES**

TEA1200TS

**NOTES**

TEA1200TS

**NOTES**

### Philips Semiconductors – a worldwide company

### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2002

SCA74

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

403502/01/pp24

Date of release: 2002 May 14

Document order number: 9397 750 09358

Let's make things better.

Philips Semiconductors