# 12-BIT SERIAL TO PARALLEL CONVERTER

### GENERAL DESCRIPTION

The NJU3714 is a 12-bit serial to parallel converter especially apply to MPU outport expander.

The effective outport assignment of MPU is available as the connection between NJU3714 and MPU is required only 4 lines.

Up to 5MHz signal can be input to the serial data input terminal and the data is output from parallel output buffer through serial in parallel out shift register and parallel data latches.

Furthermore, the NJU3714 output the serial data from SO terminal through the shift register, therefore output bit number can increase by cascade connection.

The hysteresis input circuit realized wide noise margin and high driverbility output buffer (25mA) can drive LED directly.

PACKAGE OUTLINE

NJU3714D

NJU3714G

FEATURES 12-Bit Serial In Parallel Out Cascade Connection 0 P51 20 Vpd 0.5V typ Hysteresis Input P6 2 19 ] P4 **Operating Voltage**  $5V \pm 10\%$ P7 3 **1** P3 18 **Operating Frequency** 5MHz or more P8 4 17 ] P2  $V_{ss}$ 5 16 ] PI Output Current 25mA P9. 6 15 ] ν<sub>ss</sub> C-MOS Technology P10 7 CLR 14 Package Outline DIP/SOP 20 PH 8 13 ] STB P12 [ 9 12 CLK so [ 10 ] DATA 11

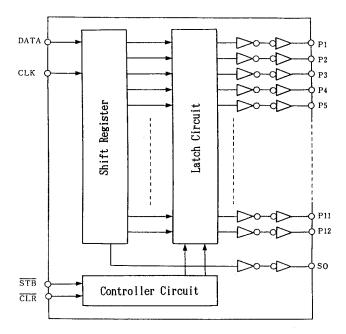

### BLOCK DIAGRAM

PIN CONFIGURATION

7-29

# JRC

### TERMINAL DESCRIPTION

| NO. | SYMBOL | FUNCTION                    | NO. | SYMBOL          | FUNCTION                     |

|-----|--------|-----------------------------|-----|-----------------|------------------------------|

| 1   | P5     |                             | 11  | DATA            | Serial Data Input Terminal   |

| 2   | P6     | Parallel Converts           | 12  | CLK             | Clock Signal Input Terminal  |

| 3   | P7     | Data Output Terminals       | 13  | STB             | Strove Signal Input Terminal |

| 4   | P8     |                             | 14  | CLR             | Clear Signal Input Terminal  |

| 5   | Vss    | GND                         | 15  | Vss             | GND                          |

| 6   | P9     |                             | 16  | P1              |                              |

| 7   | P10    | Parallel Converts           | 17  | P2              | Parallel Converts            |

| 8   | P11    | Data Output Terminals       | 18  | P3              | Data Output Terminals        |

| 9   | P12    |                             | 19  | P4              |                              |

| 10  | SO     | Serial Data Output Terminal | 20  | V <sub>DD</sub> | Power Supply Terminal        |

### FUNCTIONAL DESCRIPTION

#### (1) Reset

When the "L" level is input to the  $\overline{\text{CLR}}$  terminal, all latches are reset and all parallel conversion output are "L" level.

Normally, the  $\overline{CLR}$  terminal should be "H" level.

### (2) Data Transmission

In the STB terminal is "H" level and input the clock signal to the CLK terminal, the serial data input from DATA terminal shift in the shift register by synclonizing at rising edge of the clock signal.

When the  $\overline{\text{STB}}$  terminal change to "L" level, the data in the shift register transfer to the latch. Even if the  $\overline{\text{STB}}$  terminal is "L" level, the input clock signal shift the data in the shift register, therefore, the clock signal control is needed.

### (3) Cascade Connection

The serial data input from DATA terminal output from the SO terminal through internal shift register unrelated the CLR and  $\overline{STB}$  status.

Furthermore, the 4 input terminals have a hysteresis characteristics by using the schmitt trigger structure to protect the noise.

| CLK        | STB | CLR | O P E R A T I O N                                                                                           |

|------------|-----|-----|-------------------------------------------------------------------------------------------------------------|

| х          | х   | L   | All latch are reset (the data in the shift register is no change).                                          |

|            |     |     | All of Parallel convert output are "L".                                                                     |

| ſ          | н   |     | The serial data input from DATA terminal input to the shift register.                                       |

| Ţ          | п   | H   | In this stage, the data in the latch is no change.                                                          |

| L          |     |     | The data in the shift register transfer to the latch. And the data                                          |

| Н          |     | Н   | in the latch output from parallel output.                                                                   |

| _          |     | F   | The CLK input in the $\overline{\text{STB}}=$ "L" and $\overline{\text{CLR}}=$ "H" state, the data shift in |

| $\uparrow$ |     |     | the shift register and latched data also change in accordance with                                          |

|            |     |     | the shift register.                                                                                         |

Note ) X: Don't care

New Japan Radio Co., Ltd.-

# JRC

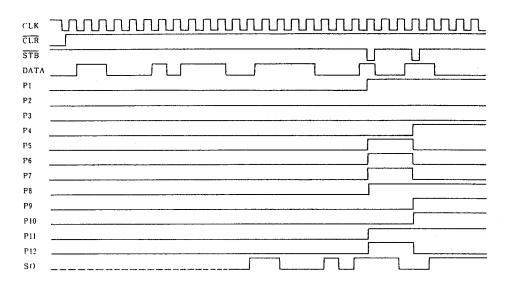

## TIMING CHART

## ■ ABSOLUTE MAXIMUM RATINGS

( Ta=25°C )

| PARAMETER                   | SYMBOL         | RATINGS                                     | UNIT |

|-----------------------------|----------------|---------------------------------------------|------|

| Supply Voltage Range        | VDD            | - 0.5 ~ + 7.0                               | V    |

| Input Voltage Range         | V <sub>1</sub> | V <sub>SS</sub> -0.5 ~ V <sub>DD</sub> +0.5 | V    |

| Output Voltage Range        | Vo             | V <sub>SS</sub> -0.5 ~ V <sub>DD</sub> +0.5 | V    |

| Output Current              | lo             | ±25                                         | mA   |

| Power Dissipation           | PD             | 700 (DTP)<br>400 (SOP)                      | mW   |

| Operating Temperature Range | Topr           | -25 ~ +85                                   | °C   |

| Storage Temperature Range   | Tstg           | -65 ~ +150                                  | °C   |

-New Japan Radio Co.,Ltd.-

## DC ELECTRICAL CHARACTERISTICS

|                           |            | 00     |                  |                                 | (V⊳⊳=4.5~ | ∕5.5V, Vs | s=OV, Ta | =25℃) |

|---------------------------|------------|--------|------------------|---------------------------------|-----------|-----------|----------|-------|

| PARAMETER                 |            | SYMBOL | CONDITION        |                                 | MIN       | ТҮР       | MAX      | UNIT  |

| Operating Current         |            | loos   | ViH=Vod, ViL=Vss |                                 |           |           | 0.1      | mA    |

|                           | High-Level | Vон    | lон=-0.4mA       | SO Terminal                     | 4.0       |           | Vod      | v     |

| Output Voltage            | Low-Level  | Vo∟    | lo∟=+3.2mA       |                                 | Vss       |           | 0.4      |       |

| Innut Valtara             | High-Level | Vан    |                  |                                 | 0.7100    |           | Vod      | v     |

| Input Voltage             | Low-Level  | Vi∟    |                  |                                 | Vss       | -         | 0.3Vpp   | V     |

| Input Leakage Current     |            | lui -  | V1=0~VDD         |                                 | -10       |           | 10       | μA    |

| High-Level Output Voltage |            | Vонр   | lон=-25mA        |                                 | Voo-1.5   |           | Vdd      |       |

|                           |            |        | Iон=-15mA        |                                 | Voo-1.0   |           | Vdd      | V.    |

|                           |            |        | Iон=-10mA        | P1∼P12<br>Terminals             | Voo-0.5   |           | Vdd      |       |

|                           |            |        | lo∟=+25mA        | lerminais                       | Vss       |           | 1.5      |       |

| Low-Level Output Voltage  |            | Vold   | lo∟=+15mA        | (Note 1)                        | Vss       |           | 0.8      | ۷     |

|                           |            |        | lo∟=+10mA        |                                 | Vss       |           | 0.4      |       |

| Output Short Current      |            | los    | Vo=7V, V1=0V     | SO Terminal                     |           |           | 10       |       |

|                           |            |        | Vo=0V, V1=7V     | (Note 2)                        |           |           | -10      | mA    |

|                           |            | losd   | V₀=7V, Vı=0V     | P1~P12                          |           |           | 20       | mA    |

|                           |            |        | Vo=0V, V1=7V     | P1∼P12<br>Termina s<br>(Note 2) |           |           | -20      |       |

Note 1) Specified value represent output current per pin. When use, total current consideration and less than power dissipation rating operation should be required. Note 2) Vp=7V, Vss=0V, 1 second per pin.

## SWITCHING CHARACTERISTICS

(VDD=4.5V~5.5V, Vss=0V, Ta=-20~75°C)

|                          |          | •                   |     |     |     | ,    |

|--------------------------|----------|---------------------|-----|-----|-----|------|

| PARAMETER                | SYMBOL   | CONDITION           | MEN | TYP | MAX | UNIT |

| Set-Up Time              | tsp      | DATA – CLK          | 20  |     |     | ns   |

| Hold Time                | tнр      | CLK – DATA          | 20  |     |     | ns   |

| Set-Up Time              | tssтв    | STB – CLK           | 30  |     |     | ns   |

| Hold Time                | tнятв    | CLK - STB           | 30  |     |     | ns   |

|                          | tpd 0    | CLK – SO            |     |     | 70  | ns   |

|                          | tpd PCK  | CLK - P1~P12        |     |     | 100 | ns   |

| Output Delay Time        | tpd PSTB | <u>STB</u> − P1~P12 |     |     | 80  | ns   |

|                          | tod PCLR | CLR - P1~P12        |     |     | 80  | ns   |

| Max. Operating Frequency | fмах     |                     | 5   |     |     | MHz  |

\* ) Cour=50pF

7

ī

# SWITCHING CHARACTERISTICS TEST WAVEFORM

1

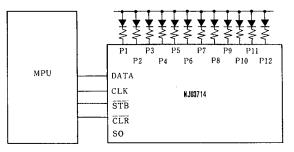

## APPLICATION CIRCUIT (1)

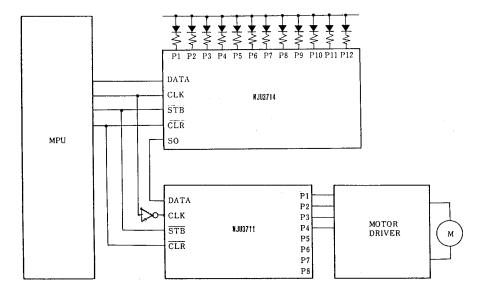

## APPLICATION CIRCUIT (2) (Combined with NJU3711)

**MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.