# CY7C185

# 8K x 8 Static RAM

#### **Features**

- High speed

- -15 ns

- Fast t<sub>DOE</sub>

- · Low active power

- —715 mW

- Low standby power

- -220 mW

- · CMOS for optimum speed/power

- Easy memory expansion with CE<sub>1</sub>, CE<sub>2</sub> and OE features

- TTL-compatible inputs and outputs

- · Automatic power-down when deselected

#### **Functional Description**

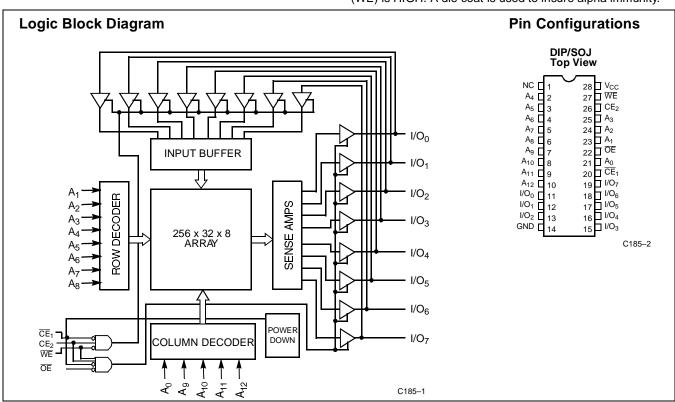

The CY7C185 is a high-performance CMOS static RAM organized as 8192 words by 8 bits. Easy memory expansion is

provided by an active LOW chip enable  $(\overline{CE}_1)$ , an active HIGH chip enable  $(\overline{CE}_2)$ , and active LOW output enable  $(\overline{OE})$  and three-state drivers. This device has an automatic power-down feature  $(\overline{CE}_1$  or  $\overline{CE}_2)$ , reducing the power consumption by 70% when deselected. The CY7C185 is in a standard 300-mil-wide DIP and SOJ package.

An active LOW write enable signal ( $\overline{\text{WE}}$ ) controls the writing/reading operation of the memory. When  $\overline{\text{CE}}_1$  and  $\overline{\text{WE}}$  inputs are both LOW and  $\text{CE}_2$  is HIGH, data on the eight data input/output pins (I/O $_0$  through I/O $_7$ ) is written into the memory location addressed by the address present on the address pins (A $_0$  through A $_1$ 2). Reading the device is accomplished by selecting the device and enabling the outputs,  $\overline{\text{CE}}_1$  and  $\overline{\text{OE}}$  active LOW,  $\text{CE}_2$  active HIGH, while  $\overline{\text{WE}}$  remains inactive or HIGH. Under these conditions, the contents of the location addressed by the information on address pins are present on the eight data input/output pins.

The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable ( $\overline{\text{WE}}$ ) is HIGH. A die coat is used to insure alpha immunity.

#### Selection Guide[1]

|                                | 7C185-12 | 7C185-15 | 7C185-20 | 7C185-25 | 7C185-35 |

|--------------------------------|----------|----------|----------|----------|----------|

| Maximum Access Time (ns)       | 12       | 15       | 20       | 25       | 35       |

| Maximum Operating Current (mA) | 140      | 130      | 110      | 100      | 100      |

| Maximum Standby Current (mA)   | 40/15    | 40/15    | 20/15    | 20/15    | 20/15    |

Shaded areas contain preliminary information.

Note:

1. For military specifications, see the CY7C185A/CY7C186A datasheet.

### Pin Configurations (continued)

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guide-lines, not tested.)

Storage Temperature ......-65°C to +150°C

Ambient Temperature with

Power Applied .....-55°C to +125°C

Supply Voltage to Ground Potential .....-0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State<sup>[2]</sup> .....-0.5V to +7.0V

| Output Current into Outputs (LOW)                      | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001V  |

| Latch-Up Current                                       | >200 mA |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 10%        |

### **Electrical Characteristics** Over the Operating Range

DC Input Voltage<sup>[2]</sup>......-0.5V to +7.0V

|                  |                                                |                                                                                                                                                                                    | 7C18 | 7C185-12        |      | 7C185-15        |      |

|------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|-----------------|------|

| Parameter        | Description                                    | Test Conditions                                                                                                                                                                    | Min. | Max.            | Min. | Max.            | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                            | $V_{CC}$ = Min., $I_{OH}$ = -4.0 mA                                                                                                                                                | 2.4  |                 | 2.4  |                 | V    |

| V <sub>OL</sub>  | Output LOW Voltage                             | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA                                                                                                                                   |      | 0.4             |      | 0.4             | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                             |                                                                                                                                                                                    | 2.2  | V <sub>CC</sub> | 2.2  | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[2]</sup>               |                                                                                                                                                                                    | -0.5 | 0.8             | -0.5 | 0.8             | V    |

| I <sub>IX</sub>  | Input Load Current                             | $GND \le V_I \le V_{CC}$                                                                                                                                                           | -5   | +5              | -5   | +5              | μΑ   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                      | $\begin{aligned} &\text{GND} \leq \text{V}_{I} \leq \text{V}_{CC}, \\ &\text{Output Disabled} \end{aligned}$                                                                       | -5   | +5              | -5   | +5              | μΑ   |

| I <sub>OS</sub>  | Output Short<br>Circuit Current <sup>[3]</sup> | V <sub>CC</sub> = Max.,<br>V <sub>OUT</sub> = GND                                                                                                                                  |      | -300            |      | -300            | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating<br>Supply Current    | V <sub>CC</sub> = Max.,<br>I <sub>OUT</sub> = 0 mA                                                                                                                                 |      | 140             |      | 130             | mA   |

| I <sub>SB1</sub> | Automatic<br>Power-Down Current                | Max. $V_{CC}$ , $\overline{CE}_1 \ge V_{IH}$ or $CE_2 \le V_{IL}$<br>Min. Duty Cycle=100%                                                                                          | 40   |                 | 40   | mA              |      |

| I <sub>SB2</sub> | Automatic<br>Power-Down Current                | $\begin{aligned} &\text{Max. V}_{CC}, \ \overline{CE}_1 \geq V_{CC} - 0.3V, \\ &\text{or CE}_2 \leq 0.3V \\ &V_{IN} \geq V_{CC} - 0.3V \text{ or } V_{IN} \leq 0.3V \end{aligned}$ | 15   |                 | 15   | mA              |      |

Shaded areas contain preliminary information.

#### Notes:

2. Minimum voltage is equal to –3.0V for pulse durations less than 30 ns.

<sup>3. -</sup>Not more than 1 output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

# **Electrical Characteristics** Over the Operating Range (continued)

|                  |                                                |                                                                                                                                                                                                                                                               | 7C18 | 7C185-20        |            | 7C185–25, 35    |      |

|------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------------|-----------------|------|

| Parameter        | Description                                    | Test Conditions                                                                                                                                                                                                                                               | Min. | Max.            | Min.       | Max.            | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                            | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                                                                                                                                                                                                                     | 2.4  |                 | 2.4        |                 | V    |

| V <sub>OL</sub>  | Output LOW Voltage                             | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA                                                                                                                                                                                                              |      | 0.4             |            | 0.4             | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                             |                                                                                                                                                                                                                                                               | 2.2  | V <sub>CC</sub> | 2.2        | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[2]</sup>               |                                                                                                                                                                                                                                                               | -0.5 | 0.8             | -0.5       | 0.8             | V    |

| I <sub>IX</sub>  | Input Load Current                             | $GND \le V_I \le V_{CC}$                                                                                                                                                                                                                                      | -5   | +5              | -5         | +5              | μΑ   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                      | $\begin{aligned} &\text{GND} \leq \text{V}_{\text{I}} \leq \text{V}_{\text{CC}}, \\ &\text{Output Disabled} \end{aligned}$                                                                                                                                    | -5   | +5              | <b>-</b> 5 | +5              | μА   |

| I <sub>OS</sub>  | Output Short<br>Circuit Current <sup>[3]</sup> | V <sub>CC</sub> = Max.,<br>V <sub>OUT</sub> = GND                                                                                                                                                                                                             |      | -300            |            | -300            | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating<br>Supply Current    | V <sub>CC</sub> = Max.,<br>I <sub>OUT</sub> = 0 mA                                                                                                                                                                                                            |      | 110             |            | 100             | mA   |

| I <sub>SB1</sub> | Automatic<br>Power-Down Current                | $\begin{array}{l} \text{Max. V}_{CC}, \overline{CE}_1 \geq \text{V}_{\text{IH or }} CE_2 \leq \text{V}_{\text{IL}} \\ \text{Min. Duty Cycle=} 100\% \end{array}$                                                                                              |      | 20              |            | 20              | mA   |

| I <sub>SB2</sub> | Automatic<br>Power-Down Current                | $\begin{array}{l} \text{Max. V}_{\text{CC}}, \overline{\text{CE}}_1 \geq \text{V}_{\text{CC}} - 0.3\text{V} \\ \text{or CE}_2 \leq 0.3\text{V} \\ \text{V}_{\text{IN}} \geq \text{V}_{\text{CC}} - 0.3\text{V or V}_{\text{IN}} \leq 0.3\text{V} \end{array}$ |      | 15              |            | 15              | mA   |

# Capacitance<sup>[4]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 7    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 7    | pF   |

#### Note:

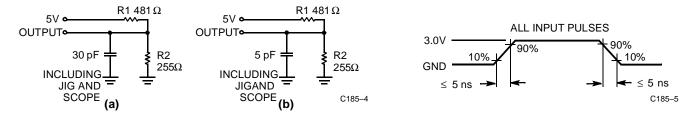

### **AC Test Loads and Waveforms**

Equivalent to: THÉVENIN EQUIVALENT

<sup>4.</sup> Tested initially and after any design or process changes that may affect these parameters.

## Switching Characteristics Over the Operating Range<sup>[5]</sup>

|                    |                                                                                   | 7C185-12 |      | 7C185-15 |      | 7C185-20 |      | 7C185-25 |      | 7C185-35 |      |                                                |

|--------------------|-----------------------------------------------------------------------------------|----------|------|----------|------|----------|------|----------|------|----------|------|------------------------------------------------|

| Parameter          | Description                                                                       | Min.     | Max. | Unit                                           |

| READ CYC           | LE                                                                                |          |      |          |      | 1        | 1    |          | 1    |          |      | 1                                              |

| t <sub>RC</sub>    | Read Cycle Time                                                                   | 12       |      | 15       |      | 20       |      | 25       |      | 35       |      | ns                                             |

| t <sub>AA</sub>    | Address to Data Valid                                                             |          | 12   |          | 15   |          | 20   |          | 25   |          | 35   | ns                                             |

| t <sub>OHA</sub>   | Data Hold from<br>Address Change                                                  | 3        |      | 3        |      | 5        |      | 5        |      | 5        |      | ns                                             |

| t <sub>ACE1</sub>  | CE <sub>1</sub> LOW to Data Valid                                                 |          | 12   |          | 15   |          | 20   |          | 25   |          | 35   | ns                                             |

| t <sub>ACE2</sub>  | CE <sub>2</sub> HIGH to Data Valid                                                |          | 12   |          | 15   |          | 20   |          | 25   |          | 35   | ns                                             |

| t <sub>DOE</sub>   | OE LOW to Data Valid                                                              |          | 6    |          | 8    |          | 9    |          | 12   |          | 15   | ns                                             |

| t <sub>LZOE</sub>  | OE LOW to Low Z                                                                   | 2        |      | 3        |      | 3        |      | 3        |      | 3        |      | ns                                             |

| t <sub>HZOE</sub>  | OE HIGH to High Z <sup>[6]</sup>                                                  |          | 6    |          | 7    |          | 8    |          | 10   |          | 10   | ns                                             |

| t <sub>LZCE1</sub> | CE <sub>1</sub> LOW to Low Z <sup>[7]</sup>                                       | 3        |      | 3        |      | 5        |      | 5        |      | 5        |      | ns                                             |

| t <sub>LZCE2</sub> | CE <sub>2</sub> HIGH to Low Z                                                     | 3        |      | 3        |      | 3        |      | 3        |      | 3        |      | ns                                             |

| t <sub>HZCE</sub>  | CE <sub>1</sub> HIGH to High Z <sup>[6, 7]</sup><br>CE <sub>2</sub> LOW to High Z |          | 6    |          | 7    |          | 8    |          | 10   |          | 10   | ns                                             |

| t <sub>PU</sub>    | CE <sub>1</sub> LOW to Power-Up<br>CE <sub>2</sub> to HIGH to Power-Up            | 0        |      | 0        |      | 0        |      | 0        |      | 0        |      | ns                                             |

| t <sub>PD</sub>    | CE <sub>1</sub> HIGH to Power-Down<br>CE <sub>2</sub> LOW to Power-Down           |          | 12   |          | 15   |          | 20   |          | 20   |          | 20   | ns                                             |

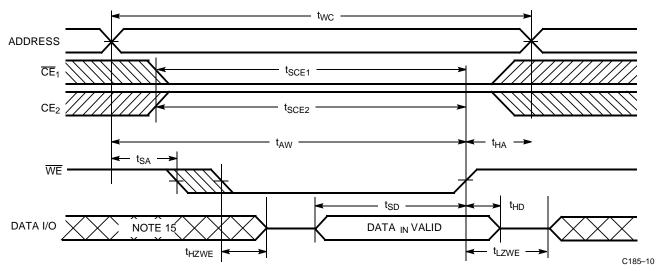

| WRITE CYC          | LE <sup>[8]</sup>                                                                 | l.       |      | l.       | ·    |          | ı    | l.       |      | l.       | I    | <u>,                                      </u> |

| t <sub>WC</sub>    | Write Cycle Time                                                                  | 12       |      | 15       |      | 20       |      | 25       |      | 35       |      | ns                                             |

| t <sub>SCE1</sub>  | CE <sub>1</sub> LOW to Write End                                                  | 8        |      | 12       |      | 15       |      | 20       |      | 20       |      | ns                                             |

| t <sub>SCE2</sub>  | CE <sub>2</sub> HIGH to Write End                                                 | 8        |      | 12       |      | 15       |      | 20       |      | 20       |      | ns                                             |

| t <sub>AW</sub>    | Address Set-Up to<br>Write End                                                    | 9        |      | 12       |      | 15       |      | 20       |      | 25       |      | ns                                             |

| t <sub>HA</sub>    | Address Hold from<br>Write End                                                    | 0        |      | 0        |      | 0        |      | 0        |      | 0        |      | ns                                             |

| t <sub>SA</sub>    | Address Set-Up to<br>Write Start                                                  | 0        |      | 0        |      | 0        |      | 0        |      | 0        |      | ns                                             |

| t <sub>PWE</sub>   | WE Pulse Width                                                                    | 8        |      | 12       |      | 15       |      | 15       |      | 20       |      | ns                                             |

| t <sub>SD</sub>    | Data Set-Up to Write End                                                          | 6        |      | 8        |      | 10       |      | 10       |      | 12       |      | ns                                             |

| t <sub>HD</sub>    | Data Hold from Write End                                                          | 0        |      | 0        |      | 0        |      | 0        |      | 0        |      | ns                                             |

| t <sub>HZWE</sub>  | WE LOW to High Z <sup>[6]</sup>                                                   |          | 6    |          | 7    |          | 7    |          | 7    |          | 8    | ns                                             |

| t <sub>LZWE</sub>  | WE HIGH to Low Z                                                                  | 3        |      | 3        |      | 5        |      | 5        |      | 5        |      | ns                                             |

Shaded areas contain preliminary information.

#### Notes:

Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified  $l_{0L}/l_{0H}$  and 30-pF load capacitance.  $t_{HZOE}$ ,  $t_{HZCE}$ , and  $t_{HZWE}$  are specified with  $C_L$  = 5 pF as in part (b) of AC Test Loads. Transition is measured  $\pm$ 500 mV from steady state voltage. At any given temperature and voltage condition,  $t_{HZOE}$  is less than  $t_{LZCE}$  for any given device. The internal write time of the memory is defined by the overlap of  $CE_1$  LOW,  $CE_2$  HIGH, and WE LOW. All 3 signals must be active to initiate a write and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

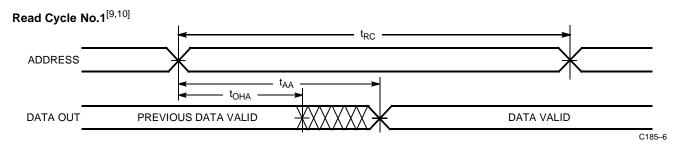

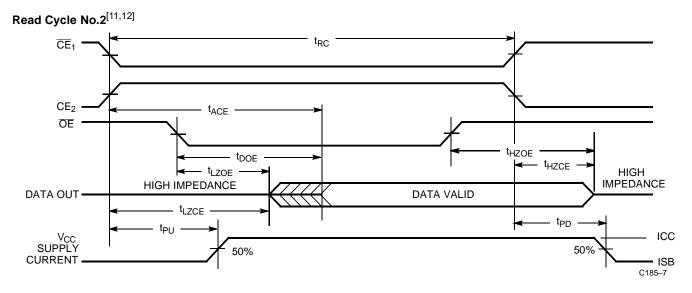

# **Switching Waveforms**

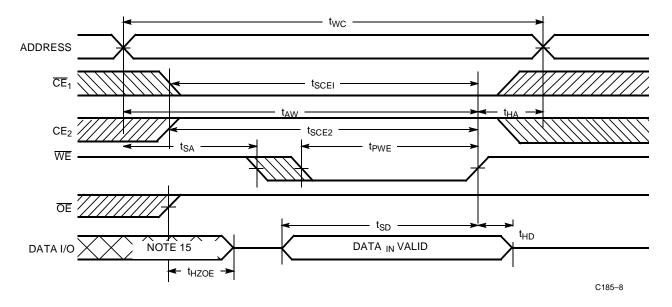

# Write CycleNo.1 ( $\overline{\text{WE}}$ Controlled) $^{[10,12]}$

### Switching Waveforms (continued)

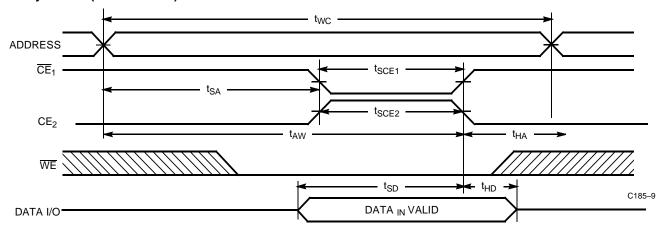

### Write Cycle no.2 (CE Controlled)[12,13,15]

# Write Cycle No.3 (WE Controlled, OE LOW)[12,13,14,15]

#### Notes:

- Device is continuously selected.  $\overline{OE}$ ,  $\overline{CE}_1 = V_{IL}$ .  $CE_2 = V_{IH}$ .  $\overline{WE}$  is HIGH for read cycle.

Data I/O is High Z if  $\overline{OE} = V_{IH}$ ,  $\overline{WE} = V_{IL}$  or  $CE_2 = V_{IL}$ .

The internal write time of the memory is defined by the overlap of  $\overline{CE}_1$  LOW,  $CE_2$  HIGH and  $\overline{WE}$  LOW.  $\overline{CE}_1$  and  $\overline{WE}$  must be LOW and  $CE_2$  must be HIGH to initiate write. A write can be terminated by  $\overline{CE}_1$  or  $\overline{WE}$  going HIGH or  $CE_2$  going LOW. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

The minimum write cycle time for write cycle #3 ( $\overline{WE}$  controlled,  $\overline{OE}$  LOW) is the sum of  $t_{HZWE}$  and  $t_{SD}$ . If  $\overline{CE}_1$  goes HIGH or  $CE_2$  goes LOW simultaneously with  $\overline{WE}$  HIGH, the output remains in a high-impedance state. During this period, the I/Os are in the output state and input signals should not be applied.

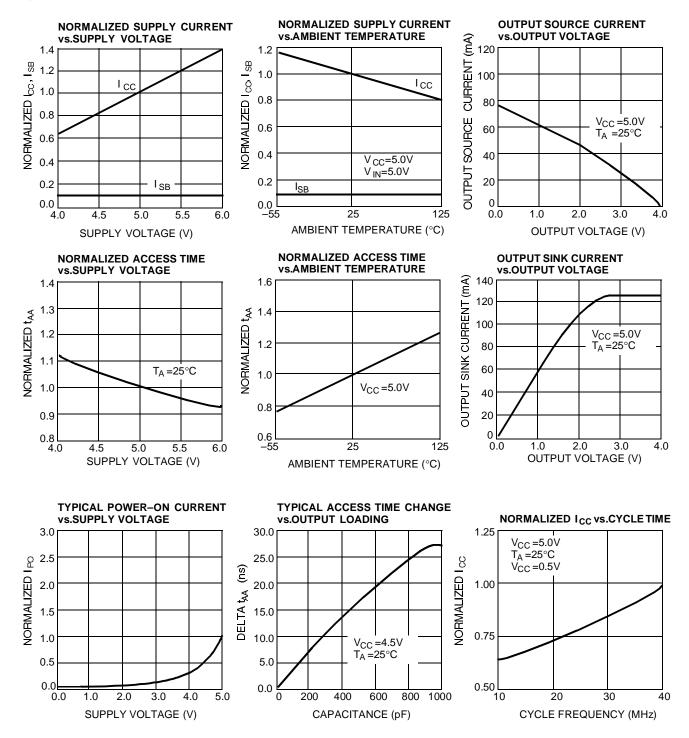

### **Typical DC and AC Characteristics**

### **Truth Table**

| CE <sub>1</sub> | CE <sub>2</sub> | WE | OE | Input/Output | Mode                |

|-----------------|-----------------|----|----|--------------|---------------------|

| Н               | Χ               | Χ  | Χ  | High Z       | Deselect/Power-Down |

| Х               | L               | Х  | Х  | High Z       | Deselect/Power-Down |

| L               | Н               | Н  | L  | Data Out     | Read                |

| L               | Н               | L  | Χ  | Data In      | Write               |

| L               | Н               | Н  | Н  | High Z       | Deselect            |

# **Address Designators**

| Address<br>Name | Address<br>Function | Pin<br>Number |

|-----------------|---------------------|---------------|

| A4              | X3                  | 2             |

| A5              | X4                  | 3             |

| A6              | X5                  | 4             |

| A7              | X6                  | 5             |

| A8              | X7                  | 6             |

| A9              | Y1                  | 7             |

| A10             | Y4                  | 8             |

| A11             | Y3                  | 9             |

| A12             | Y0                  | 10            |

| A0              | Y2                  | 21            |

| A1              | X0                  | 23            |

| A2              | X1                  | 24            |

| A3              | X2                  | 25            |

### **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                       | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------------|--------------------|

| 12            | CY7C185-12PC  | P21             | 28-Lead (300-Mil) Molded DIP       | Commercial         |

|               | CY7C185-12VC  | V21             | 28-Lead Molded SOJ                 |                    |

| 15            | CY7C185-15PC  | P21             | 28-Lead (300-Mil) Molded DIP       | Commercial         |

|               | CY7C185-15VC  | V21             | 28-Lead Molded SOJ                 |                    |

|               | CY7C185-15ZC  | Z28             | 28-Lead Thin Small Outline Package |                    |

| 20            | CY7C185-20PC  | P21             | 28-Lead (300-Mil) Molded DIP       | Commercial         |

|               | CY7C185-20VC  | V21             | 28-Lead Molded SOJ                 |                    |

|               | CY7C185-20ZC  | Z28             | 28-Lead Thin Small Outline Package |                    |

| 25            | CY7C185-25PC  | P21             | 28-Lead (300-Mil) Molded DIP       | Commercial         |

|               | CY7C185-25VC  | V21             | 28-Lead Molded SOJ                 |                    |

|               | CY7C185-25ZC  | Z28             | 28-Lead Thin Small Outline Package |                    |

| 35            | CY7C185-35PC  | P21             | 28-Lead (300-Mil) Molded DIP       | Commercial         |

|               | CY7C185-35VC  | V21             | 28-Lead Molded SOJ                 |                    |

|               | CY7C185-35ZC  | Z28             | 28-Lead Thin Small Outline Package |                    |

Shaded areas contain preliminary information.

Document #: 38-00037-K

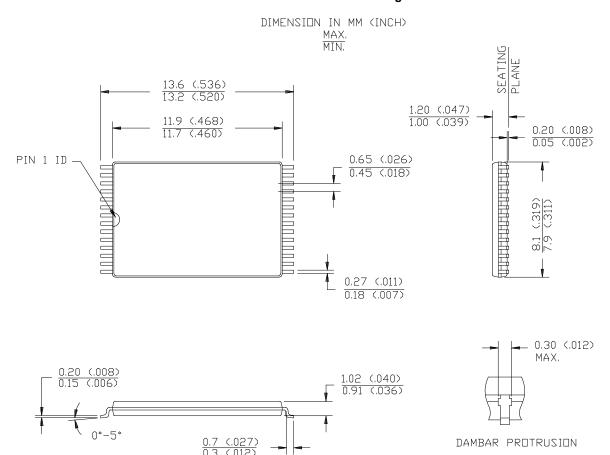

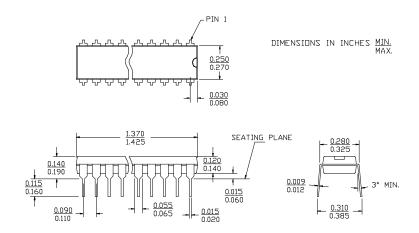

## **Package Diagrams**

### 28-Lead (300-Mil) Molded DIP P21

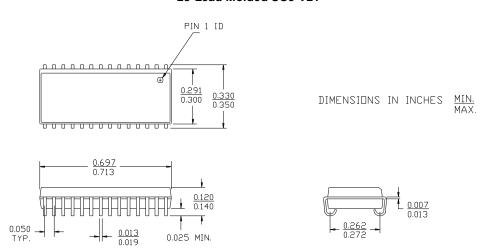

### 28-Lead Molded SOJ V21

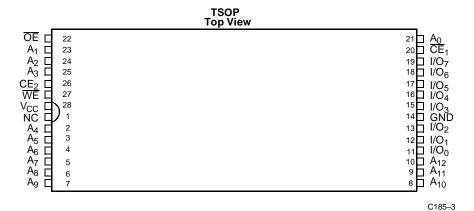

### Package Diagrams (continued)

### 28-Lead Thin Small outline Package Z28