# MC14LC5447

# **Product Preview**

# **Calling Line Identification (CLID) Receiver with Ring Detector**

The MC14LC5447 is a silicon gate HCMOS IC designed to demodulate Bell 202 and V.23 1200-baud FSK asynchronous data. The primary application for this device is in products that will be used to receive and display the calling number, or message waiting indicator sent to subscribers from participating central office facilities of the public switched network. The device also contains a carrier detect circuit and ring detector which may be used to power up the device.

Applications for this device include adjunct boxes, answering machines, feature phones, fax machines, and computer interface products.

The MC14LC5447 offers the following performance features.

- Ring Detector On–Chip

- Ring Detect Output for MCU Interrupt

- Power–Down Mode, Less than 1 μA

- Single Supply: + 3.5 to + 6.0 V

- Pin Selectable Clock Frequencies: 3.68 MHz, 3.58 MHz, or 455 kHz

- Two Stage Power–Up for Power Management Control

- Demodulates Bell 202 and V.23

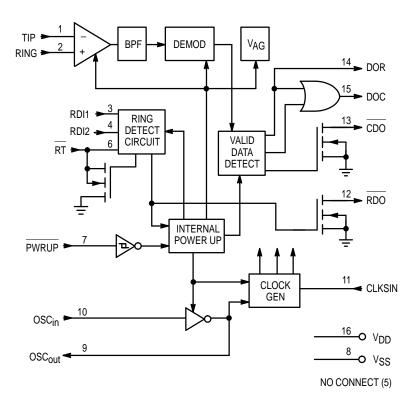

#### **BLOCK DIAGRAM**

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

REV 0 7/96

**ORDERING INFORMATION** MC14LC5447P Plastic DIP MC14LC5447DW

SOG Package

| PIN ASSIGNMENT      |      |                     |  |  |  |

|---------------------|------|---------------------|--|--|--|

| ті 🛛 1              | • 16 | VDD                 |  |  |  |

| RI 🛛 2              | 15   | DOC                 |  |  |  |

| RDI1 🛛 3            | 14   | ] dor               |  |  |  |

| RDI2 🛛 4            | 13   |                     |  |  |  |

|                     | 12   | RDO                 |  |  |  |

| RT 🛛 6              | 11   | CLKSIN              |  |  |  |

| PWRUP [ 7           | 10   | ] osc <sub>in</sub> |  |  |  |

| ∨ <sub>SS</sub> [ 8 | 9    | osc <sub>out</sub>  |  |  |  |

| NC = NO CONNECTION  |      |                     |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND, except where noted)

| Rating                      | Symbol           | Value                          | Unit |

|-----------------------------|------------------|--------------------------------|------|

| DC Supply Voltage           | V <sub>DD</sub>  | – 0.5 to + 6.0                 | V    |

| Input Voltage, All Pins     | V <sub>in</sub>  | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Current Drain Per Pin    | I                | ± 10                           | mA   |

| Power Dissipation           | PD               | 20                             | mW   |

| Operating Temperature Range | TA               | 0 to + 70                      | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | – 40 to + 150                  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub>  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  V<sub>DD</sub>.

Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

#### **ELECTRICAL CHARACTERISTICS**

(All polarities referenced to V\_SS = 0 V, V\_DD = + 5 V  $\pm$  10%, unless otherwise noted, T\_A = 0 to + 70°C)

| Parameter                                                                                                                                              |                                | Min                   | Тур  | Max                   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|------|-----------------------|------|

| DC Supply Voltage                                                                                                                                      | V <sub>DD</sub>                | 3.5                   | 5    | 6                     | V    |

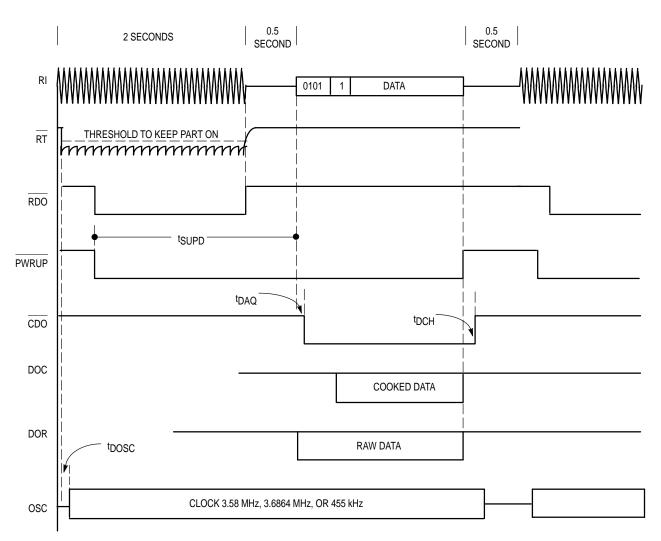

| Supply Cu <u>rrent (All</u> Output Pins Unloaded) (See Figure 1)<br>RT = 0, PWRUP = 1, XTAL = 3.58 MHz                                                 | IDD                            | -                     | 2.4  | 3                     | mA   |

| Supply Current (All Output Pins Unloaded) (See Figure 1)<br>PWRUP = 0, RT = Don't Care, XTAL = 3.58 MHz                                                | IDD                            | -                     | 4.0  | 5.5                   | mA   |

| St <u>and</u> by C <u>urrent (</u> All Output Pins Unloaded) (See Figure 1)<br>RT = 1, PWRUP = 1                                                       | ISTBY                          | -                     | _    | 1                     | μA   |

| Input Voltage 0 Level (CLKSIN, OSC <sub>in</sub> )                                                                                                     | VIL                            | —                     | _    | V <sub>DD</sub> x 0.3 | V    |

| Input Voltage 1 Level (CLKSIN, OSCin)                                                                                                                  | VIH                            | V <sub>DD</sub> x 0.7 | —    | —                     | V    |

| Output Voltage High: V_DD = 5 V (DOR, DOC, OSC_out)<br>$I_{OH}$ = 40 $\mu A$ $I_{OH}$ $\leq$ 1 $\mu A$                                                 | VOH                            | 2.4<br>4.95           | _    | -                     | V    |

| Output Voltage Low: V_DD = 5 V (DOR, DOC, OSC_out) $\label{eq:OL} \begin{array}{l} I_{OL} = 1.6 \text{ mA} \\ I_{OL} \leq 1 \ \mu\text{A} \end{array}$ | V <sub>OL</sub>                | -                     | _    | 0.4<br>0.05           | V    |

| Input Leakage Current (OSCin, CLKSIN, PWRUP, RT, RDI1, and RDI2)                                                                                       | l <sub>in</sub>                | _                     | _    | ±1                    | μΑ   |

| Output Voltage Low: V <sub>DD</sub> = 5 V (RDO, RT, CDO) I <sub>OL</sub> = 2.0 mA                                                                      | VOL                            | _                     | _    | 0.4                   | V    |

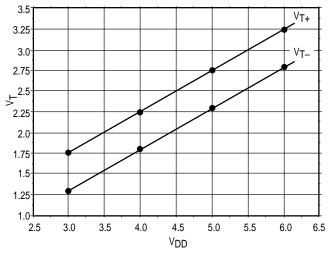

| Input Thr <u>eshold Volta</u> ge Positive Going: V <sub>DD</sub> = 5 V<br>(RDI1, RT, PWRUP) (See Figure 3)                                             | V <sub>T+</sub>                | 2.5                   | 2.75 | 3.0                   | V    |

| Input Thr <u>eshold Volta</u> ge Negative Going: V <sub>DD</sub> = 5 V<br>(RDI1, RT, PWRUP) (See Figure 3)                                             | V <sub>T-</sub>                | 2.0                   | 2.3  | 2.6                   | V    |

| RDI2 Threshold                                                                                                                                         | R <sub>D2</sub> V <sub>T</sub> | 1.0                   | 1.1  | 1.2                   | V    |

| TIP/RING Input dc Resistance                                                                                                                           | R <sub>in</sub>                | _                     | 250  | _                     | kΩ   |

# ANALOG CHARACTERISTICS (V<sub>DD</sub> = + 5 V, T<sub>A</sub> = + 25°C, unless otherwise noted, 0 dBm = 0.7746 Vrms @ 600 $\Omega$ )

| Characteristic                                                             |                                         | Min  | Тур                        | Max  | Unit |

|----------------------------------------------------------------------------|-----------------------------------------|------|----------------------------|------|------|

| Input Sensitivity: TIP and RING (Pins 1 and 2, $V_{DD}$ = + 5 V)           |                                         | - 40 | - 45                       | —    | dBm  |

| Band–Pass Filter (BPF)<br>Frequency Response (Relative to 1700 Hz @ 0 dBm) | 60 Hz<br>500 Hz<br>2700 Hz<br>≥ 3300 Hz |      | - 64<br>- 4<br>- 3<br>- 34 | <br> | dB   |

| Carrier Detect Sensitivity                                                 | 2 3300 HZ                               |      | - 48                       |      | dBm  |

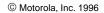

## SWITCHING CHARACTERISTICS (V<sub>DD</sub> = + 5 V, C<sub>L</sub> = 50 pF, T<sub>A</sub> = + 25°C)

| Description                              |                   | Min | Тур | Max | Unit |

|------------------------------------------|-------------------|-----|-----|-----|------|

| OSC Startup (CLKSIN = 1; 3.579 MHz XTAL) | <sup>t</sup> DOSC | _   | 2   | _   | ms   |

| Power–Up Low to FSK (Setup Time)         | <sup>t</sup> SUPD | 15  |     | —   | ms   |

| Carrier Detect Acquisition Time          | <sup>t</sup> DAQ  | —   | 14  | —   | ms   |

| End of Data to Carrier Detect High       | <sup>t</sup> DCH  | 8   | _   | —   | ms   |

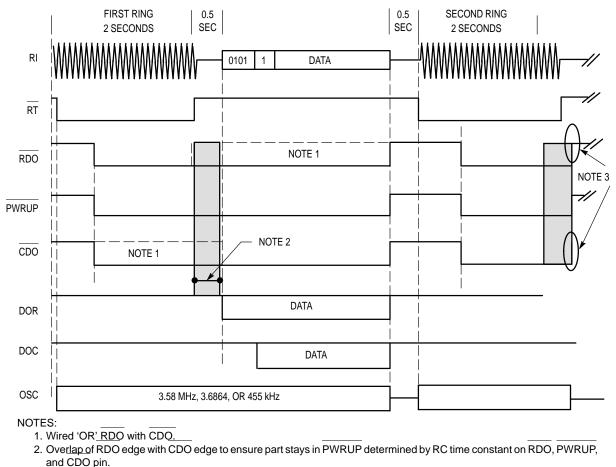

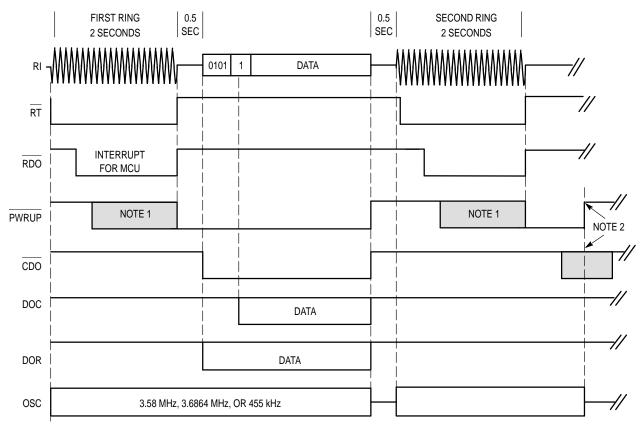

# TIMING DIAGRAM

Figure 1. IDD Test Circuit

#### **PIN DESCRIPTIONS**

#### ТΙ

### Tip Input (Pin 1)

This input pin is normally connected to the tip side of the twisted pair. It is internally biased to 1/2 supply voltage when the device is in the power–up mode. This pin must be dc isolated from the line.

### RI

#### **Ring Input (Pin 2)**

This input is normally connected to the ring side of the twisted pair. It is internally biased to 1/2 supply voltage when the device is in the power–up mode. This pin must be dc isolated from the line.

## RDI1

#### Ring Detect Input 1 (Pin 3)

This input is normally coupled to one of the twisted pair wires through an attenuating network. It detects energy on the line and enables the oscillator and precision ring detection circuitry.

#### RDI2

#### Ring Detect Input 2 (Pin 4)

This input to the precision ring detection circuit is normally coupled to one of the twisted pair wires through an attenuating network. A valid ring signal as determined from this input sends the RDO (Pin 12) to a logic 0.

## RT

## Ring Time (Pin 6)

An RC network may be connected to this pin. The RC time constant is chosen to hold this pin voltage below 2.2 V between the peaks of the ringing signal. RT is an internal power–up control and activates only the circuitry necessary to determine if the incoming ring is valid.

## PWRUP

#### Power Up (Pin 7)

A logic 0 on the PWRUP input causes the device to be in the active mode ready to demodulate incoming data. A

logic 1 on this pin causes the device to be in the standby mode, if the RT input pin is at a logic 1. This pin may be controlled by RDO and CDO for auto power–up operation. For other applications, this pin may be controlled externally.

# Vss

### Ground (Pin 8)

Ground return pin is typically connected to the system ground.

# OSCout

### Oscillator Output (Pin 9)

This pin will have either a crystal or a ceramic resonator tied to it with the other end connected to OSC<sub>in</sub>.

# OSC<sub>in</sub>

#### **Oscillator Input (Pin 10)**

This pin will have either a crystal or a ceramic resonator tied to it with the other end connected to  $OSC_{out}$ .  $OSC_{in}$  may also be driven directly from an appropriate external source.

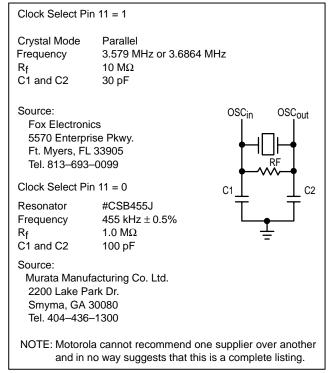

#### CLKSIN

#### **Clock Select Input (Pin 11)**

A logic 1 on this input configures the device to accept either a 3.579 MHz or 3.6864 MHz crystal. A logic 0 on this pin configures the part to operate with a 455 kHz resonator.

For crystal and resonator specifications see Table 1.

# RDO

#### **Ring Detect Out (Pin 12)**

This open–drain<u>output</u> goes low when a valid ringing signal is detected. RDO remains low as long as the ringing signal remains valid. This signal can be used for auto power– up, when connected to Pin 7.

## CDO

#### Carrier Detect Output (Pin 13)

When low, this open drain <u>output</u> indicates that a valid carrier is present on the line. CDO remains low as long as the carrier remains valid. An 8 ms hysteresis is <u>b</u>uilt in to allow for a momentary drop out of the carrier. CDO may be <u>used in the auto power-up configuration when connected to PWRUP.</u>

#### DOR Data Out Raw (Pin 14)

<u>This</u> pin presents the output of the demodulator whenever CDO is low. This data stream includes the alternate 1 and 0 pattern, and the 150 ms of marking, which precedes the data. At all other times, DOR is held high.

#### DOC

#### Data Out Cooked (Pin 15)

This output presents the output of the demodulator whenever CDO is low, and when an internal validation sequence has been successfully passed. The output does not include the alternate 1 and 0 pattern. At all other times, DOC is held high.

#### V<sub>DD</sub>

#### Positive Power Supply (Pin 16)

The digital supply pin, which is connected to the positive side of the power supply.

### **APPLICATIONS INFORMATION**

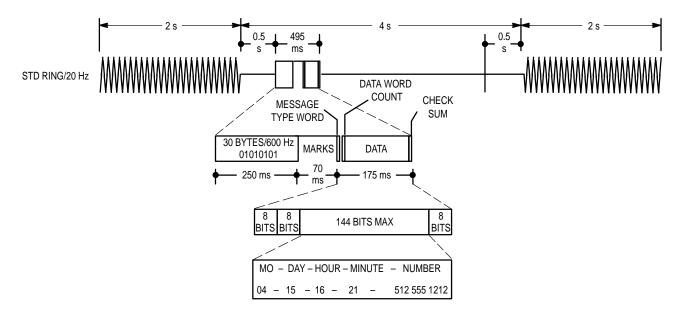

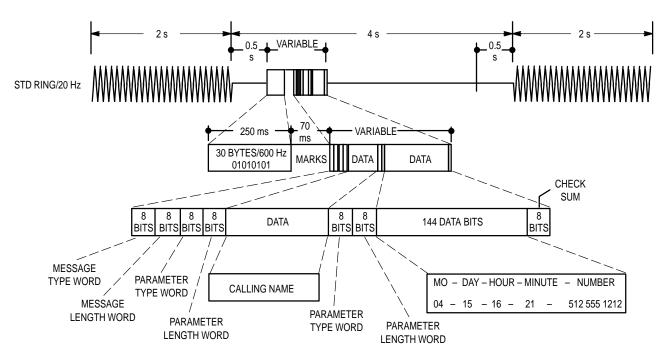

The MC14LC5447 has been designed to be one of the main functional blocks in products targeted for the CLASS (Custom Local Area Signaling Service) market. CLASS is a set of subscriber features now being presented to the consumer by the RBOCs (Regional Bell Operating Companies) and independent TELCOs. Among CLASS features, such as distinctive ringing and selective call forwarding, the subscriber will also have available a service known as Calling Number Delivery (CND) and message waiting. With these services, a subscriber will have the ability to display at a minimum, a message containing the phone number of the calling party, the date, and the time. A message containing only this information is known as a single format message, as shown in Figure 9. An extended message, known as multiple format message, can contain additional information as shown in Figure 10.

The interface should be arranged to allow simplex data transmission from the terminating central office, to the CPE (Customer Premises Equipment), only when the CPE is in an on-hook state. The data will be transmitted in the silent period between the first and second power ring after a voice path has been established.

The data signaling interface should conform to Bell 202, which is described as follows:

- Analog, phase coherent, frequency shift keying

- Logical 1 (Mark) = 1200 ± 12 Hz

- Logical 0 (Space) = 2200 ± 22 Hz

- Transmission rate = 1200 bps

- Application of data = serial, binary, asynchronous

The transmission level from the terminating C.O. will be -13.5 dBm  $\pm 1.0$ . The expected worst case attenuation through the loop is expected to be -20 dB. The receiver therefore, should have a sensitivity of approximately -34.5 dBm to handle the worst case installations.

Additional information on CLASS services can be obtained from:

BELLCORE CUSTOMER SVS. 1–800–521–2673 201–699–5800 FOREIGN CALLS 201–699–0936 FAX The document number is: TA–NWT–000030 Title: "Voice Band Data Transmission Interface Generic Requirements"

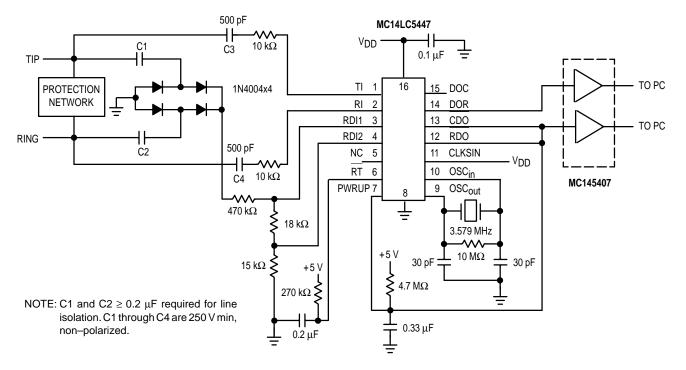

Figure 7 is a conceptual design of how the MC14LC5447 can be implemented into a product which will retrieve the incoming message and convert it to EIA–232 levels for transmission to the serial port of a PC. With this message and appropriate software, the PC can be used to look up the name and any additional information associated with the caller that had been previously stored.

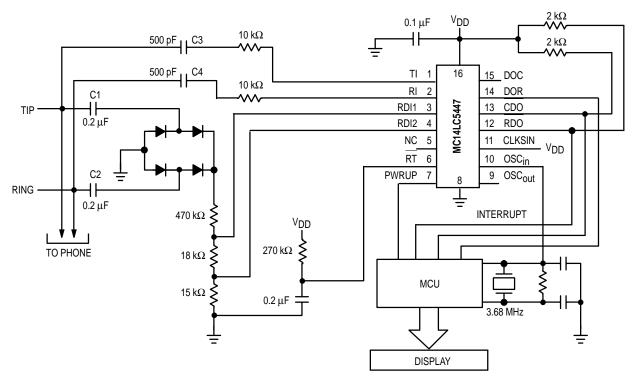

Figure 8 is a conceptual design of an adjunct unit in parallel with an existing phone. This arrangement gives the subscriber CND service without having to replace existing equipment.

#### **Table 1. Oscillator Specifications**

#### **DESIGN INFORMATION**

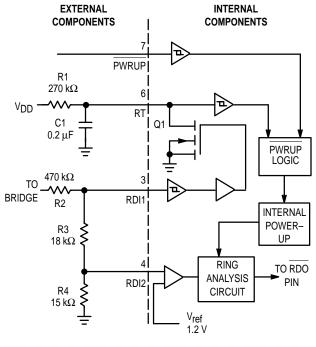

The circuit in Figure 2 illustrates in greater detail the relationship between Pins 3, 4, 6, and 7.

The external component values shown in Figure 2 are the same as those shown in Figures 7 and 8. When V<sub>DD</sub> is applied to the circuit in these two<u>fig</u>ures, the RC network will charge cap C1 to V<sub>DD</sub> holding RT (Pin 6) off. If the PWRUP (Pin 7) is also held at V<sub>DD</sub>, the MC14LC5447 will be in a power–down mode, and will consume 1  $\mu$ A of supply current (max).

The resistor network (R2 – R4) attenuates the incoming power ring applied to the top of R2. The values given have been chosen to provide a sufficient voltage at RDI1 (Pin 3) to turn on the Schmitt-trigger input with approximately a 40 Vrms or greater power ring input from tip and ring. When  $V_{T+}$  of the Schmitt is exceeded, Q1 will be driven to saturation discharging cap C1 on RT. This will initialize a partial power–up, with only the portions of the part involved with the ring signal analysis enabled, including RDI2 (Pin 4). At this time the MC14LC5447 power consumption is increased to approximately 2.4 mA (typ).

Figure 2.

The value of R1 and C1 must be chosen to hold the RT pin voltage below the  $V_{T+}$  of the RT Schmitt between the individual cycles of the power ring. The values shown will work for ring frequencies of 15.3 Hz (min).

With RDI2 now enabled, a portion of the power ring above 1.2 V is fed to the ring analysis circuit. This circuit is a digital integrator which looks at the duty cycle of the incoming signal. When the input to RDI2 is above 1.2 V, the integrator is counting up at an 800 Hz rate. When the input to RDI2 falls below 1.2 V, the integrator counts down at a 400 Hz rate.

Figure 3. VDD versus VT+ and VT-

A ring is qualified when an internal count of binary 48 is reached. The ring is disqualified when the count drops to a binary 32. The number of ring cycles required to qualify the signal will depend on the amplitude of the voltage presented to RDI2. The shortest amount of time needed to do the qualification is approximately 60 ms. The shortest amount of time required for dequalification will be approximately 40 ms.

Once the ring signal is qualified, the RDO pin will be sent low. This can be fed back to PWRUP as shown in Figure 7, or with a pull–up resistor, can be used as an interrupt to an MCU as shown in Figure 8. In either case, once the PWRUP pin is below  $V_{T-}$ , the part will be fully powered up, and ready to receive FSK. During this mode, the device current <u>will</u> increase to approximately 6.2 mA (typ). The state of the RT pin is now a "don't care" as far as the part is concerned. Normally, however, this pin will be allowed to return to  $V_{DD}$ .

After the FSK message has been received, the PWRUP pin can be allowed to return to V<sub>DD</sub> and the part will return to the standby mode, consuming less than 1  $\mu$ A of supply current. The part is now ready to repeat the same sequence for the next incoming message.

#### TYPICAL DEMODULATOR PERFORMANCE

The following describes the performance of the MC14LC5447 demodulator in the presence of noise over a simulated Bell 3002 telephone loop.

The Bell 3002 loop represents a worst case local telephone loop in North America. The characteristics of this loop, which affect performance, are high frequency attenuation and Envelope Delay Distortion (EDD) or group delay.

The minimum receiver sensitivity of the MC14LC5447 under these conditions is typically – 45 dBm.

The MC14LC5447 achieves a Bit Error Rate (BER) of  $1 \times 10^{-5}$  at a Signal-to-Noise Ratio (SNR) of 15 dB in V.23 operation and at an SNR of 18 dB in Bell 202 operation (see Figures 4 and 5).

All measurements in dBm are referenced to 600  $\Omega$ : 0 dBm = 0.7746 Vrms.

All measurements were taken using the MC145460EVK evaluation board.

Electronic file not available for this figure. To view the complete document, order it from the Literature Center.

# Figure 4. MC14LC5447 V.23 Operation (Typical BER vs SNR)

Electronic file not available for this figure. To view the complete document, order it from the Literature Center.

# Figure 5. MC14LC5447 Bell 202 Operation (Typical BER vs SNR)

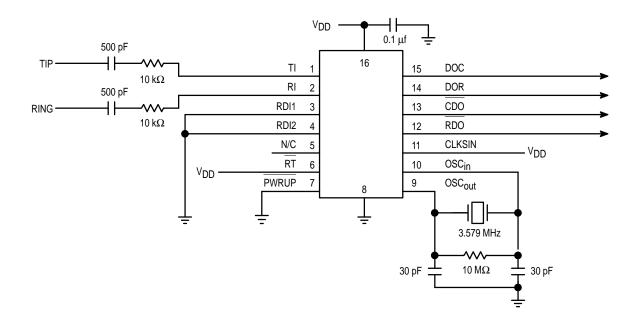

Figure 6. Full-Time Power without Ring Detect

## **APPLICATION CIRCUIT**

Figure 7. Partial Implementation of PC Interface to Tip and Ring

3. Part reverts to PWR ON, on rising edge of RDO since there is no CDO.

Timing Diagram for Figure 7

# **APPLICATION CIRCUIT**

Figure 8. Adjunct Box Concept for Calling Number Display

NOTES:

1. MCU must assert PWRUP to MC14LC5447.

2. No data detected, MCU powers down the MC14LC5447.

**Timing Diagram for Figure 8**

Figure 9. Single Message Format

Figure 10. Multiple Message Format

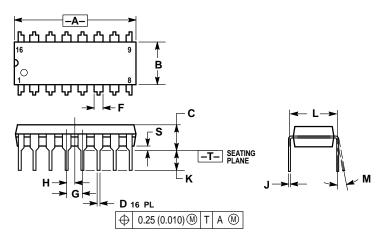

P SUFFIX PLASTIC DIP CASE 648-08

NOTES:

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL. 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH. 5. ROUNDED CORNERS OPTIONAL.

|     | INCHES    |       | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.740     | 0.770 | 18.80    | 19.55  |

| В   | 0.250     | 0.270 | 6.35     | 6.85   |

| С   | 0.145     | 0.175 | 3.69     | 4.44   |

| D   | 0.015     | 0.021 | 0.39     | 0.53   |

| F   | 0.040     | 0.70  | 1.02     | 1.77   |

| G   | 0.100 BSC |       | 2.54 BSC |        |

| Н   | 0.050 BSC |       | 1.27 BSC |        |

| J   | 0.008     | 0.015 | 0.21     | 0.38   |

| Κ   | 0.110     | 0.130 | 2.80     | 3.30   |

| L   | 0.295     | 0.305 | 7.50     | 7.74   |

| М   | 0°        | 10 °  | 0°       | 10 °   |

| S   | 0.020     | 0.040 | 0.51     | 1.01   |

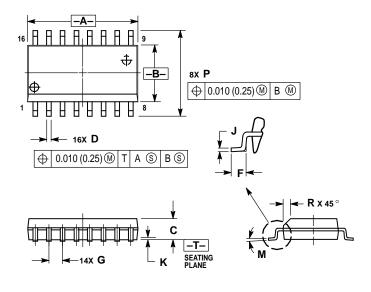

**DW SUFFIX** SOG PACKAGE CASE 751G-02

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE MOLD DOCTOLISION

PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER

Minamoni Mole Frights to the local and loca EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INC       | HES   |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 10.15       | 10.45 | 0.400     | 0.411 |

| В   | 7.40        | 7.60  | 0.292     | 0.299 |

| С   | 2.35        | 2.65  | 0.093     | 0.104 |

| D   | 0.35        | 0.49  | 0.014     | 0.019 |

| F   | 0.50        | 0.90  | 0.020     | 0.035 |

| G   | 1.27        | BSC   | 0.050 BSC |       |

| J   | 0.25        | 0.32  | 0.010     | 0.012 |

| ĸ   | 0.10        | 0.25  | 0.004     | 0.009 |

| М   | 0 °         | 7 °   | 0 °       | 7 °   |

| Р   | 10.05       | 10.55 | 0.395     | 0.415 |

| R   | 0.25        | 0.75  | 0.010     | 0.029 |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(A)** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

$\Diamond$

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design-NET.com JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

INTERNET: http://Design-NET.com

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298